Fターム[5J106FF06]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 入力回路 (135)

Fターム[5J106FF06]に分類される特許

1 - 20 / 135

高安定発振器

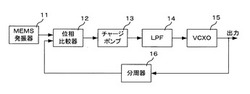

【課題】小型化が容易であり、低コストで製造可能であって、発振出力周波数における短期安定度と長期安定度とを両立させた高安定発振器を提供する。

【解決手段】一定の周波数の信号を出力する高安定発振器は、出力発振器として電圧制御型水晶発振器15を備えるPLL回路と、MEMS振動子を有するMEMS発振器11と、を備える。MEMS発振器11の出力を基準信号としてPLL回路の位相比較器12に供給する。MEMS発振器11によって出力周波数の長期安定度が維持され、電圧制御型水晶発振器15によって出力周波数の短期安定度が維持されるようにする。

(もっと読む)

発振器

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

発振装置

【課題】水晶振動子の動作時間の経過に伴う発振周波数の変化を補償して安定した発振周波数が得られる発振装置を提供すること。

【解決手段】基準時から所定の時間が経過した後における第1及び第2の水晶振動子の周波数差と、基準時における第1及び第2の水晶振動子の周波数差と、の差分値ΔF(即ち、第1の水晶振動子における周波数について基準時からの変化分と、第2の水晶振動子における周波数について基準時からの変化分との差分値ΔF)を求める。そして基準時からの時間の経過に対して、第1の水晶振動子の周波数の変化分と第2の水晶振動子の周波数の変化分との比率が同じであるとして取り扱ったときの当該比率を経時変化の補正係数とし、差分値ΔFに対応する値と経時変化の補正係数とに基づいて、発振装置の出力を作り出すための水晶振動子の周波数について補正値を取得する。

(もっと読む)

同期信号生成装置および同期信号生成方法

【課題】ホールドオーバー状態からGPSロック状態に復帰する際の基地局の状態に応じて、内部パルスおよび内部周波数信号をGPS基準パルスに同期させた状態に復帰させることができる同期信号生成装置および同期信号生成方法を提供することである。

【解決手段】本発明に係る基地局3にパルスを提供する同期信号生成装置は、GPS衛星から受信した信号からGPS基準パルスを生成するGPS受信器11と、内部周波数信号を生成する発振器15と、内部周波数信号を分周して内部パルスを生成する分周器12と、GPS基準パルスと内部パルスとを比較して前記内部パルスを前記GPS基準パルスに同期させる同期部14と、基地局3の状態に応じて、ホールドオーバー状態からGPSロック状態に復帰するときの、同期部14のループタイムを決定する制御部13と、を備える。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

フェーズロックドループの方法及び装置

【課題】2点変調を採用するフェーズロックドループを用いた通信システムを提供する。

【解決手段】フェーズロックドループは、位相検出器106の第1の入力に動作可能に接続された出力を有する主発振器100、位相検出器106の第2の入力に動作可能に接続された出力を有する従発振器102、及び位相検出器106の生誤り端末に動作可能に接続されたフォワード利得適応モジュールを含む。フォワード利得適応モジュールは、位相検出器106の生誤り端末と動作可能に接続された、フォワード利得適応モジュールの可変利得増幅器200と、前記フォワード利得適応モジュールの可変利得増幅器200と前記従発振器102とに動作可能に接続された、フォワード利得適応モジュールの積分器202とを具備する。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

PLL回路

【課題】出力クロック信号のロングタームジッタを抑制するPLL回路を提供する。

【解決手段】位相比較器、チャージポンプ回路、ループフィルタ、及び電圧制御発振器を有するPLL回路において、基準クロック信号と帰還クロック信号との位相差が所定の閾値より大きい場合には、位相差の単位量当たりに対する変化を小さくして位相差に応じた出力電流を出力し、位相差が所定の閾値以下である場合には、位相差の単位量当たりに対する変化を大きくして位相差に応じた出力電流を出力するようにして、ロック後のループ帯域を広げることができるようにする。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

同期装置および同期方法

【課題】同期源からの信号を捕捉できない状態になっても、可能な限り同期を維持することができる同期装置および同期方法を提供する。

【解決手段】選択部20は、内蔵GPSユニット2からの第1の基準信号およびGPSユニット3からの第2の基準信号のいずれかを選択する。PLL回路6は、選択部20で選択された基準信号に同期した同期信号を生成して内部の回路へ供給する。、内蔵GPSユニット2のホールドオーバー時間は、GPSユニット3のホールドオーバー時間よりも短い。選択部20は、GPSユニット3がホールドオーバー可能な状態となった後は、GPSユニット3を選択する。

(もっと読む)

1 - 20 / 135

[ Back to top ]