Fターム[5J106RR01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 入力回路(固定分周器以外) (47)

Fターム[5J106RR01]に分類される特許

1 - 20 / 47

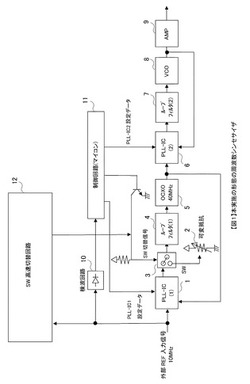

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

周波数シンセサイザ

【課題】 電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供する。

【解決手段】 基準信号発生回路1に、OCXO20と、TCXO30と、それぞれの出力に対してウェイト調整を行うウェイト変換器21,31と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器41を備え、CPU10が、電源投入時にはTCXO30のウェイトを100%、OCXO20のウェイトを0%とし、徐々にOCXO20のウェイトを上げて、予め設定された一定時間後にTCXO30のウェイトを0%、OCXO20のウェイトを100%とするようにウェイト変換器B,Cを制御する周波数シンセサイザとしており、電源投入後に急速に周波数を安定させることができるものである。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

位相同期回路及び位相同期方法

【課題】低品質の入力光信号に対しても、安定して同期信号を発生するとともに、入力光信号が有するクロック信号に対する位相誤差検出感度を高くし、同期信号のタイミングジッタを低減し、製造コストを削減することである。

【解決手段】位相同期回路10は、基準信号を発生する基準信号発生部22と、入力光信号と電気信号とを位相比較して第1の位相誤差信号を生成する光位相比較部1と、第1の位相誤差信号と、基準信号と、を位相比較して第2の位相誤差信号を生成し、第2の位相誤差信号における入力光信号のクロック信号周波数に対応する周波数成分のみに応じて入力光信号の位相に同期した出力信号を発生して出力する位相同期部2と、基準信号の分周信号を用いて、位相同期部2から出力された同期信号をSSB変調して電気信号として光位相比較部1に出力する変調部3と、を備える。

(もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

搬送波生成回路

【課題】広帯域にわたって周波数成分の劣化がない搬送波を生成する搬送波生成回路を提供する。

【解決手段】指定された搬送波の周波数に応じて設定を変更する機能を設け、スプリアスが発生しない設定値に切り替える。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

シンセサイザと、これを用いた受信装置、および電子機器

【課題】精度の高い発振周波数を生み出す事ができるシンセサイザを提供する事を目的とする。

【解決手段】シンセサイザ1は、基準発振器2からの基準発振信号が入力される比較器4と、比較器4の出力信号に基づいて発振信号を出力する電圧制御発振器5と、この電圧制御発振器5の出力信号を制御部7からの制御信号に基づいて分周する第2分周器6とを備えており、比較器4は、第2分周器6からの出力信号と基準発振器2からの出力信号とを比較してこの比較結果を示す信号を電圧制御発振器5に出力し、シンセサイザ1を用いる電子機器の使用状態に基づいて、第2分周器6の分周比の値が決められている。これにより、温度検出部8とMEMS振動子11との間の温度差に起因したシンセサイザの発振周波数誤差を無くす事ができる。

(もっと読む)

基準クロック信号生成装置

【課題】

デジタル映像信号処理で必要となる所定周波数の基準クロック信号を得る手法として、ジッター発生要因を有する手法を用いた場合でも、このジッターに起因する画質劣化や音質劣化を出来る限り目立たなくすることを可能とする装置を提供する。

【解決手段】

映像信号や音声信号の信号レベルが低い期間か否かを検出し、信号レベルが低くない期間は、クロック信号を生成するPLL回路の構成要素である帰還分周器5の分周比率を固定値とし、信号レベルが低い期間は、帰還分周器5の分周比率を可変して、これら各期間よりも十分に長い期間で積分すると、全体的にみれば所定周波数となる基準クロック信号を生成する。

(もっと読む)

シンセサイザまたは発振器モジュールと、このシンセサイザを用いたシンセサイザモジュール、受信装置、及び電子機器、ならびに分周器の分周比の制御方法

【課題】制御部による分周器の制御に起因したノイズの発生を抑え、受信特性の良好な受信機を実現可能なシンセサイザを提供することを目的とする。

【解決手段】制御部7は、温度を検出する温度検出部8の出力信号に基づいて第2の分周器6へ適当な整数分周数Mや分数分周数Nの制御信号を送り、第2の分周器6の分周比を変化させる。つまり、第2の分周器6は、分周数Mが入力される整数部分と、分周数Nが入力される分数部分により構成される。制御部7は、温度を検出する温度検出部8の温度信号に基づいて第2分周器6の分周比を不均一な時間間隔で変化させる。これにより、第2分周器6の制御に伴い特定周波数に多数発生するノイズを抑圧することができ、シンセサイザの位相雑音を低減することができる。

(もっと読む)

ADPLL周波数シンセサイザ

【課題】DCO利得正規化回路を用いることなく制御感度を適切に推定することで、デジタル制御発振器の発振周波数が変化しても位相雑音特性が変化しないADPLL周波数シンセサイザを提供する。

【解決手段】周波数設定ワードがFCW0からFCW2へ変更される場合、制御感度推定部12は、ダミーであるFCW1である時の発振周波数f1をまず測定し、次にFCW2である時の発振周波数f2を測定する。そして、制御感度推定部12は、発振周波数f1及びf2の値からFCW2時の制御感度KDCO2を計算する。ループフィルタ13は、制御感度KDCO2の値に基づいて、予め設計した固有周波数ωn及びダンピングファクタζとなるように、フィルタ係数α2及びρ2の値を決定する。

(もっと読む)

1 - 20 / 47

[ Back to top ]