Fターム[5J106KK00]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441)

Fターム[5J106KK00]の下位に属するFターム

性能の向上 (885)

信頼性の向上 (1,507)

経時変化防止、校正 (43)

調整、設定、試験 (111)

間欠動作 (21)

現用予備 (33)

相互同期 (18)

生産性の向上 (36)

IC化,LSI化 (197)

小型化 (224)

簡素化 (146)

省電力化 (216)

Fターム[5J106KK00]に分類される特許

1 - 4 / 4

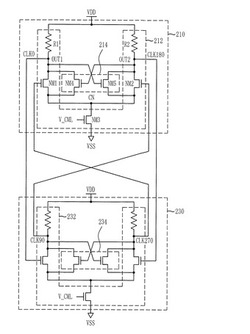

リング発振器及びこれを用いるマルチ位相クロック補正回路

【課題】クロスカップル構造を有する複数のバッファを備えて発振し、CMLレベルのクロック信号を生成することのできるリング発振器を提供し、また、基準位相クロック信号を補正して希望の周波数、及び互いに予め定められた位相差を有するマルチ位相クロック信号を生成することのできるマルチ位相クロック補正回路を提供する。

【解決手段】 本発明のリング発振器は、各々クロスカップル構造を有し、予め定められた電圧レベルのバイアス電圧が印加されて複数のクロック信号を生成するための複数のバッファ手段を備え、前記複数のクロック信号が、前記バイアス電圧に対応するスイング幅を有する。

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

【課題】制御信号だけではなく、周波数も制御可能な変調機能を有する発振器、及びその発振器を用いた位相同期ループ回路を提供する。

【解決手段】出力信号の帰還信号と基準信号との位相を比較して、位相差を示す信号を出力する位相検出器1081と、位相検出器1081の出力信号が供給され、位相差をなくすための制御信号を出力するループフィルタ1082と、ループフィルタ1082からの制御信号に基づく周波数で発振する発振器1083とを備え、発振器1083は、制御信号に変調信号を加えることによって周波数を変調する変調手段を備える位相同期ループ回路(PLL回路)。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】より容易に広い制御電位の範囲にわたって発振周波数の線形性が高い電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路、n個の可変容量回路、及び負性抵抗回路と、電源電位からn個の基準電位を生成する基準電位発生部114とを備える。n個の可変容量回路の可変容量素子の一方端子には、n個の基準電位のいずれかがそれぞれ入力される。n個の可変容量回路の可変容量素子の他方端子には、発振周波数をフィードバック制御するための制御電位Vtが共通入力される。そして、第1〜第3の可変容量回路A〜Cの一方端子には、第1〜第3の基準電位Vref1〜3がそれぞれ入力される。この第1〜第3の基準電位Vref1〜3はそれぞれ固定で、かつ、第1の基準電位Vref1と第2の基準電位Vref2の電位差と、第2の基準電位Vref2と第3の基準電位Vref3との電位差が異なっている。

(もっと読む)

位相同期ループ回路及びこの位相同期ループ回路の制御方法

【課題】電圧制御水晶発振器の経年変化による異常が発生しても、この異常を確実に検出できるようにした位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号W1を生成し、カウンタ115にて内部クロック信号から電圧制御水晶発振器12の異常を検出するために必要なウインドウ信号W2を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号W1,W2のハイレベル期間内に入っているか否かを判定し、ウインドウ信号W1のハイレベル期間に入っていて、ウインドウ信号W2のハイレベル期間内に入っていない場合に、電圧制御水晶発振器12の異常と判定するようにしている。

(もっと読む)

1 - 4 / 4

[ Back to top ]