Fターム[5J106KK34]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 現用予備 (33)

Fターム[5J106KK34]に分類される特許

1 - 20 / 33

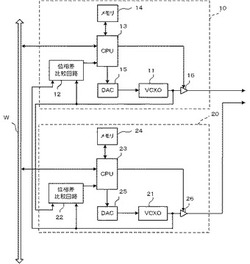

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

クロック供給装置

【課題】入力クロックの周波数がジッタやワンダ等により時間的に変動する場合においても、入力クロックの不具合の状態を的確に判定することができようにし、適切な保守が可能となる、クロック供給装置を提供する。

【解決手段】本発明のクロック供給装置においては、N系クロック受信部22とN系MTIE計測部31との間に設置されるワンダ・ジッタ除去フィルタ41と、E系クロック受信部23とE系MTIE計測部32との間に設置されるワンダ除去フィルタ42と、を有して構成される。そして、発振器部26が有するローパスフィルタ特性のカットオフ周波数と、ワンダ除去フィルタ41,42の有するローパスフィルタ特性のカットオフ周波数とが一致あるいは略等しいように構成される。

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

同期信号生成装置及び同期信号生成方法

【課題】コストの増大を抑止しつつ、障害発生時にも複数装置間の同期を障害回復まで維持することを可能とすること。

【解決手段】同期信号生成装置であって、他の装置との間で同期をとるための信号を受信し、受信された信号に基づいて第一同期用信号を出力する受信部と、第一同期用信号と所定のずれを生じながら第二同期信号を出力する発振部と、第一同期用信号と第二同期用信号とのずれを予め記憶する記憶部と、受信部が信号を受信している場合には第一同期信号に基づいて同期信号を出力し、受信部が信号を受信していない場合には第二同期信号及び記憶部に記憶されるずれに基づいてずれを補正することにより同期信号を出力する同期信号生成部と、を備える。

(もっと読む)

衛星ナビゲーションシステムのためのマスタークロック生成装置

【課題】低廉な製作コスト及び部品コストで製造することができ、更に、マスタータイミング基準信号をより高精度で生成することのできる衛星ナビゲーションシステムのためのマスタークロック生成装置の提供。

【解決手段】複数の周波数信号入力部の各々に、原子時計信号から成る第1参照周波数信号と、原子時計信号から成る第2参照周波数信号との、いずれか一方を供給する。複数の周波数コンバータ(110、115、120、125)は、互いに同一周波数の中間周波数信号を出力する。スイッチングマトリクス130は、前記中間周波数信号のうちの1つを主クロックとして選択して送出すると共に、別の1つを副クロックとして選択して送出する。周波数信号生成器150は、前記主クロックから基準周波数信号を生成し、複数の周波数信号出力部へ送出する。位相メーター170は、前記主クロックと前記副クロックとの間の位相差を測定し、異常挙動を検出する。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

基準周波数発生システム及び基準周波数発生装置

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のGPS受信機21aからケーブル101を介して出力された1PPS信号がPLL回路22bに供給される。予備側に入力された1PPS信号は、ケーブル101と遅延量が等しいケーブル102を介して現用側に戻される。現用側の基準周波数発生装置51は、自機のGPS受信機21aからの1PPS信号と、予備側に出力して戻された1PPS信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

周波数シンセサイザ

【課題】電圧制御発振部からの周波数信号を分周、A/D変換、直交検波を行い、検波に用いた周波数信号とA/D変換した周波数信号との周波数差で回転する回転ベクトルを取り出し、この回転ベクトルの周波数と設定周波数との差分を積分して電圧制御発振部の制御電圧とする周波数シンセサイザにおいて、PLL制御が正常に動作しない状態を瞬時にあるいは事前に判定できる技術の提供。

【解決手段】電圧制御発振部に入力される制御電圧を監視し、監視された制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断してアンロック検出信号を出力する。回転ベクトルに対して、設定周波数に応じて粗刻みに決められた周波数で逆回転する逆回転ベクトルを乗算して回転ベクトルを減速する構成においては、減速された回転ベクトルの長さ(スカラー量)またはゲイン制御用の補正信号が予め設定した範囲から外れているか否かの判定結果を更に考慮する。

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

冗長構成システムにおける基準信号同期制御方法

【課題】運用系と待機系の位相差を正確に求めることが出来る冗長構成システムにおける基準信号同期制御方法を提供することである。

【解決手段】装置の基準信号を生成し、運用系と待機系の冗長構成を成すユニットにおいて、運用系のハードウェアと、待機系のハードウェアで、同じタイミングの基準信号を用いて装置を動作させるために、運用系から出力する基準信号は、各機能部の他、待機系にも送り、待機系は、運用系から入力される基準信号と自ら生成する基準信号との位相差を、運用系から待機系までの遅延を擬似的に実現させ、そこから求められた遅延量に従い、待機系が生成する基準信号に遅延分のオフセットをかけることで、運用系の基準信号と同期させる。

(もっと読む)

リアルタイムクロック回路のバックアップ電源回路および半導体装置

【課題】二次電池を過充電することなく、負荷回路の正確な消費電流の測定を可能にする。

【解決手段】リアルタイムクロック回路11のバックアップ電源回路20において、主電源Vinにより充電されるバックアップ電源20と、主電源Vinと、リアルタイムクロック回路11の電源端子間に介挿された第1スイッチ手段SW1と、バックアップ電源20と、リアルタイムクロック回路11の電源端子間に介挿された第2スイッチ手段SW2と、主電源Vinの電圧を検出し、該電圧が第1検出電圧以下の場合には第1スイッチ手段SW1をオフする第1電圧検出回路12と、主電源Vinの電圧を検出し、該電圧が第2検出電圧以上の場合には前記第2スイッチ手段SW2をオフする第2電圧検出回路13を備える。

(もっと読む)

同期確立装置および通信装置

【課題】それぞれの発振器を備えた複数の受信部の同期を容易に確立すること。

【解決手段】現用系A受信部140の同期確立部200は、複数の受信部(140、150、160)それぞれに備えられた第一の発振器230によって生成された互いに周波数が異なる複数の波形信号を入力する入力部(210、220、240)と、入力部によって入力された複数の波形信号に対する論理演算により複数の受信部に共通する波形の共通波形信号を算出する算出部250と、算出部250によって算出された共通波形信号から各受信部内部における処理周波数を規定するローカル信号を生成するPLL部260、第二の発振器270および分周器265と、を備える。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

半導体装置

【課題】 クロック信号の高い周波数精度およびシステムの低消費電流を実現することができる半導体装置を実現する。

【解決手段】 本発明の半導体装置は、外付けされる外部発振回路17の発振動作を発振停止信号により制御し、外部発振回路17からの信号を外部クロック信号として出力する制御回路11と、クロック信号を生成し出力する内部発振回路12と、外部クロック信号または内部発振回路12からのクロック信号を切り替え信号に基づいて選択し、内部クロック信号として出力するセレクタ14を有する。

(もっと読む)

位相同期回路

【課題】 セレクタ3によるクロックの切り替え時に、効果的に出力クロックfoの波形の乱れを抑制することは困難であった。

【解決手段】 複数のクロックのいずれかを入力クロックとして選択するセレクタ3と、入力クロックを分周する1/m分周器4と、出力クロックfoを分周する1/n分周器5と、1/m分周器4により分周されたクロックと1/n分周器5により分周されたクロックとの位相差を検出する位相差検出器7と、位相差検出器7により検出されたその位相差に応じて電圧レベルが変動する入力電圧に基づいて出力クロックfoを出力する電圧制御発振器9と、を備え、その入力電圧の電圧レベルが実質的に一定に保持されたうえで、セレクタ3によって入力クロックとして選択されるクロックが変更される。

(もっと読む)

1 - 20 / 33

[ Back to top ]