Fターム[5J106KK01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 性能の向上 (885)

Fターム[5J106KK01]の下位に属するFターム

高速化 (327)

高精度化 (345)

キャプチャーレンジの拡大 (127)

出力歪の低減 (33)

Fターム[5J106KK01]に分類される特許

1 - 20 / 53

圧電薄膜共振子、発振器及び時間標準器

半導体装置及びその制御方法

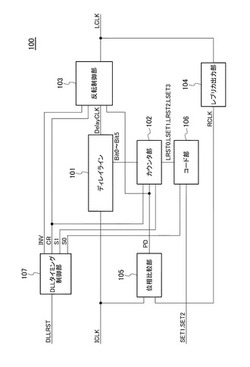

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

量子干渉装置及び量子干渉方法

【課題】アルカリ金属原子に対するEIT現象の発現効率を高めることができる量子干渉装置及び量子干渉方法を提供すること。

【解決手段】光源10は、互いに周波数が異なる複数の第1の光と互いに周波数が異なる複数の第2の光とを発生させてアルカリ金属原子20に照射する。光検出部30は、アルカリ金属原子を透過した光の強度を検出する。制御部40は、光検出部が検出した光の強度に基づいて、第1の光の各々と第2の光の各々との周波数差が2S1/2の第1の基底準位と第2の基底準位とのエネルギー差に相当する周波数にそれぞれ一致するように制御し、かつ、第1の光の各々の波長が2P1/2のいずれかの励起準位又はその近傍の準位と第1の基底準位とのエネルギー差に相当する波長と一致するように制御するとともに、第2の光の各々の波長が当該励起準位又はその近傍の準位と第2の基底準位とのエネルギー差に相当する波長と一致するように制御する。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

通信装置及び周波数シンセサイザ

【課題】使用する周波数帯域で、温度変化による送受信の振幅値の偏差を抑えることができる通信装置を提供すること。

【解決手段】送信信号の信号路に介在して設けられると共に制御電圧の印加により容量が変化する可変容量素子とインダクタンスとを含む共振回路を有し、この共振回路の共振点に応じて高周波の入力信号の振幅を調整する振幅調整回路と、前記信号路が置かれている雰囲気の温度を検出する温度検出部と、一のチャンネルにおける周波数帯域において、送信信号の振幅値が予め設定した値になるようにまたは近づくように、前記振幅調整回路の制御電圧値と温度検出値との関係データを記憶する記憶部と、前記温度検出部の温度検出値と前記関係データとに基づいて振幅調整回路の制御電圧を出力する制御電圧出力部と、を備えるように装置を構成する。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

位相同期ループ回路、半導体集積回路、電子機器、位相同期ループ回路の制御方法

【課題】位相同期ループ回路において、制御応答の改善や消費電力の低減を図る。

【解決手段】発振器制御部255と分周器制御部257は、発振制御信号と分周制御信号が、引込み過程およびロック時の双方において、ループフィルタ電圧に基づいて比例関係を持って連動して変化するようにする。発振部210と分周部220が引込み過程およびロック時の双方において連動した動作をする。引込み過程およびロック時の双方における任意のループフィルタ電圧に対応する分周部220の最高動作周波数が発振部210の発振出力信号の周波数よりも常に高くなるように各制御信号の関係を設定する。ロック時の分周制御信号は、引込み過程における発振部210の発振出力信号の最高周波数と対応するループフィルタ信号に基づくバイアス電流よりも小さなバイアス電流を分周部220に自動的に設定するようになる。このことにより、ロック時の電力消費を低減できる。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

PLL回路及びチャージポンプ回路

【課題】簡単な構成でPLL回路がロック時にオフリーク電流が生じるのを低減することが可能なチャージポンプ回路及びそのチャージポンプ回路を用いたPLL回路を提供することを課題とする。

【解決手段】P型トランジスタMP1及びN型トランジスタMN1と並列に常にオフにしたP型トランジスタMP2及びN型トランジスタMN2を設ける。P型トランジスタMP1とN型トランジスタMN2が共にOFFのときオフリーク電流はP型トランジスタMP2及びN型トランジスタMN2を介して逃げる。また常にオフにしたP型トランジスタMP2及びN型トランジスタMN2の代りに動的にオン/オフを切替えるP型トランジスタやN型トランジスタを設けたり、P型トランジスタMP1及びN型トランジスタMN1のオフ抵抗と同じ抵抗値の抵抗器を設けても良い。

(もっと読む)

量子干渉装置、原子発振器、および磁気センサー

【課題】ドップラー拡がりによる光共鳴波長分布を持つ原子集団に対しEIT現象を効率

よく発生させる原子発振器を提供する。

【解決手段】各共鳴光を出射するLD2と、LD2の中心波長を発生する中心波長発生手

段1と、二つの異なる基底状態のエネルギー差(ΔE12)に相当する周波数の1/2の

周波数を発振する発振器9と、ドップラー拡がりに対して十分小さい周波数を発振する発

振器10と、電気信号によりLD2から出射された共鳴光11に周波数変調を与えるEO

M(電気光学変調素子)3、4と、EOM4により変調された光12の波長により光の吸

収量を変化させる、気体状アルカリ金属(セシウム)原子を封入したガスセル5と、ガス

セル5から透過する光13を検出する光検出器(光検出手段)6と、光検出器6の出力に

基づきガスセル5のEIT状態を検出して出力電圧を制御する周波数制御手段7と、を備

えて構成されている。

(もっと読む)

クロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路

【課題】動作信頼性を向上させるクロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路を提供すること。

【解決手段】受信信号を再生するタイミング情報が重畳された前記受信信号とリカバリクロックとの位相差に基づいて、前記受信信号とリファレンスクロックとの周波数オフセット情報を検知する周波数差検知部34と、前記周波数検知部34が検知した前記周波数オフセット情報に基づいて、前記受信信号と前記リカバリクロックとの位相差を補正する補正部30とを具備する。

(もっと読む)

PLL回路

【課題】位相比較回路と、チャージポンプと、ループフィルタと、電圧制御発振回路とがこの順に接続されてなるPLL回路において、ループ帯域幅に変動が起こっても容易に対応できるPLL回路を提供する。

【解決手段】位相比較回路は、電圧制御発振回路から出力される帰還信号と、外部より入力される基準信号とが接続される2入力を備え、チャージポンプは種々の利得に対応した電流源を備え、基準信号と位相比較回路の出力からPLLがロックしたときのロック信号を出力するPLLロック検出回路と、基準信号をカウントするカウント回路と、ロック信号とカウンタ回路のカウンタ信号からロック時のカウンタ信号をラッチするラッチ回路と、基準信号を入力する前に一定の利得に対応した電流源のコードに設定され、基準信号を入力後ロック信号及びラッチされたカウンタ信号から適切な利得に対応した電流源のコードを選択して出力する選択手段とを備えている。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

DLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法

【課題】本発明は、アップデート条件を緩和させて効率的なアップデートを行い、位相比較感知結果値が不規則に変化しても内部クロックの位相をより正確に制御することができるDLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックとフィードバッククロックの位相を比較感知して位相感知信号を生成する位相感知手段;前記基準クロックに応答して前記位相感知信号が有する第1論理値と第2論理値の個数の差を判別して有効区間信号とアップデート制御信号を生成するアップデート制御装置;及び前記有効区間信号のイネーブル時に前記アップデート制御信号に応答して遅延ラインに付与する遅延値をアップデートするシフトレジスタ;を備える。

(もっと読む)

基準信号発振装置

【課題】使用する無線通信の周波数帯が変更された場合に、基準信号の周波数の精度を容易且つ適切に変更することである。

【解決手段】GPS信号を受信してUTCに同期した時間信号を取得するGPSユニット52と、基準信号を発振する基準信号ユニット40と、基準信号ユニット40により発生された基準信号のパルス数を測定する測定時間、又は基準信号の周波数の精度の操作入力を受け付ける操作ユニット53と、GPSユニット52により取得された前記時間信号に基づいて、操作ユニット53により入力された測定時間、又は前記入力された精度に対応する測定時間をカウントするとともに、当該測定時間内の前記基準信号のパルス数を測定し、正確なパルス数からの前記測定したパルス数の誤差をなくすように基準信号ユニット40が発生する基準信号の周波数を補正する制御ユニット51と、を備える。

(もっと読む)

電圧制御型発振回路及び電圧変換回路

【課題】複雑な定電流源を使用せずに簡単な回路構成で制御電圧がゲートしきい値電圧以下でも制御電流を流すことができる電圧変換回路及び電圧制御型発振回路を提供すること。

【解決手段】電圧−電圧変換回路101は、制御電圧VINをゲート端子に受けるn型MOSトランジスタN110と、基準電圧VRをゲート端子に受けるn型MOSトランジスタN111と、n型MOSトランジスタN110,N111の共通ドレイン端子をドレイン端子に接続し、ソース端子を高電位電源VDDに接続するp型MOSトランジスタP110と、n型MOSトランジスタN110,N111の共通ソース端子と接地GND間に接続される抵抗体R100とを備える。電圧電流変換回路100は、さらに生成された制御電流に対応する動作電流が流されて電流値に応じた周波数で発振するリングオシレータ201と、基準電圧VRを印加するバイアス電圧発生回路301とを備える。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】PLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づき基準信号の位相及び/又は発振周波数を制御するVCXOと、タイミング位相ベクトル信号の位相及び位相差に基づき制御係数を出力する2次PLL回路とを備える。この2次PLL回路は、タイミング位相ベクトル信号に基づき制御係数を発生する制御係数発生回路と、制御計数発生回路からの制御係数につき6dB単位での対数軸上におけるレベル調整を行う第1のレベル調整回路と、第1のレベル調整回路からの制御係数について±6dBレベルの微調整を行う第2のレベル調整回路とを有する。

(もっと読む)

1 - 20 / 53

[ Back to top ]