Fターム[5J106KK02]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 性能の向上 (885) | 高速化 (327)

Fターム[5J106KK02]の下位に属するFターム

同期確立の高速化 (203)

Fターム[5J106KK02]に分類される特許

1 - 20 / 124

PLL回路

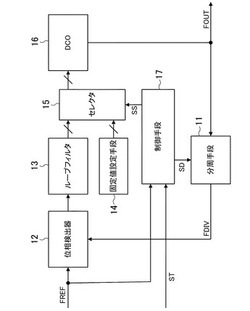

【課題】デジタル制御発振器を用いるPLL回路において高速に引き込みを行う。

【解決手段】PLL回路は、当該PLL回路の出力を分周する分周手段(11)と、基準クロック信号と分周手段(11)の出力信号との位相差を検出する位相検出器(12)と、位相検出器の出力信号をフィルタリングして、当該フィルタリング結果をデジタル値として出力するループフィルタ(13)と、デジタル値と固定値とのいずれか1つを選択するセレクタ(15)と、セレクタ(15)で選択された値に応じた周波数で発振するデジタル制御発振器(16)と、スタート信号を受けるまではセレクタ(15)に対して固定値の選択を指示し、スタート信号を受けてから基準クロック信号のエッジタイミングでセレクタ(15)に対してデジタル値の選択を指示するとともに分周手段(11)に対して出力の開始を指示する制御手段(17)とを備えている。

(もっと読む)

PLL回路およびそのキャリブレーション方法

【課題】1回のキャリブレーションによって電圧制御発振器のフリーラン発振周波数がPLLロックレンジ内に入るようにして、キャリブレーション時間の大幅な時間短縮が可能となり、低消費電流化に貢献できるようにする。

【解決手段】PLLループをオープンにし、電圧制御発振器1に制御電圧Vcとして基準電圧Vaを入力したとき、基準信号f3のパルスによって帰還信号f2のパルス幅をカウントし、得られたカウント値に基づき、電圧制御発振器1の発振周波数f1を調整するキャリブレーションを実行するキャリブレーション回路10を設ける。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

遅延ロックループ回路及びロックアップ方法

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

クロック供給回路及び半導体集積回路

【課題】高速なクロックを内部回路に供給するためには、消費電力の高いクロックバッファを必要とする。そのため、高速なクロックを低消費電力で供給するクロック供給回路及び半導体集積回路が、望まれる。

【解決手段】クロック供給回路は、電圧制御発振器を含むPLL回路と、電圧制御発振器の発振周波数を制御する発振制御電圧に基づいて、電圧制御発振器の発振周波数と略同一の周波数を持つクロックを、PLL回路のリファレンスクロックに同期させて出力する自己発振型バッファ回路と、を備えている。

(もっと読む)

可変分周装置

【課題】クロック信号が高速化した場合でも対応することのできる可変分周装置を得る。

【解決手段】可変分周回路101は、クロック信号Clk_aを入力し、クロック信号Clk_aに対するP(Pは2以上の整数)またはP+1の分周した信号Do1を出力する。可変分周回路102は、クロック信号Clk_aと逆相になるクロック信号Clk_bを入力し、クロック信号Clk_bに対するPまたはP+1の分周した信号Do2を出力する。経路切り替え回路103は、信号Do1,Do2を入力し、経路選択信号MuxContにより信号Do1,Do2のうちいずれか一方を選択し出力する。

(もっと読む)

位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラム

【課題】アナログ特性を容易な設計で高速なデジタルアシストが可能な位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラムを提供する。

【解決手段】デジタルアシストキャリブレーション回路は、探索範囲を所定の値から順番に検索値を変更して、検索値と目的値との大小関係を確認する順次探索と、探索範囲の検索値の中央値と上記目的値との大小関係を確認し、目的値が含まれる側の半分の検索範囲に対してのみその半分の検索範囲の検索値の中央値と目的値との大小関係を確認して、目的値を検索していく二分探索と、を選択的に処理可能で、検索過程における最初の過程と最後の過程のうち、少なくとも最初の過程と最後の過程のいずれかにおいて二分探索を行い、残りの過程では順次探索処理を行う。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

電流−モード利得分割デュアル−パスVCO

【課題】大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術の提供。

【解決手段】VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ252、電流増幅器254、総和器256、及び電流制御オシレータ(ICO)260を含む。電圧−電流コンバータは、制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流I3を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流CTRLを受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

チャージポンプ回路

【課題】充放電電流の立ち上がりを高速にし、かつ誤動作のおそれがないチャージポンプ回路を提供する。

【解決手段】ダイオード接続されたトランジスタMp1と、トランジスタMp2と、指令信号UPbで制御されてMp1,Mp2のゲート間を接続するトランジスタMp3とで第1のカレントミラー回路が構成されている。トランジスタMp2のゲート電極と電源VDDの間には指令信号UPbで制御されるトランジスタMp4が接続されている。また、ダイオード接続されたトランジスタMn1と、トランジスタMn2と、指令信号DNで制御されてMn1,Mn2のゲート間を接続するトランジスタMn3とで第2のカレントミラー回路が構成されている。Mn2のゲート電極と接地の間には、指令信号DNbで制御されるトランジスタMn4が接続されている。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

チャージポンプ回路

【課題】後段のループフィルタの状態によらずに電流誤差を低減し、且つ、高速動作が可能なチャージポンプ回路を提供する。

【解決手段】VDDの端子とノードN1との間に接続される定電流源I1と、VSSの端子とノードN2との間に接続される定電流源I2と、入出力端子ICPとノードN1との間に接続され信号UPが入力するトランジスタMP1と、入出力端子ICPとノードN2との間に接続され信号DNが入力するトランジスタMN1と、入出力端子ICPに入力側が接続される電圧増幅器11と、ノードN1と電圧増幅器11の出力側に接続され信号UPの反転信号UPBが入力するトランジスタMP2と、ノードN2と電圧増幅器11の出力側に接続され信号DNの反転信号DNBが入力するトランジスタMN2とを備える。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

1 - 20 / 124

[ Back to top ]