Fターム[5J106KK05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 性能の向上 (885) | 高精度化 (345)

Fターム[5J106KK05]の下位に属するFターム

定常位相誤差の低減 (66)

Fターム[5J106KK05]に分類される特許

1 - 20 / 279

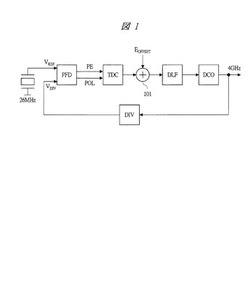

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

発振器

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

時間−デジタル変換器及びPLL回路

【課題】本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

(もっと読む)

半導体装置

【課題】調整コードの変化に伴うジッタの発生が低減されたDLL回路を提供する。

【解決手段】内部クロック信号ECLKを受けるインバータ回路210〜217と、内部クロック信号OCLKを受けるインバータ回路220〜227とを有し、調整コードC0〜C7を受けて選択されたインバータ回路の出力を合成することによって、内部クロック信号LCLKの位相を16段階に調整する。インバータ回路210,220は内部クロック信号LCLKの位相を1段階変化させる能力を有し、インバータ回路211〜217,221〜227は内部クロック信号LCLKの位相を2段階変化させる能力を有する。このように、内部クロック信号LCLKの位相を調整するインバータ回路の最大能力が抑制されていることから、調整コードの変化に伴うジッタの発生が低減される。

(もっと読む)

無線機

【課題】煩雑なメンテナンスを行わなくても周波数精度を高く保つことができ、かつ変調信号による周波数偏移を大きくすることができる無線機を提供する。

【解決手段】基準信号を出力する電圧制御水晶発振器と、高周波信号を出力する電圧制御発振器と、基準信号と高周波信号とが入力され、高周波信号の位相が基準信号と同じになるように位相同期を行う位相同期回路と、参照信号を発生する参照信号発生部と、基準信号の周波数を補正する周波数補正信号を電圧制御水晶発振器に出力するとともに、基準信号と参照信号とに基づき、基準信号の周波数が参照信号の周波数に対して所定の範囲内となるように周波数補正信号の値を変更する制御部と、から無線機を構成する。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。更に前記温度検出値に基づいて、OCXOの設定周波数を補正し、雰囲気温度が基準温度からずれたことによる周波数の変動分を補償するようにする。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

ガスセルユニットおよび原子発振器

【課題】周波数精度を向上させることができるガスセルユニットおよび原子発振器を提供すること。

【解決手段】本発明のガスセルユニット2は、ガス状のアルカリ金属原子を封入したガスセル21と、ガスセル21を加熱するヒーター22と、ガスセル21を介してヒーター22に対向して設けられ、ガスセル21を加熱するヒーター23とを有し、ヒーター22は、通電により発熱する発熱抵抗体222を備え、ヒーター23は、発熱抵抗体222に流れる電流の方向と同方向に電流が流れ、通電により発熱する発熱抵抗体232を備え、発熱抵抗体222と発熱抵抗体232との間にて、発熱抵抗体222への通電に伴って生じる磁場と、発熱抵抗体232への通電に伴って生じる磁場とを互いに相殺または緩和させる。

(もっと読む)

信号生成回路、レーダー装置

【課題】低雑音で高周波数精度かつ高線形なFMCW信号を得ることのできる信号生成回路、レーダー装置を提供する。

【解決手段】アナログ制御信号により発振信号の周波数が制御される発振器を有している信号生成回路は、発振信号の位相情報を検出してディジタルの位相情報を出力するディジタル位相検出部と、ディジタルの位相情報を微分してディジタルの周波数情報を出力する第1の微分部と、発振周波数を設定する周波数設定コードとディジタルの周波数情報とを比較してディジタルの周波数誤差情報を出力する比較部と、ディジタルの周波数誤差情報の高周波成分を除去するローパスフィルタ部とを備えている。さらに、高周波成分が除去されたディジタルの周波数誤差情報をアナログの周波数誤差情報に変換するD/A変換部と、アナログの周波数誤差情報を積分してアナログの位相誤差情報に変換しアナログ制御信号として出力する積分器とを備えている。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

PLL周波数シンセサイザ

【課題】 フラクショナルN方式のPLL(Phase-locked loop;位相同期回路)周波数シンセサイザにおいて生じる、フラクショナルスプリアスを抑圧する。

【解決手段】 可変分周器の分周数を2つ以上の整数値で時間的に切り替えるフラクショナルN方式のPLL周波数シンセサイザにおいて、電圧制御発振器2とループフィルタ7の間に、抑圧周波数および減衰量の制御を可能とする可変ノッチフィルタ8を設けることで、フラクショナルスプリアスを抑圧することができる。

(もっと読む)

1 - 20 / 279

[ Back to top ]