Fターム[5J106KK33]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 間欠動作 (21)

Fターム[5J106KK33]に分類される特許

1 - 20 / 21

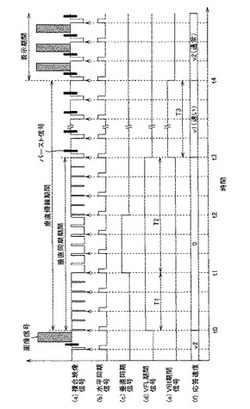

バーストクロック発生回路

【課題】バーストクロック信号を安定に生成できるバーストクロック発生回路を提供する。

【解決手段】このバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では位相ロックフィルタ4の応答速度を0に設定し、各垂直帰線期間のうちの垂直同期期間を除く期間では位相ロックフィルタ4の応答速度を比較的速い速度v1に設定し、複合映像信号における垂直帰線期間以外の表示期間では位相ロックフィルタ4の応答速度を比較的遅い通常の速度v2に設定する。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成できる。

(もっと読む)

送受信装置

【課題】構造簡単な距離を測定可能とした送受信装置の実現

【解決手段】第1信号の受信と第2信号の送信とを共通化した送受信アンテナ20と、第1信号を復調して第1パルス信号を得る復調器30と、制御信号を入力して目標周波数を設定する目標周波数設定レジスタ61と目標位相を設定する目標位相設定レジスタ66とを有し、目標周波数設定レジスタに設定されている目標周波数と目標位相設定レジスタに設定されている目標位相とに一致した周波数と位相の第2パルス信号を出力するパルス発振器60を有する。第2パルス信号により搬送波を変調する変調器70と、第1パルス信号と、第2パルス信号との位相差を検出する位相比較器32を有する。また、位相差信号の時間変動からその時の第1パルス信号と第2パルス信号との周波数差をもとめ、その周波数差に基づいて目標周波数を制御する周波数制御装置と、位相差信号の示す位相差に基づいて目標位相を制御する位相制御装置とを有する。

(もっと読む)

クロック信号を生成できる、または各トランシーバに関連付けられたデジタル・システムのデータのバイパスを可能にする、電力管理されたトランシーバのネットワークを使用する通信システム

【課題】感知回路の雑音感受性を最小にするとともに、回路の少なくとも一部に対する電力を管理して、消費電力を少なくした通信システムを提供する。

【解決手段】通信システムはノードのセットを含む。各ノードはトランシーバ・インターフェイスとデジタル・システムを含む。トランシーバは、通信回線とデジタル・システムとの間に結合されており、伝送フォーマットおよび/または伝送プロトコルを対応するノード内の1つまたは複数のデジタル・システムにより認識されるビットのシーケンスに修正する。トランシーバは、デジタル・システムを支持する回路基板から分離された1つまたは複数のモノリシック回路基板に配置される。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

データ再生回路

【課題】バースト光信号が入力された場合のロックアップ動作を高速に行うデータ再生回路を得ること。

【解決手段】本発明にかかるデータ再生回路は、VCO4で生成したクロックと入力データとを比較し、比較結果に基づいてVCO4への入力電圧を調整するPLL回路(周波数・位相比較器1,フィルタ処理回路2,VCO4)と、VCO4で生成されたクロックを利用して入力データを識別再生する識別回路6と、各子局装置からの送信スケジュールに基づいて、データ入力区間を特定する受信タイミング生成回路8と、を備え、PLL回路は、第1のデータ入力区間が終了後、その次の第2のデータ入力区間が開始するまでの区間では、第1のデータ入力区間に含まれるEOB区間でVCO4への入力としていた電圧信号を、VCO4へ継続して入力させる。

(もっと読む)

PLL装置及びその制御方法

【課題】 基準入力期間に対して基準信号断期間が長期間継続しても、基準信号に同期して安定した信号を出力することが可能な、制御が容易で安価なPLL技術を提供する。

【解決手段】 基準発信源から入力される基準信号に対して所定の位相差を有する出力信号を生成するPLL装置は、前記基準信号と前記出力信号との位相を比較して、当該位相の位相差に対応する位相差信号を出力する比較手段と、基準となる位相差に対応する基準位相差信号を保持する保持手段と、前記位相差信号、又は、前記基準位相差信号を制御信号として選択する選択手段と、前記選択手段が選択した制御信号に応じた周波数の前記出力信号を発振して出力する発振手段と、を備え、前記選択手段は、前記基準発信源から前記基準信号が入力されている期間は前記位相差信号を選択し、前記基準発信源から前記基準信号が入力されていない期間は前記基準位相差信号を選択する。

(もっと読む)

原子発振器

【課題】τ秒平均時間の短い期間における短期安定度を向上させた原子発振器を提供する

。

【解決手段】周波数制御部2は、光検出器の出力信号をデジタル信号に変換するA/D変

換器12と、制御電圧を所定の周期又はデューティ比で間欠的に出力するタイミングを生

成するタイマ(制御周期生成手段)13と、タイマ13により生成されたタイミングに基

づいて出力された制御電圧Vcをアナログ電圧に変換するD/A変換器10と、タイマ1

3のタイミングに基づいて、パワーダウンする期間を指示した信号を出力するIO(パワ

ーダウン生成部)14と、全体の動作を制御するCPU11と、を備え、IO14は、少

なくとも周波数合成逓倍部4、又は/及び、原子共鳴部3をパワーダウンするように構成

されている。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

データ通信システムの高速パワーアップ

データ通信システムは、第1のクロック発生回路を有する送信機と、第2のクロック発生回路を有する受信機とを具えている。第1及び第2のクロック発生回路のうちの少なくとも一方の特定のクロック発生回路が順次のデータバースト間でパワーダウンされるようになっている。このデータ通信システムは、前記特定のクロック発生回路がパワーダウンした際にこのデータ通信システムを実用使用状態に起動するのを促進させる。このデータ通信システムは、起動時に前記特定のクロック発生回路の動作量を予め決定した値にプリセットする。  (もっと読む)

(もっと読む)

自動周波数制御回路

【課題】 自動周波数制御回路における検出部の起動および停止を簡単に制御し、消費電力を低減する。

【解決手段】 受信パケットから送信装置と受信装置との間のクロック周波数の誤差を検出し、その周波数誤差に対する補正値を出力する検出部と、検出部から出力された補正値に基づいて受信パケットの周波数誤差を補正する補正部とを備えた自動周波数制御回路において、検出部とは別のアルゴリズムで、受信パケットの周波数誤差の有無を簡易に判定し、周波数誤差があれば検出部を動作させ、周波数誤差がなければ検出部の動作を停止させ、検出部の動作時に出力した補正値を受信パケットの周波数誤差の補正に用いる制御を行う簡易判定部を備える。

(もっと読む)

ヘテロダイン受信機、PLL発振回路及び間欠受信制御方法

【課題】PLL発振回路を使用して間欠受信動作を行う受信機のオン・オフ時間の比率を大きくして、省電力効果の向上を図ったPLL発振回路、ヘテロダイン受信機及びその間欠受信制御方法を提供する。

【解決手段】PLL発振回路の要部への電源制御用第一のスイッチと、位相比較器と低域フィルタとの間に挿入した第二のスイッチ回路とを備え、これらを間欠的に制御することにより、PLLの同期を促進する。

(もっと読む)

クロック制御回路

【課題】発振回路からの基準クロックを供給し続けなくても、PLL回路からの所定のクロックの出力を継続させることができるようにする。

【解決手段】電圧信号V0に応じた周波数の動作クロックCKを生成する電圧制御発振器3と、動作クロックから比較クロックCKrを生成する分周回路4と、比較クロックを発振回路1の基準クロックCK0と位相比較して位相比較信号S1を生成する位相比較器5と、位相比較信号を第1の電圧信号V1に変換するローパスフィルタ7と、第1の電圧信号から第2の電圧信号V2を生成する電圧制御回路8と、第1の電圧信号と第2の電圧信号の一方を選択して電圧制御発振器3へ出力する選択回路9と、選択回路9に初期には第1の電圧信号を選択させ、電圧制御回路8が第2の電圧信号を生成した後は、選択回路に第2の電圧信号を選択させるとともに、発振回路1の動作を停止させる制御手段(CPU)10を備える。

(もっと読む)

発振制御回路

【課題】内部に搭載したPLLが生成したクロック信号で内部回路を駆動するLSIにおいて、PLLの動作を外部より停止させる場合、出力クロック信号の波形を崩し、内部回路の安定動作を保証できない可能性がある。

【解決手段】PLL21の動作を停止させる場合は、第1のフリップフロップ22により、PLL21より出力されるクロック信号CLKに同期させてPLL21を停止させる。PLL21の動作を復帰させる場合は、第2のフリップフロップ23により、クロック信号CLKを使用せずに外部制御信号であるライトイネーブル信号WEにて復帰させる。

(もっと読む)

半導体装置

【課題】 PLL回路の出力の張り付きを防止する。

【解決手段】 半導体装置1には、入出力回路部2、アナログ回路部3、デジタル回路部4、入力端子PIN、制御端子PCTL、及び電源端子PVccが設けられている。アナログ回路部3には、第1の電源回路11、第2のレベルシフト回路16、位相周波数比較器17、チャージポンプ回路18、ループフィルタ19、及び電圧制御発振器20が設けられ、デジタル回路部4には、第2の電源回路12、第1のレベルシフト回路15、分周回路7、及び論理回路・メモリ部6が設けられている。アナログ系電源が供給され、デジタル系電源が供給されないとき、第1のレベルシフト回路15がONしないので、位相周波数比較器17はリセットされず動作を開始しない。

(もっと読む)

発振回路及び赤外線受信装置

【課題】間欠動作時の消費電流を低減することができる発振回路を提供する。

【解決手段】発振回路2aは、コンデンサC0を充放電する充放電回路4aと、充放電回路4aによるコンデンサC0の充放電に応じて変化する充放電信号Xに基づいて、受信デバイスを間欠動作させるために、受信デバイスの間欠動作の周期を表すインターバル期間と間欠駆動する受信デバイスがオンしている期間を表すウォッチ期間とが設定された信号out1を生成する信号生成回路5aとを備え、信号生成回路5aは、基準電圧Vth1と基準電圧Vth2との間の電圧差に基づいてインターバル期間を信号out1に設定し、基準電圧Vth1と基準電圧Vth2との間の電位をそれぞれ有する基準電圧Vth3と基準電圧Vth4との間の電圧差に基づいてウォッチ期間を信号out1に設定する。

(もっと読む)

遅延固定ループ回路

【課題】半導体設計技術に関し、特に、SDRAMの遅延固定ループ回路に関し、さらに詳細には、半導体の低電力動作のためのパワーダウンモードの動作の際に、安定した遅延固定ループ回路の動作のための回路を提供すること。

【解決手段】パワーダウンモードの脱出の際に発生できる遅延固定ループ(DLL)回路ロックフェイルを防止するための回路である。本発明では、パワーダウンモードの脱出の後に、内部クロック信号の位相とデータ出力端から出力されるフィードバック信号の位相とを比較して、更新が可能な時間が短い場合、前記内部クロック信号とフィードバック信号とを同期化して、正常的なデータ送受信が困難になるのを防止するために、パワーダウンモードの進入を知らせる制御信号のクロックエッジを感知し、その信号を遅延させた信号でDLLのクロックバッファをオン・オフ駆動する。

(もっと読む)

ロックフェイル防止のための遅延固定ループクロックの生成方法及びその装置

【課題】相対的に長時間パワーダウンモードにとどまる場合、チップの温度等の様々な環境の変化によってロックフェイルが発生することを防止する遅延固定ループ装置を提供すること。

【解決手段】本発明の遅延固定ループ装置は、パワーダウンモードへの出入を決定する制御信号を生成するパワーダウンモード制御部と、制御信号によりノーマルモードで外部クロックをバッファリングし第1の内部クロック信号を生成する第1のクロックバッファと、制御信号によりパワーダウンモードで外部クロックをバッファリングし第2の内部クロック信号を生成する第2のクロックバッファと、制御信号によりノーマルモードでは第1の内部クロック信号を選択し、パワーダウンモードでは第2の内部クロック信号を選択して伝達するクロック選択部と、クロック選択部で選択された信号を使用して位相更新を行うことによりDLLクロックを出力する位相更新部とを備える。

(もっと読む)

発振装置およびその制御方法

【課題】発振装置の電力を削減する。

【解決手段】通常の使用状態では、PLL周波数シンセサイザ部31の基準発振器11、第1分周器12、位相比較器13および第2分周器16は動作せず、消費電流量を格段に小さなものとする。そして、A/D変換機18、制御回路21、D/A変換器20、第1スイッチ17、第2スイッチ19およびコンデンサ22を備えることによって、PLL周波数シンセサイザ部31を間欠的に働作させ、出力発振信号Sfoが所望の周波数となるように較正し、出力発振信号Sfoを得る。

(もっと読む)

局部発振回路、携帯情報端末および局部発振制御方法

【課題】 TDMA/TDDのスロット可変型通信における周波数の変動を防止する。

【解決手段】 2系統のPLL回路をそれぞれ有する第1の集積回路(40a)および第2の集積回路(40b)と、基準発振回路(30)と、2系統の周波数帯域の信号を出力する出力回路(50,60)とを備える。互いに同一系統となる2つの第1PLL回路(70A,70B)は、該各PLL回路をフレーム期間中の異なるタイムスロットにて動作させるための制御信号が供給される信号線(70AC,70BC)と出力回路とに接続される。第1の集積回路の第2PLL回路(80A)は、該PLL回路を上記タイムスロットの双方にて動作させるための制御信号が供給される信号線(80AC)と出力回路とに接続される。第2の集積回路の第2PLL回路(80B)は、出力回路には接続されず、第1の集積回路のPLL回路が接続された信号線(70AC,80AC)のうちのいずれかと接続される。

(もっと読む)

クロック生成回路

【課題】

回路規模と消費電力とを増大させることなく、規格などに定められた変動周期および周波数の変動範囲を満足するように、出力クロック信号の周波数拡散を実現できるようにする。

【解決手段】

電圧制御発振器110の発振周波数を制御する発振周波数制御信号をリークさせる電流経路160が設けられ、電圧制御発振器110のサイクル数をカウントするカウンタ170のカウント結果に応じた所定の周期で、位相検出器120の出力のオン/オフの状態が切り替えられる。位相検出器120の出力がオフの時には、電流経路160で発振周波数制御信号がリークさせられることによって電圧制御発振器110の発振周波数が低下する。次に位相検出器120の出力がオンになると、フィードバック制御により低下した電圧制御発振器110の発振周波数が所定の周波数まで上昇する。

(もっと読む)

1 - 20 / 21

[ Back to top ]