Fターム[5J106KK32]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 調整、設定、試験 (111)

Fターム[5J106KK32]に分類される特許

1 - 20 / 111

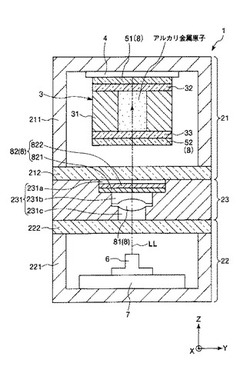

原子発振器および原子発振器の製造方法

【課題】 優れた特性を発揮することのできる原子発振器および原子発振器の製造方法を提供すること。

【解決手段】原子発振器1は、ガス状の金属原子を封入したガスセル3が収納された第1パッケージ21と、ガスセル3中の金属原子を励起する励起光LLを出射する光出射部6が収納された第2パッケージ22と、少なくとも1つの光学部品8が設けられた第3パッケージ23とを有している。また、第2パッケージ22の一方側に第3パッケージ23が固定され、第3パッケージ23の第2パッケージ22と反対側に第1パッケージ21が固定されている。光出射部6から出射した励起光LLが、光学部品8を通過したのちガスセル3内に入射するよう構成されている。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

位相差検証回路

【課題】別途、基準クロックなどを用意することなく、複数のクロック信号間の位相差が一定であるか否かを検証することができる位相差検証回路を得ることを目的とする。

【解決手段】AND回路11−0〜11−7からパルス信号#0〜#7が出力されている期間中、電荷を蓄積するキャパシタチャージ回路13−0〜13−7を設け、比較回路14が、キャパシタチャージ回路13−0〜13−7により蓄積された電荷の充電量を示す電圧信号Vout#0〜#7を比較し、その電圧信号Vout#0〜#7が一致していれば、クロック信号#0〜#7間の位相差が一定であることを認定する。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

信号処理装置

【課題】 外部からの基準信号の周波数変化が安定している状態であるかどうかをユーザが容易に判別可能とする。

【解決手段】 外部機器から供給された基準信号を入力する入力手段と、前記入力手段により入力された基準信号とクロックとの位相差を検出する位相検出手段と、前記位相検出手段の出力に応じた周波数の前記クロックを発生する発生手段と、前記位相検出手段の出力に基づいて前記入力手段により入力された基準信号の周波数と前記クロックの周波数との誤差を検出し、前記検出した誤差に基づいて前記基準信号の周波数変化の状態を示す情報を表示装置に表示する制御手段とを備える。

(もっと読む)

半導体集積回路

【課題】テストパターンや期待値パターンを蓄えておくメモリを半導体集積回路に増設することなく、SSCG、PLL、又は、DLL等のクロック生成モジュールの単体試験を容易に可能とする。

【解決手段】この半導体集積回路は、入力されるクロック信号に基づいて新たなクロック信号を生成して出力するモジュールと、モジュールに入力されるクロック信号に含まれているパルス数をカウントする第1のカウンタと、モジュールから出力されるクロック信号に含まれているパルス数をカウントする第2のカウンタと、第1のカウンタのカウント値と第2のカウンタのカウント値とを比較して、両者が一致するか否かを表す信号を出力するコンパレータと、コンパレータから出力される信号をサンプリングする回路とを具備する。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、低ジッタで大きな電源電圧・温度変動耐性を実現する。

【解決手段】第1の発振回路および第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第2の発振回路および第1の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Ca,Cbを入力する端子を備え、第1〜第2の発振回路はそれぞれ2つの制御端子を備え、それぞれの一方の制御端子に周波数制御信号Aを入力し、第1の発振回路の他方の制御端子に回路間ばらつき調整信号Caを入力し、第2の発振回路の他方の制御端子に回路間ばらつき調整信号Cbを入力する構成。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、ジッタを低減する。

【解決手段】第1の発振回路および第2の発振回路はそれぞれ2つの周波数制御端子を備え、それぞれの一方の周波数制御端子に周波数制御信号Aを入力する構成であり、第2の発振回路の他方の周波数制御端子に固定の周波数制御信号Bを与え、第1の発振回路および第2の発振回路の各発振周波数を比較し、その周波数誤差に応じた周波数制御信号Cを第1の発振回路の他方の周波数制御端子に与えるばらつき補償回路を備える。

(もっと読む)

位相同期回路

【課題】デジタル型の位相比較器だけで構成しつつ、不感帯の影響を排除して出力信号の位相雑音を低減する。

【解決手段】制御電圧Vcに応じた周波数の出力信号Soを出力する電圧制御発振器4と、位相比較対象信号Sdおよび基準信号Srを入力して、位相比較対象信号Sdの位相が基準信号Srの位相に対して遅れているときには両信号Sd,Srの位相差に応じたパルス幅の第1パルス信号S1を出力し、位相比較対象信号Sdの位相が基準信号Srの位相に対して進んでいるときには両信号Sd,Srの位相差に応じたパルス幅の第2パルス信号S2を出力する位相比較器2と、両パルス信号S1,S2を入力すると共に両パルス信号S1,S2の差分を積分して制御電圧Vcを出力するループフィルタ3とを備え、両パルス信号S1,S2のうちの一方のパルス信号の信号電圧を他方のパルス信号の信号電圧と異なる電圧に規定する電圧規定部6を備えている。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

測定装置、再生装置、測定方法

【課題】PLL回路をより的確に評価できるPLL性能測定装置を提供する。

【解決手段】フェーズロックドループ回路にて検出される位相誤差についての移動平均を求める。この移動平均と閾値との比較に基づいて、フェーズロックドループ回路がロック状態に収束したか否かの判定を行う。

(もっと読む)

1 - 20 / 111

[ Back to top ]