Fターム[5J106KK39]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 簡素化 (146)

Fターム[5J106KK39]に分類される特許

1 - 20 / 146

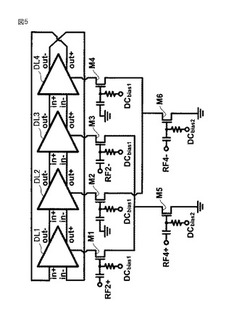

分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

PLL回路

【課題】本発明は、遅延素子の遅延時間のばらつきを補償するように、デジタルコードを補正する必要のないTDCを提供することを目的とする。

【解決手段】基準信号の周波数に対して所望倍数の周波数を有する出力信号を出力する発振部と、基準信号についての出力信号の整数分周及び小数分周の和並びに当該所望倍数について差分を計算し、発振部に当該差分を0にするように出力信号を出力させる位相比較部と、を備えるPLL回路において、TDC2は、小数分周の初期値を設定し、初期値を計測値として出力するデジタルコード発生器23と、初期値に基づく位相比較部及び発振部の動作後に、当該差分を0にする方向に、小数分周の分解能を1ステップとして段階的に、小数分周を初期値から最適値へと更新し、最適値を計測値として出力するデジタルコード発生器23及び加減算器24と、を備える。

(もっと読む)

遅延回路、DLL回路、および半導体装置

【課題】 段数切替型の遅延回路において、段数切替時に発生するハザードを抑制する。

【解決手段】 本発明の段数切替型の遅延回路は、段数切替前後で遅延回路の内部ノードの論理状態が変化しないように、遅延のための経路として選択されていない段に遅延回路の入力が接続されている。これにより、遅延回路のハザードの発生を抑制することができ、ひいては遅延回路を備えるDLL回路や半導体装置の論理規模を低減でき、低消費電力化に寄与し、また、半導体装置の処理速度を向上させることができる。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

周波数シンセサイザ

【課題】ディジタル処理を用いたPLLにより周波数シンセサイザを構成するにあたって、A/D変換部を不要とすること。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

(もっと読む)

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

イオントラップ構造、イオントラップ型周波数標準器及び出力周波数安定化方法

【課題】構造がシンプルであり、且つトラップホールの影響を排除できるイオントラップ構造、イオントラップ型周波数標準器及び出力周波数安定化方法を提供することを目的とする。

【解決手段】イオントラップ型周波数標準器301は、所定の領域を取り囲むように平行且つ対称に配置される4以上の偶数の第1直線状電極36と、領域内に生ずるポテンシャルの領域の中心軸方向のポテンシャルを制御する調整電極(31〜34、37)と、を備えるイオントラップ構造を有する。

(もっと読む)

ルビジウム原子発振器

【課題】回路構成を単純化して部品コストを低減すると共に、回路の小型化を実現したルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器50は、ルビジウム原子の共振周波数により励振する光マイクロ波ユニット(OMU)1と、OMU1を透過した光の強度を検出する光検出部2と、Amp3に現れる周波数誤差信号の位相を検波する位相検波器4と、位相検波器4の出力信号を積分するループフィルタ5と、ループフィルタ5の電圧に基づいて所定の周波数を発振する電圧制御水晶発振器(VCXO)6と、マイクロ波の位相を低周波により変調する発振回路7と、VCXO6の発振信号をマイクロ波に逓倍する位相変調逓倍部8と、を備えて構成されている。

(もっと読む)

信号伝搬遅延を補償するための装置及び方法

【課題】1以上の伝送接続上の電気信号など、1以上の信号の伝搬遅延または時間を補償する装置及び方法を提供し、実装のための複雑な演算手段を必要とせず、自動的に伝搬時間の補償を行なうことを可能とする。

【解決手段】第1伝送接続(104)の第1端(106)と第2端(108)の間を伝搬中に第1周期信号ref(t)が受ける遅延τを補償するための装置(100)であり、前記第1信号ref(t)に対応し、その位相が遅延τに等しい時間により位相前進された第2信号ref(t+τ)を生成可能な第1手段(114)と、前記第1伝送接続の前記第2端で取得され前記第1信号ref(t)に対応し、その位相が遅延τにより遅延された第3信号ref(t-τ)と、前記第2信号ref(t+τ)とから、前記第1信号ref(t)と同位相である第4信号を生成可能な第2手段(116)とを少なくとも備える。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

無線通信機

【課題】信号発生器の周波数設定データを複数の箇所から設定する際に、複雑なスイッチを設けることなく、周波数設定データの衝突を防止し、また、より狭い周波数偏差の要求に応える。

【解決手段】無線通信機100は、PLL回路144を構成するPLLIC128と、PLLICに出力周波数を設定する第1のデータを出力し、少なくとも、PLLICへのアクセス不実行状態と、アクセス待機状態と、アクセス実行状態との3つの状態を遷移するCPU112と、出力周波数を増加もしくは減少させるためPLLICに設定する第2のデータを出力し、少なくとも、PLLICのアクセス可能状態と、アクセス禁止状態との2つの状態を遷移するDSP118とを備え、CPUとDSPとが第1の信号と第2の信号によって互いに状態遷移に関する情報を交換し、PLLICへのアクセスの衝突を防止する。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】簡易な構成によりクロックリカバリを実現し、伝送時のオーバーヘッドを削減する。

【解決手段】送信装置1−1は、制御用メタデータを生成し、制御用メタデータを定期的に受信装置2−1へ送信する。また、送信装置1−1は、コンポーネントの符号化を行い、自身のコンポーネントのクロックを用いてPCR、DTS及びCTSを生成し、または、他のコンポーネントのクロックを用いてDTS及びCTSを生成し、コンポーネントの符号データ等を受信装置2−1へ送信する。受信装置2−1は、制御用メタデータを定期的に受信すると共に、コンポーネントの符号データ等を受信する。そして、受信装置2−1は、制御用メタデータに従って、受信したPCRに基づいて自身のコンポーネントのクロックに対しクロックリカバリを行い、復号等を行う。また、受信装置2−1は、他のコンポーネントのクロックを流用して復号等を行う。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

クロック生成回路および電子機器

【課題】クロック生成回路の回路規模を抑制しつつ、クロック信号の周波数スペクトルを好適に拡散する。

【解決手段】クロック生成回路1の電流制御発振部13は、供給される電流に応じた遅延量で信号を遅延する複数の電流制御遅延回路11を含む閉ループ12によりクロック信号を生成する。位相制御部15〜18は、クロック信号と基準信号とを比較する比較器15を有し、これらの信号の位相差を減らすように変化する制御電流を、複数の電流制御遅延回路11に供給する電流として出力する。拡散電流生成部19は、複数の電流制御遅延回路11の一部に対して、制御電流の替わりに、制御電流と異なる電流値のスペクトラム拡散電流を供給する。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

1 - 20 / 146

[ Back to top ]