Fターム[5J106GG08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 周波数変換回路 (216)

Fターム[5J106GG08]の下位に属するFターム

分周回路 (187)

Fターム[5J106GG08]に分類される特許

1 - 20 / 29

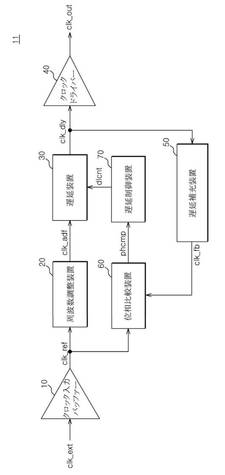

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

広帯域PLL発振回路

【課題】周波数逓倍回路を含む広帯域PLL発振回路において、逓倍回路出力端に高調波等の不要周波数信号を除去するフィルタを必要とせず、簡単な構成によって不要周波数信号に起因して間違った周波数に同期することなく、安定した動作が得られる広帯域PLL発振回路を提供する。

【解決手段】

逓倍回路に同調周波数制御機能を備え、発振周波数に応じて適切な同調周波数になるように制御する。また、PLLロックインまでの時間短縮のためにメモリに記憶した制御電圧情報をVCOに印加する機能を備え、この制御電圧情報によって同時に逓倍回路の同調周波数を制御する。

(もっと読む)

クロック再生装置

【課題】高速で安定したクロックを再生できるクロック再生装置を提供すること。

【解決手段】受信データからデータ受信用の再生クロックを得るクロック再生装置において、前記受信データから不連続を含む再生クロックを生成する再生クロック生成部と、この再生クロック生成部から出力される再生クロックを所定時間逓倍する再生クロック逓倍部とを有し、前記再生クロック生成部から出力された不連続を含む再生クロック信号を前記再生クロック逓倍部で演算し、連続した再生クロックを得ることを特徴とするクロック再生装置。

(もっと読む)

低電力非同期カウンタ及び方法

【解決手段】低電力非同期カウンタの設計技術。典型的な実施形態では、複数のフリップフロップのクロック入力及び信号出力が、非同期カウント構造を実現するように直列に連結される。複数のフリップフロップの信号出力は、参照信号の順次遅延されたバージョンによってサンプリングされる。更に、参照信号の順次遅延されたバージョンを生成する設計方法が開示される。典型的な実施形態では、非同期カウント技術は、デジタル位相ロックループ(DPLL)の高速カウンタに使用され得る。 (もっと読む)

周波数シンセサイザ及び無線送信装置

【課題】VCOの出力帯域を選択設定可能な周波数シンセサイザにおける消費電力を低減すること。

【解決手段】互いに並列に接続されたミキサ111と分周器112とを有する周波数変換回路110を設け、VCO101の周波数帯域選択時に分周器112を用いることにより、VCO101の周波数帯域選択時の位相比較器102の最高動作周波数を低くすることができ、消費電力を低減できる。また、送信時にはミキサ111を用いることにより、送信時のループゲインを下げずに済む。

(もっと読む)

位相補間器及びクロックデータリカバリ装置

【課題】本発明は、ミキサの数を減らすことで回路面積及び消費電力を縮小し、位相の不整合を抑制することが可能な位相補間器を提供する。

【解決手段】位相差が0度のクロックD0を与えられミキサ2個分の遅延量を有するクロックD0+2Dcを出力する2ミキサM11、M12、位相差が0度のクロックD0と位相差が90度のクロックD90とを与えられ位相差が45度の遅延量とミキサ2個分の遅延量とを有するクロックD90+2Dcを出力するミキサM1、M13、クロックD0、D90、D45+2Dcのいずれか2つを用いて位相差が所定角度の遅延量とミキサ2個分の遅延量とを有するクロックを生成して出力する少なくとも1つのミキサを備える。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

フェーズロックドループ回路

【課題】入力される水平同期信号に対して、サンプリングクロックの周期の値に制約されることなく、位相誤差量を低減することができるフェーズロックドループ回路を提供する。

【解決手段】入力される水平同期信号(H-sync)は、逓倍PLL回路2から出力される、周期が等しく、1/4周期分づつずれた位相関係の4種の第1〜第4サンプリングクロックによりサンプリング回路でそれぞれサンプリングされ、各サンプリングクロックに位相同期した4種の水平同期出力データが生成され、これらはさらに加算回路6で加算されて加算水平同期出力データが生成された後、位相比較器13に入力され、分周器14で分周されたシステムクロック(第1サンプリングクロック)と位相比較される。

(もっと読む)

拡張されたトラッキング範囲を有する位相ロック・ループ(PLL)

PLLのトラッキング範囲を拡張するための方法は、それに関連する第1の幅を有する、PLLの初期トラッキング・ウィンドウを確立するステップと、PLLに供給された入力信号の周波数がトラッキング・ウィンドウ外にあるとき、第1の幅よりも大きい、それに関連する第2の幅を有する拡張されたトラッキング範囲内にPLLのトラッキング・ウィンドウを動的に調整するステップとを含む。  (もっと読む)

(もっと読む)

シンセサイザ

【課題】本発明は、周波数可変間隔(チャネルステップ)を細かく設定できると同時に位相比較周波数を高く設定し信号近傍の位相雑音を抑制することを目的とする。

【解決手段】本発明に係るシンセサイザは、高周波信号を発生させる第1のループ84に、第1のループ84の基準周波数を調整するための第2のループ85を設けたことを特徴とする。第2のループ85が第1のループ84の基準周波数を目的の周波数に調整する。第1のループ84は、第2のループ85の調整した基準周波数を用いて高周波信号を発生させる。第2のループ85が第1のループ84の基準周波数を微調整するので、第1のループ84の分周回路の分母を小さくしても周波数設定の分解能は粗くならない。第1のループ84の分周回路の分母を小さくしても、分解能を落とすことなく所望の周波数を発振する。

(もっと読む)

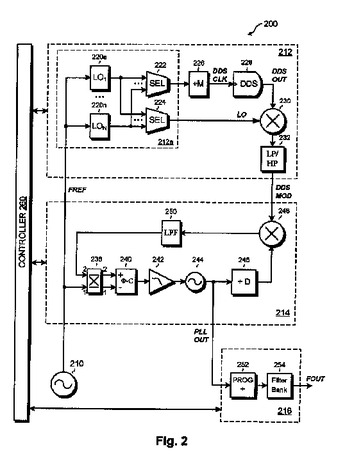

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

周波数切替え方法、周波数切替え装置および撮像装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときに異常動作が起きるのを防ぐことができる周波数切替え方法を提供する。

【解決手段】 出力信号の周波数を目標周波数に切り替えるときに、位相周波数比較器10とチャージポンプ回路11と逓倍設定回路14をリセット状態にし(S2)、逓倍数を目標周波数に対応した逓倍数C1に変更し(S4)、分周数を目標周波数に対応した分周数より大きい仮分周数2Nに変更する(S5)。その後、位相周波数比較器10とチャージポンプ回路11と逓倍設定回路14のリセット状態を解除して(S6)、分周数を目標周波数に対応した分周数Nに変更する(S8)。

(もっと読む)

周波数切替え装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときにシステム誤動作が起きるのを防ぐことのできる周波数切替え装置を提供する。

【解決手段】 周波数切替え器5は、位相周波数比較器10と、チャージポンプ回路11と、LPF回路12と、VCO回路13と、カウンタ回路14と、カウンタ回路14の動作を制御する制御部8を備える。制御部8は、逓倍数変更部16と、変更許可判定部15を備える。変更許可判定部15は、カウンタ回路14のカウンタ値に基づいて、逓倍数を目標逓倍数に変更するのを許可するか否かを判定する。例えば、カウンタ値が目標逓倍数以下の基準値(例えば、カウンタ値0)になったときに、逓倍数の変更を許可する。

(もっと読む)

信号発生装置

【課題】本発明では、汎用DDSを使用した周波数可変の信号発生装置において、ジッター発生を抑制し、高精度の周波数可変の矩形パルス信号を発生する。

【解決手段】周波数可変の信号発生装置は、設定値に応じて変更される周波数のアナログ信号を出力するDDS1と、該アナログ信号から該周波数の第1矩形パルス信号を生成するコンパレータ3と、第1矩形パルス信号を設定される分周比で分周した第2矩形パルス信号を出力するプログラマブル分周器41と、制御部4とを備える。該周波数を高周波数領域側に変更の場合、該分周器に対し第1矩形パルス信号を出力信号Soとする。該周波数を低周波数領域側に変更の場合、DDSに対して設定値を分周比倍の値に変更制御して該分周比倍の周波数を有する第1矩形パルス信号を発生させ、分周器において当該分周比で分周した当該周波数の第2矩形パルス信号を出力信号Soとする。

(もっと読む)

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

映像検波回路

【課題】AM変調されたPIF信号から映像信号を同期検波するVIF回路において、過変調状態にて復調される映像信号の精度が低くなる。

【解決手段】比較器68は、過変調状態であるVTH超の映像信号か否かを判定する。VTH以下の期間では、スイッチ回路56はAPCフィルタ54の出力電圧をVCO48に入力させ、PLLを構成する。PLLは、PIF信号にロックするように動作し、搬送波を再生する。一方、VTHを超える期間では、スイッチ回路56はSH回路58の出力電圧VSHをVCO48に入力する。SH回路58は、水平同期期間でのロック状態のAPCフィルタ54の電圧を保持しており、これを用いてVCO48を制御することで、フリーランや周波数ドリフトが抑制される。

(もっと読む)

1 - 20 / 29

[ Back to top ]