Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

81 - 100 / 330

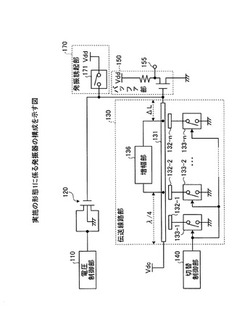

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

クロック供給装置

【課題】入力クロックの周波数がジッタやワンダ等により時間的に変動する場合においても、入力クロックの不具合の状態を的確に判定することができようにし、適切な保守が可能となる、クロック供給装置を提供する。

【解決手段】本発明のクロック供給装置においては、N系クロック受信部22とN系MTIE計測部31との間に設置されるワンダ・ジッタ除去フィルタ41と、E系クロック受信部23とE系MTIE計測部32との間に設置されるワンダ除去フィルタ42と、を有して構成される。そして、発振器部26が有するローパスフィルタ特性のカットオフ周波数と、ワンダ除去フィルタ41,42の有するローパスフィルタ特性のカットオフ周波数とが一致あるいは略等しいように構成される。

(もっと読む)

基準周波数発生装置

【課題】リファレンス信号が取得できなくなっても長時間にわたって高精度な基準周波数信号を出力可能で、使用温度範囲が広く、安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置11は、GPS受信機21と、PLL回路31と、検出器28と、記憶部29と、制御部22と、を備える。PLL回路31は、GPS受信機21からのリファレンス信号に基づいて得られた同期制御信号に基づき、デジタル制御発振器26を制御する。記憶部29には、同期制御信号の制御値と、そのときの電圧値及び温度と、の対応関係が記憶されている。リファレンス信号が得られない場合、制御部22は、前記対応関係と、検出器28が検出した電圧及び温度と、に基づいて自走制御信号を決定し、デジタル制御発振器26を制御する。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、ジッタを低減する。

【解決手段】第1の発振回路および第2の発振回路はそれぞれ2つの周波数制御端子を備え、それぞれの一方の周波数制御端子に周波数制御信号Aを入力する構成であり、第2の発振回路の他方の周波数制御端子に固定の周波数制御信号Bを与え、第1の発振回路および第2の発振回路の各発振周波数を比較し、その周波数誤差に応じた周波数制御信号Cを第1の発振回路の他方の周波数制御端子に与えるばらつき補償回路を備える。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

PLL回路

【課題】特性が悪化する可能性があった。

【解決手段】本発明は、第1および第2のループフィルタを有するPLL回路であって、前記第1のループフィルタに出力される第1の電流信号を生成する第1の出力ドライバと、前記第2のループフィルタに出力される第2の電流信号を生成する第2の出力ドライバとを備える電流信号生成回路と、前記第1もしくは第2の出力ドライバのいずれを活性化するか選択する制御回路と、を有するPLL回路である。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

光学系及び原子発振器

【課題】光源の光パワーのバラツキが所定の範囲変動しても一定の光吸収量を得ることが

できる原子発振器の光学系を提供する。

【解決手段】この光学系100は、共鳴光2を出射する光源1と、光源1から出射された

共鳴光2を導く出射光路を複数の出射光路a〜cの中から選択する光スイッチ3と、複数

の出射光路a〜cに夫々配置され、共鳴光4が通過する長さが夫々異なる複数のガスセル

5、6、7と、複数の入射光路A〜Cが各ガスセル5、6、7の出射側に配置され、光ス

イッチ3により選択されたガスセルを通過した励起光8を導く入射光路Aを複数の入射光

路A〜Cの中から選択する光スイッチ9と、励起光10を検出するPD11と、PD11

により検出された励起光10の吸収量に基づいて光スイッチ3及び光スイッチ9を制御す

る制御部12と、を備えて構成される。

(もっと読む)

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、パルスカウンタ12、充電回路13、リセット回路14、調整回路15及びタイミング制御部を備えている。タイミング制御部から供給されたカウント開始信号に基づいてパルスカウンタ12は、発振回路11から出力される周波数f0のパルス信号をカウントし、この間、出力信号S1を充電回路13に供給する。充電回路13は、出力信号S1が供給されている間、定電流減PS1とコンデンサC1とを接続し、接続ノードND1の電圧V1を上昇させる。調整回路15は、出力信号S1の出力が終了した場合の電圧V1が、高電位基準電圧VHより高い場合には、周波数f0を高くする調整値を発振回路11に供給し、低電位基準電圧VLより低い場合には、周波数f0を低くする調整値を発振回路11に供給する。

(もっと読む)

ディザ処理型クロック発生器

【課題】 位相分解能を高くし周波数スペクトラムのピークを低減したスペクトラム拡散クロック発生器を提供する。

【解決手段】 本発明のスペクトラム拡散クロック発生器100は、基準クロック信号と帰還クロック信号の位相差を検出する位相比較器20、チャージポンプ22、ループフィルタ24、多相のクロック信号を発生する多相VCO22、多相VCO26からの隣合う位相のクロック信号の位相を補間する位相補間部120、位相補完部120の位相選択を制御する位相選択部130、一定のステップ幅で段階的に変化する1周期分の変調波形データを記憶する変調データ部140、ディザステップ信号DSを出力するディザ処理部150、変調波形データとディザステップ信号を加算する加算器160を有する。位相選択部130は、ディザステップ信号が加算された変調波形データに基づき位相の補間を行う。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

81 - 100 / 330

[ Back to top ]