Fターム[5J106LL05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 同期化クロック制御回路 (17)

Fターム[5J106LL05]に分類される特許

1 - 17 / 17

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

基準周波数発生システム及び基準周波数発生装置

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のGPS受信機21aからケーブル101を介して出力された1PPS信号がPLL回路22bに供給される。予備側に入力された1PPS信号は、ケーブル101と遅延量が等しいケーブル102を介して現用側に戻される。現用側の基準周波数発生装置51は、自機のGPS受信機21aからの1PPS信号と、予備側に出力して戻された1PPS信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

同期化システム用結晶ベース発振器

【課題】クロックの不具合の可能性を排除し、冗長性及び拡張性を備える同期化システムを提供するためのSXOモジュールを提供する。

【解決手段】第1のバスから調整済み信号を受信し、共振器信号をステージ維持増幅器に渡す結晶共振器を含む結晶発振器ベースのモジュール。同期化範囲拡大回路が利得制御ネットワークと共振器の間に接続される。トライステートバッファがバッファを介して共振器信号を受信するように接続された主入力を有する。トライステートバッファの出力は、必要に応じて整合ネットワークを介して、第2のバスに接続される。上記モジュールを交互に2つのバスに接続することによって同期クロックシステムが形成されうる。また、トライステートバッファは制御入力も有しており、制御入力はホットスワッピングおよび他の便益を可能にするようにVccとグラウンドの間の遅延回路に接続されてもよい。

(もっと読む)

適応的遅延調整を有する位相補間器

【課題】参照信号と補間信号間の位相関係を確実に保持し、より小さく、より簡単な構成の装置を実現するために応用可能な位相補間器を提供する。

【解決手段】位相補間器は、2つの可調整遅延器30及び31、可調整遅延器30で遅延された信号と可調整遅延器31で遅延された信号との位相差を検出する位相比較器32、位相比較器32の出力を積分する積分器33、可調整遅延器30及び31の制御電圧を設定する乗算器34−1、34−2を備える。位相比較器32と積分器33を備えるフィードバックループは、可調整遅延器30の遅延量を制御し、{ACK1、ACK2}及びICK間の位相関係を確実に保持し、安定なICK位相を実現する。

(もっと読む)

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

クロックデータ再生回路

【課題】高速シリアルデータ転送の受信回路において、低消費電力モードから通常モードに復帰する際の復帰時間を短縮する。

【解決手段】シリアルデータ転送路から転送される同期用クロックを含むシリアルデータから同期用クロック及びデータを再生するクロックデータ再生回路であって、シリアルデータ及び基準クロックを電力モードに応じて選択してクロックデータ再生回路に供給する選択回路を具備する。

(もっと読む)

パルス無線受信装置および同期方法

【課題】NRZ符号化されたパルス信号に対しても同期可能であり、かつ従来のEarly/Late DLL方式に比べフィンガー数を削減したパルス無線受信装置および同期方法を提供する。

【解決手段】相対差算出手段1505は、最大値検出手段1551A、1551Bと最小値検出手段1552A、1552Bおよび加算手段1553A、1553B、1554を備える。最大値検出手段1551Aは、サンプル手段1504から入力される連続したn個のサンプル値1504Aから最大値を検出し最大値Amaxを出力する。同期制御手段1506は、相対差算出手段1505からの相対振幅差信号iVをもとに包絡線信号とク

ロック信号のタイミングが同期するように、クロック信号の位相を制御する遅延制御信号を生成し、遅延手段1503へ出力する。

(もっと読む)

無線装置

【課題】パルスの形状が変動しても、正確な波形サンプルが可能な無線装置を提供する。

【解決手段】入力信号とクロック信号を同期させる同期装置は、入力信号を、所定の間隔の第1と第2のサンプルタイミングでサンプルするサンプル手段102,103と、同期引き込み時に、第1と第2のサンプルタイミングをともにずらし、同期追従時に、第1と第2のサンプルタイミングの間隔を狭める遅延制御手段112とを備える。同期状態判定部105は位相誤差算出部104から出力された位相誤差量から同期しているか否かを判定し、遅延量制御部106に同期状態を出力する。遅延量制御部106は位相誤差算出部104から出力される位相誤差量と同期状態判定部105から出力される同期状態から、可変遅延器107および108に現在設定している遅延量の増減を制御する。

(もっと読む)

DLL回路

【課題】ジッタを小さくすることが可能なDLL回路を提供する。

【解決手段】各遅延回路UDCM0〜UDCMn+1を、第1及び第2インバータ15a,15b、第1及び第2ナンド回路16a,16b、スイッチングトランジスタ17及びトランスファーゲート18で構成するとともに、その第2ナンド回路16bを介して前段の遅延回路と後段の遅延回路とを接続するようにした。つまり、各遅延回路にて、1つの第2ナンド回路16bを介して、後段の遅延回路からの出力クロック信号を反転させて前段の遅延回路に出力した。詳述すると、各遅延回路は、その第2ナンド回路16b中の1個のトランジスタを駆動させて後段の遅延回路からの出力クロック信号を反転させて前段の遅延回路に出力する。

(もっと読む)

チャージポンプ回路及びこれを用いたPLL回路

【課題】PLL回路の応答特性を調整可能にし、更に、リファレンスリーク(キャリアリーク)を低減する。

【解決手段】位相比較器50内にパルス幅変更部70を設け、外部からセレクト信号SL1,SL2によりセレクタ73,76を切り替えることにより、アップ信号UP又はダウン信号DNのパルス幅を変更させ、チャージポンプ回路80の充電時間を調整することにより、PLL回路の反応特性を高める(不感帯を減少させる)。チャージポンプ回路80内にセレクト部90を設け、外部からセレクト信号SL1,SL2によりスイッチ91〜94を切り替えることにより、チャージ電流Icpによる出力電圧Vcpの持ち上がりによって起きるリファレンスリーク(キャリアリーク)を抑制し、これによってノイズ量を低減する。

(もっと読む)

遅延固定ループ装置

【課題】 1つのレプリカ遅延部を採用して外部クロックとデータまたは外部クロックと内部クロック間のスキューを補償する。

【解決手段】 遅延固定ループ装置は、レファレンスクロックをそれぞれ遅延させライジングクロックとフォーリングクロックとを生成し、レプリカディレイされたライジングクロックをレファレンスクロックに同期させ、フォーリングクロックをレファレンスクロックに同期されたライジングクロックに同期させる遅延手段と、レプリカディレイされたライジングクロックを提供するレプリカ遅延部と、ライジングクロックの同期を制御し、フォーリングクロックの同期を制御する制御手段と、遅延手段のライジングクロックをレプリカ遅延部へ伝達し、遅延手段で相互に同期された前記ライジングクロックとフォーリングクロックのパルス幅を調節して出力パルスを生成するDCC出力部とを含む。

(もっと読む)

ロックの喪失後にフェーズ・ロックド・ループをリセットするための回路

【課題】フェーズ・ロックド・ループ(PLL)回路内でリセット信号を発生するシステム及び方法を提供する。

【解決手段】リセット信号は、基準信号及びロック検出信号をリセット回路へ入力することにより発生される。PLL内のリセット回路は、一連の相互接続されたラッチ又はDフリップフロップを備え、これらを用いて遅延時間を生成する。遅延時間は、リセット信号がリセットを指示するのをリセット回路が待つ時間である。リセット回路はまた、或るパルス幅を有するリセット信号を発生する。このパルス幅は、一連の相互接続されたラッチにより決定される。リセット信号は、電圧制御発振器(VCO)又はPLL内の他の回路をリセットするため用いられ、また、PLLの外部にある回路によっても用いられ得る。

(もっと読む)

ロックフェイル防止のための遅延固定ループクロックの生成方法及びその装置

【課題】相対的に長時間パワーダウンモードにとどまる場合、チップの温度等の様々な環境の変化によってロックフェイルが発生することを防止する遅延固定ループ装置を提供すること。

【解決手段】本発明の遅延固定ループ装置は、パワーダウンモードへの出入を決定する制御信号を生成するパワーダウンモード制御部と、制御信号によりノーマルモードで外部クロックをバッファリングし第1の内部クロック信号を生成する第1のクロックバッファと、制御信号によりパワーダウンモードで外部クロックをバッファリングし第2の内部クロック信号を生成する第2のクロックバッファと、制御信号によりノーマルモードでは第1の内部クロック信号を選択し、パワーダウンモードでは第2の内部クロック信号を選択して伝達するクロック選択部と、クロック選択部で選択された信号を使用して位相更新を行うことによりDLLクロックを出力する位相更新部とを備える。

(もっと読む)

別途の比例経路を有するクロックデータリカバリループ

【課題】安定性の高いバンバンCDRループを提供すること。

【解決手段】本発明によるクロックデータリカバリループ(30)は、非線形(例えば、バンバン)位相検出器(311)、チャージポンプ(31)、RCループフィルタ(32)、および、信号生成器(例えば、電圧制御発振器(VCO)(33))を含む。データ速度が遅いときは、ループ(30)はチャージポンプ(31)と、安定な二次挙動を示すループフィルタ(32)とともに、動作され得る。このとき、ループフィルタ(32)の抵抗器Rは比例経路として機能する。また、別途の比例経路(312)も提供され、VCO(33)の制御入力に位相検出器(311)の出力を直接提供する。その間、ループフィルタ(32)の抵抗器Rもバイパスされる。データ速度の増加が、三次の影響を生じさせるとき、別途の比例経路(312)が二次挙動を維持するように活性化され得る。

(もっと読む)

位相制御回路

【課題】 本発明は、デジタルコードに対する位相変化の線形性を改善した位相制御回路を提供することを目的とする。

【解決手段】 位相制御回路は、第1のクロック信号の電流を流すよう機能する第1の端子と、第1の端子に結合される第1の複数のスイッチ回路と、第1の複数のスイッチ回路にそれぞれ結合される第1の複数の電流源と、第2のクロック信号の電流を流すよう機能する第2の端子と、第2の端子に結合される第2の複数のスイッチ回路と、第2の複数のスイッチ回路にそれぞれ結合される第2の複数の電流源とを含み、第1のクロック信号と第2のクロック信号とを重ね合わせるように第1の端子と第2の端子とが互いに結合されており、第1の複数の電流源のそれぞれの供給電流量のうち少なくとも1つが他とは異なり、第2の複数の電流源のそれぞれの供給電流量のうち少なくとも1つが他とは異なることを特徴とする。

(もっと読む)

位相同期回路及び半導体集積回路装置

【課題】動作周波数範囲を広げても、チップ上の占有面積、ゲート数、電力を増加させることなく、位相同期を短い時間で完了することが可能な位相同期回路を提供する。

【解決手段】遅延時間の異なる複数の遅延素子311,312,313,314を含み、第1のクロック信号103が入力される計測遅延列119と、その計測遅延列119に対応して複数の位相比較器109を含み、計測遅延列119からの信号及び第2のクロック信号104が入力され、第1のクロック信号103と第2のクロック信号104との遷移時間差を計測する位相比較器列121と、計測遅延列119に対応して遅延時間の異なる複数の遅延素子を含み、位相比較器列121からの信号及び第3のクロック信号105が入力される生成遅延列120とを有し、遅延素子のそれぞれの遅延時間は固定とする。

(もっと読む)

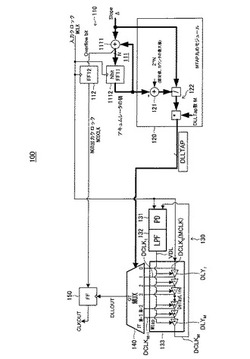

高速信号回路

【課題】 低速な同期信号を分配することによって、同期バスの動作周波数を高速に維持し、基板配線からの輻射ノイズへの対策を不要にする。

【解決手段】 各LSI2,3,4が備える内部クロック生成回路11,12,13は、内部クロックを発振する準備が完了すると、クロック同期信号生成回路14へ発振準備完了信号CLK_EN1,2,3を送信する。すると、クロック同期信号生成回路14は各LSI2,3,4へ低速のクロック同期信号SYNC_PULSEを送信する。これにより、各LSI2,3,4の内部クロック生成回路11,12,13は、クロック同期信号SYNC_PULSEに同期して、各水晶発振子8,9,10の信号を逓倍した高速のバスクロック信号CLK1,2,3を生成して共通の同期バス1へ送信する。従って、各LSI2,3,4が接続される同期バス1の動作周波数は高速のまま、信号線を流れるクロック同期信号SYNC_PULSEは低速となるので、基板からの輻射ノイズを低減することができる。

(もっと読む)

1 - 17 / 17

[ Back to top ]