Fターム[5J106LL07]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 同期・非同期検出回路 (13)

Fターム[5J106LL07]に分類される特許

1 - 13 / 13

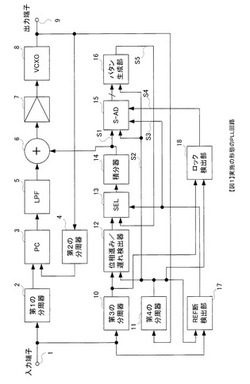

PLL回路

【課題】 基準周波数断時におけるフリーランの出力周波数の精度を向上させるPLL回路を提供する。

【解決手段】 比例積分方式のPLL回路を用いて、積分器14の後にA/D変換部15とパタン生成部16を付加した構成とし、A/D変換部15が、ロック時の積分器14の出力電圧をデジタル信号として得て、ロック外れ時はロック時のデジタル信号を保持する機能を備え、ロック外れ時で基準周波数断時には、保持したデジタル信号に応じてパタン生成部16がパタン生成し、セレクタ13によって積分器14に出力するものであり、基準周波数断時には、パタン生成の波形を積分器14に代替入力するPLL回路である。

(もっと読む)

PLL回路、DLL回路

【課題】基準クロック信号と比較対象となるクロック信号の両者の位相を比較する位相比較器から位相差信号が出力され続けるPLL回路又はDLL回路にあって、両信号の同期を適切に検出して低ジッタ動作を実現する。

【解決手段】同期判定回路(15)は、基準クロック信号(R)の位相を基準として帰還クロック信号(V)の位相が進相又は遅相であるかを検出し、両信号の位相差の期間、進相検出信号(DOWN)又は遅相検出信号(UP)を出力する進相及び遅相検出部(158)と、進相検出信号(DOWN)が出力されている期間、初期値からの計数を開始する進相期間計数部(155)と、遅相検出信号UPが出力されている期間、初期値からの計数を開始する遅相期間計数部(156)と、進相期間計数部又は遅相期間計数部の計数値が第1の規定値に到達しない回数が第2の規定値を上回ったとき、位相同期検出信号(P_DET)を出力する位相同期判定部(157)と、を備える。

(もっと読む)

アンロック検出回路

【課題】2つの信号間の位相差の発生を正確に検出するアンロック検出回路を提供する。

【解決手段】アンロック検出回路は、論理値を基準信号の変化に応じて記憶する第1フリップフロップと、論理値を入力信号の変化に応じて記憶する第2フリップフロップと、当該第1及び第2フリップフロップの出力の否定論理積を算出するNAND回路とを備えた位相比較器と、第1フリップフロップの出力を基準信号の変化に応じて記憶する第3フリップフロップと、第2フリップフロップの出力を入力信号の変化に応じて記憶する第4フリップフロップとを備えた第1アンロック検出器と、NAND回路の出力を基準信号の変化に応じて記憶する第5フリップフロップと、NAND回路の出力を入力信号の変化に応じて記憶する第6フリップフロップとを備える第2アンロック検出器と、第3、第4、第5及び第6フリップフロップの出力の論理和を算出するOR回路とを具備する。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

クロックデータ修復回路

【課題】本発明は、誤同期状態から正常な同期状態へ復帰することが可能なクロックデータ修復回路を提供することを目的とする。

【解決手段】本発明の1つの実施形態は、位相検出部2と、クロック信号生成部と、出力部と、追い越し検知部8とを備えるクロックデータ修復回路である。位相検出部2は、入力データから位相情報を取得し、クロック信号生成部は、位相情報に基づき、複数のクロック信号を生成し、出力部は、入力データと、クロック信号生成部で生成した複数のクロック信号のうち選択したクロック信号とを出力する。追い越し検知部8は、選択したクロック信号が入力データを位相的に追い越しているか否かを検知し、当該検知に基づき選択したクロック信号をクロック信号生成部で生成した他のクロック信号に切り替えるように制御する。

(もっと読む)

アンロック信号検出方法

【課題】

解決しようとする課題は、PLL回路において周期的及びバースト的に生じるアンロックの検出を正確に行い、また、周囲温度の変化にも柔軟に対応することができるディジタル信号回路の中核となるクロック系及び無線部の搬送周波数の基準となる周波数の異常を正確に判断することを可能にすることである。

【解決手段】

PLL回路におけるアンロック検出方法であって、予め定められた周期でサンプリングし、アンロックであればカウンタでカウントアップし、予め定められた周期回数でカウントアップした値と予め定められたしきい値を制御部で比較し、カウントアップした値が予め定められたしきい値を超えている場合にアラーム信号を出力すること実現した。

(もっと読む)

アンロック検出回路及びクロック発生システム

【課題】アンロックを検出する位相差を制御し任意の感度でアンロックの検出を行う。

【解決手段】PLLのアンロック状態を検出するアンロック検出回路に、PLLへの基準信号、PLLからのフィードバック信号のデューティ比を調整する1対のデューティ調整回路111,112と、デューティ調整回路からデューティ調整後の基準信号、フィードバック信号をクロック信号として論理値を記憶する第1のフリップフロップ回路121,122と、第1のフリップフロップ回路の出力信号の論理積を取り記憶した論理値をリセットするAND回路123と、デューティ調整回路からデューティ調整後の基準信号、フィードバック信号を反転しクロック信号として第1のフリップフロップ回路の出力信号をサンプリングし論理値として記憶する第2のフリップフロップ回路124,125と、第2のフリップフロップ回路の出力信号の論理和をとりアンロック信号として出力するOR回路126とを備える。

(もっと読む)

位相同期ループ回路での周波数検出器及び周波数エラーの検出方法

【課題】 位相同期ループ回路において周波数エラーを高速で検出できる周波数検出器及び周波数エラーの検出方法を提供する。

【解決手段】 予測されたランレングス信号の予測分布度に基づいて、周波数検出周期の間にサンプルされたRF信号からランレングス信号を検出するランレングス信号検出ユニットと、周波数検出周期の間に、検出されたランレングス信号をカウントする少なくとも一つのカウンタを備えたカウンタユニットと、サンプルされたRF信号のパッシングエッジをカウントして、周波数検出周期を制御するエッジカウンタと、カウンタユニットに含まれたカウンタによりカウントされた値及び所定の基準値を利用して、周波数検出周期の間の周波数エラーを生成する周波数エラー生成ユニットとを備える。

(もっと読む)

PLLのロック検出回路

【課題】PLLの動作に影響を与えることなく、その回路規模が小さく、設計の検証も容易で、ロック状態の判定精度を適宜設定することができるPLLのロック検出回路を提供する。

【解決手段】ロック検出回路は、PLLに入力される入力クロックおよびフィードバッククロックを各々分周した第1および第2の分周クロックを出力する第1および第2の分周回路と、第1および第2の分周クロックを比較し、両者の間の位相差に相当する位相差出力信号を出力する比較回路と、2以上の所定のカウント数まで、第1の分周クロックをカウントして、所定パルス幅のカウント信号を出力するカウンタと、位相差出力信号が出力されない状態で、前記カウント信号が所定数入力されるとロック検出信号を出力する検出回路とを備える。

(もっと読む)

ディジタルPLLのロック状態判定回路

【課題】 反転間隔の長い信号及び短い信号が入力されるディジタルPLLのロック判定を確実に行うことのできるロック状態判定回路を実現することにある。

【解決手段】 PLLの入力信号を、ディジタル制御発振器25からの出力信号により標本化した離散値により入力し、ディジタル制御発振器25の発振周波数の繰返しで得られる離散値の信号レベルが、予め設定される閾値の範囲にあるか否かを電圧比較手段311により検出し、検出した電圧を電圧比較手段311により閾値の範囲外であるとして検出されるときには正の第1の数を、範囲内として検出されるときには負の第2の数をセレクタ312により割り付け、割り付けた数を累積手段321で加算累積し、累積数の大きさに応じPLL2がロック状態にあるか否かをロック判定手段323により判定するようにしてディジタルPLLのロック状態判定回路を実現した。

(もっと読む)

PLL回路およびPLL回路の発振動作制御方法

【課題】設計者の負担軽減を図るとともに発振動作の高性能化を実現すること。

【解決手段】PLL回路100は、印加された電圧に応じた発振信号Xを出力する電圧制御発振器(VCO)114を有する。PLL回路100は、検知部120により、VCO114から出力された発振信号Xの周波数を検知して、当該周波数に応じた検知信号OSCを出力する。また、検出部130により、検知信号OSCに基づいて、発振信号Xの異常発振状態を検出する。生成部140は、状態検出信号CHに基づいて、VCO114の出力動作のリセットをおこなうリセット信号S1を生成し、VCO114に出力する。これにより、VCO114から出力された発振信号Xの異常発振状態を自動的にリセットすることができる。

(もっと読む)

PLLクロック出力安定化回路

【課題】源振クロックで所定サイクル毎に周波数を測定することで、PLL回路が安定したことをLSI内部等で検査可能にする。

【解決手段】PLLクロック出力安定化回路は、基準クロックclkを固定又は可変の逓倍数Nで逓倍してPLLクロックpll_clkを出力するPLL回路10と、一定期間の間、前記PLLクロックpll_clkでカウントアップするカウンタ17と、カウンタ17のカウント値と固定又は可変の逓倍数Nとを比較する比較回路18と、一定期間の間、比較回路18の比較値の等しい状態が続いた回数だけカウントアップするカウンタ20と、カウンタ20のカウント値が安定待ち回数kに達したときに出力イネーブル信号enableを生成し、出力イネーブル信号enableにより、PLLクロックpll_clkを遮断していたゲート回路25を開いてPLLクロックpll_clkを通過させる出力手段とを備えている。

(もっと読む)

1 - 13 / 13

[ Back to top ]