Fターム[5J106RR03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 外部応用回路との結合 (24)

Fターム[5J106RR03]に分類される特許

1 - 20 / 24

半導体集積回路

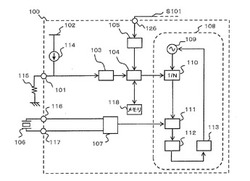

【課題】単一の回路仕様で世界各国の衛星放送に簡便に対応できる、LNB用半導体集積回路を実現する。

【解決手段】半導体集積回路100の所定の端子電圧を設定することで、PLL回路108の可変分周器110の分周比を設定し、所望の局部発振周波数を得る。供給される直流電位に対応して可変分周器の分周比を制御する第1の分周比設定部と、供給されるパルス信号の有無に対応して可変分周器の分周比を制御する第2の分周比設定部とを備え、第1の分周比設定部または第2の分周比設定部による可変分周器の分周比制御により、局部発振器109の発振周波数を所望の周波数に設定する。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

PLL回路

【課題】VCOを切り替えて使用するPLL回路において、位相雑音を減らすことである。

【解決手段】複数のVCO22a〜22nの内の1つを選択する際に、選択可能な複数のVCO内で、発振周波数帯域の最も低いVCOを選択する。これにより、位相雑音の小さいVCOを使用することができる。

(もっと読む)

基準クロック信号生成装置

【課題】

デジタル映像信号処理で必要となる所定周波数の基準クロック信号を得る手法として、ジッター発生要因を有する手法を用いた場合でも、このジッターに起因する画質劣化や音質劣化を出来る限り目立たなくすることを可能とする装置を提供する。

【解決手段】

映像信号や音声信号の信号レベルが低い期間か否かを検出し、信号レベルが低くない期間は、クロック信号を生成するPLL回路の構成要素である帰還分周器5の分周比率を固定値とし、信号レベルが低い期間は、帰還分周器5の分周比率を可変して、これら各期間よりも十分に長い期間で積分すると、全体的にみれば所定周波数となる基準クロック信号を生成する。

(もっと読む)

シンセサイザまたは発振器モジュールと、このシンセサイザを用いたシンセサイザモジュール、受信装置、及び電子機器、ならびに分周器の分周比の制御方法

【課題】制御部による分周器の制御に起因したノイズの発生を抑え、受信特性の良好な受信機を実現可能なシンセサイザを提供することを目的とする。

【解決手段】制御部7は、温度を検出する温度検出部8の出力信号に基づいて第2の分周器6へ適当な整数分周数Mや分数分周数Nの制御信号を送り、第2の分周器6の分周比を変化させる。つまり、第2の分周器6は、分周数Mが入力される整数部分と、分周数Nが入力される分数部分により構成される。制御部7は、温度を検出する温度検出部8の温度信号に基づいて第2分周器6の分周比を不均一な時間間隔で変化させる。これにより、第2分周器6の制御に伴い特定周波数に多数発生するノイズを抑圧することができ、シンセサイザの位相雑音を低減することができる。

(もっと読む)

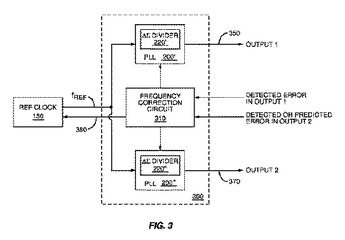

多出力周波数シンセサイザにおける周波数制御のための装置と方法

共通の基準周波数信号に位相同期した2つ以上の信号を合成(シンセサイズ)するための方法と回路とを開示する。1つの実施例では、その方法は、第1と第2の位相同期ループ回路(200′,200″)を使用して、基準クロック信号に位相同期する第1と第2の出力信号(350,370)を生成する工程を備える。第1の出力信号において検出された周波数誤差に応じて、第1の出力信号(350)は、第1の位相同期ループ回路における周波数分周比を調整することにより補正される。第2の出力信号(370)は、検出した周波数誤差から算出される調整パラメータを使用して、第2の位相同期ループ回路における周波数分周比を調整することにより、第1の出力信号への補正とは別個に補正される。別の代表的な方法では、第1と第2の出力信号は、第1と第2の位相同期ループ回路を使用して、上述したように生成される。第1の出力信号において検出された周波数誤差に応じて、第1の位相同期ループ回路における周波数分周比を調整し、制御信号(360)を生成して基準クロック信号の周波数を調整することにより、第1の出力信号が補正される。第2の出力信号(370)は共通の基準クロック信号から導出されるので、基準クロック周波数(FREF)に対する調整はまた、第2の出力信号の周波数も調整するであろう。いくつかの実施例においては、第2の位相同期ループ回路における周波数分周比を調整することにより、第2の出力信号(370)に対する付加的な調整を施すことができる。記述した方法を実施するための回路もまた開示される。  (もっと読む)

(もっと読む)

信号分配装置

【課題】分周器の広帯域かつ低電圧動作を保障する。

【解決手段】信号分配装置は、第2制御信号に従って動作し、参照周波数に従って発振周波数を調整する調整部を有する位相同期ループ回路101と、電流源負荷を有し、前記調整部によって調整された発振周波数を分周してI/Q信号を生成する分周器102と、第1制御信号に従って自走発振周波数を生成する自走発振周波数生成器105と、前記参照周波数と前記自走発振周波数を比較する比較部103A及び前記比較部103Aの比較結果に従って前記第1制御信号又は前記第2制御信号を生成する制御部103Bを有する自走発振周波数制御回路103と、前記分周器102によって生成された前記I/Q信号を用いて送信又は受信を行う通信回路104と、を備えている。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

同期掃引シンセサイザ

【課題】 本発明は、スタート周波数からストップ周波数まで、階段状に周波数を高速変化させ、且つスイープタイミングに同期した同期パルスを出力することができる同期掃引周波数シンセサイザを提供する。

【解決手段】 電圧制御発振器11が、位相比較制御部でロックが検出されるまでは、特定のスタート周波数を提供し、ロックが検出された後は、階段波形となるスイープ周波数を提供し、位相比較制御部が、スイープのタイミングに同期した掃引同期パルスを出力する同期掃引周波数シンセサイザとしている。

(もっと読む)

フィルタ装置およびそれを有する送受信機

【課題】任意の基準信号周波数により所望のフィルタ帯域特性を得ることができ、そのフィルタ帯域を可変することができるフィルタ装置およびそれを用いた送受信機を提供する。

【解決手段】信号を処理するフィルタ13と、フィルタ13の周波数特性を所定の特性に調整するフィルタ調整回路16aと、フィルタ調整回路16aに基準信号を供給する基準信号源とを備える。この基準信号源は、周波数シンセサイザ20であり、周波数シンセサイザ20は、フィルタ調整回路16aがフィルタ13の調整を行う際に、フィルタ調整回路16aに必要な周波数で発振した発振信号を出力し、発振信号をフィルタ調整回路16aの基準信号として用いる。

(もっと読む)

複数の通信システムのための基準信号生成

【課題】複数の通信システムのための基準信号を生成する技術について説明する。

【解決手段】装置は基準発振器、周波数制御部及び複数の周波数シンセサイザを含む。基準発振器は、水晶発振器または他のある形式の発振器であり、主基準信号を生成する。周波数制御部は、主基準信号の周波数誤差を推定し、周波数誤差推定値を出力する。複数の周波数シンセサイザは、主基準信号を受け取り、複数のシステムのための複数のシステム基準信号を生成する。少なくとも一つの(例えば各々の)周波数シンセサイザは、周波数制御部からの周波数誤差推定値に基づいて主基準信号の周波数誤差を補正する。各周波数シンセサイザは、位相同期ループ(PLL)のための分周器制御信号を生成するために使用されるシグマ・デルタ変調器を含む。分周器制御信号は、主基準信号の周波数誤差を補正する。

(もっと読む)

シンセサイザモジュール

【課題】 周波数設定者の利用形態に応じて発振周波数の設定を容易できるシンセサイザモジュールを提供する。

【解決手段】 CPU10は、ロータリーSW11の状態を判断し、ロータリーSW11で設定されたCH番号が有効な値であれば、スイッチによる周波数設定を行い、有効な値でなければ、パワーオフ直前の最終設定周波数を再設定し、その後にシリアルバス13から入力されたシリアル信号による周波数設定を行うものであり、ロータリーSW11による設定とシリアル信号による設定をぶつかることなく周波数設定者の利用形態に応じて適正に行うことができるシンセサイザモジュールである。

(もっと読む)

高周波信号発生装置

【課題】数MHzから数GHzの周波数領域にわたる高周波信号を、非常に低いSSBノイズで安定して発生することができる高周波信号発生装置を提供する。

【解決手段】搬送波周波数f1の1/nにほぼ相当する第1高周波信号aを発振する高周波発振器11と、搬送波周波数f1にほぼ相当する第2高周波信号eを発振する電圧制御発振器15と、電圧制御発振器15の出力周波数fを1/nに分周する分周回路16と、第1高周波信号aと出力周波数fの1/nの第2高周波信号gの位相差に比例した誤差信号Veを出力する位相比較器12と、誤差信号Veに応じて制御電圧を電圧制御発振器15に入力するVCO制御回路13とを備え、VCO制御回路13は、SSBノイズが第1高周波信号aの方が第2高周波信号eのものより小さい周波数帯域では、誤差信号Veに比例する制御電圧を出力し、大きい周波数帯域では制御電圧を0にする。

(もっと読む)

クロック変換回路

【課題】クロック変換時の収束時間を短縮し安定性を向上する。

【解決手段】位相比較部10は基準クロックをカウントした基準クロックカウンタ値と、供給された再生クロックステップ値を加算して再生クロックのタイミングでラッチした再生クロックステップ値加算結果との位相比較を行い、位相誤差を検出する。ループフィルタ11は検出された位相誤差を平滑化し位相誤差に対応した電圧値を出力する。電圧制御発振部12はループフィルタ11により出力された電圧値により再生クロックを生成する。

(もっと読む)

FM変調装置

【課題】基準周波数の制御電位をモニターし、モニターした制御電圧に直接変調をかけ、任意の時間に渡り安定した被変調波を生成し、その被変調信号を所定の偏差内の送信チャネル周波数に逓倍して送信を行うことができるFM変調装置の提供を目的とする。

【解決手段】基準周波数を発振し、且つ第1被変調信号を生成する基準信号部10と、基準信号部10の基準周波数を制御する制御電圧をモニターし、モニターした制御電圧を変調信号に加算し、その加算信号を基準信号部10に出力する制御部30と、基準信号部10において加算信号により生成された第1被変調信号と、制御部30から出力される制御信号とを入力して、第2被変調信号及び第3被変調信号を生成するメインPLL部20とから成る。

(もっと読む)

半導体装置

【課題】高速動作する複数の回路ブロック間で同時に割り込み処理をおこなう場合のタイミング設計を容易化し、回路規模・消費電力を低減する。

【解決手段】クロック信号発生回路5と、クロック信号clkに同期して動作する複数の回路ブロック6とを有し、複数の回路ブロックのそれぞれは、周波数引き込み過程のクロック信号に同期して出力した割り込み信号reset_inを受けてリセット処理を行う。

【効果】タイミングマージンを大幅に向上させる。

(もっと読む)

多重周波数源システム及び動作方法

多重周波数源システムが、既定の目標周波数に同調可能な少なくとも1つの周波数源と、目標周波数より高い、又は低い周波数の第2の信号を生成するように動作する少なくとも1つの追加周波数源を含む。同調可能周波数源を、第2の信号の同時生成の間に目標周波数に同調させる方法は、(i)第2の信号の周波数が目標周波数より高いときに、同調可能周波数源を、目標周波数より低い少なくとも1つの周波数点周波数に同調するように制御し、その後、発振器を目標周波数に同調するように制御すること、又は(ii)第2の信号の周波数が目標周波数より低いときに、同調可能周波数源を、目標周波数より高い少なくとも1つの周波数点に同調するように制御し、その後、同調可能周波数源を、目標周波数に同調するように制御することを含む。 (もっと読む)

クロック発生装置及び半導体集積回路装置

【課題】 高速動作メモリを用いる場合であっても拡散スペクトル・クロック信号を用いて、EMIを効果的に低減することができるクロック発生装置及び半導体集積回路装置を提供する。

【解決手段】 拡散スペクトル・クロック発生器210は、DDR SDRAM112Aの連続アクセスを判定し、DDR SDRAM112Aのデータ読み出し時の連続アクセスでは拡散OFFにする状態判定器220を備える。

(もっと読む)

1 - 20 / 24

[ Back to top ]