Fターム[5J106RR21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 同期検出手段 (14)

Fターム[5J106RR21]に分類される特許

1 - 14 / 14

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

局部発振器を調整する装置及び方法

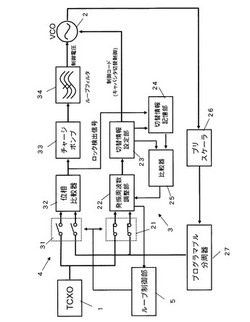

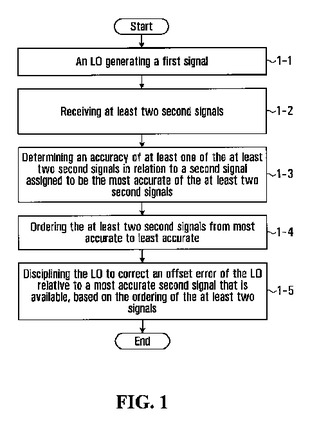

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、少なくとも2つの入力を有する優先制御部とを有し、入力の各々は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号をそれぞれ受信し、優先制御部は、少なくとも2つの第2信号の内の少なくとも1つの第2信号の精度を判定し、何れかの第2信号は少なくとも2つの第2信号の内で精度が最高であるように指定され、優先制御部は、最高精度から最低精度へ少なくとも2つの第2信号を順番に並べ、少なくとも2つの第2信号の順番に基づいて、装置に利用可能な最高精度の第2信号に対してLOのオフセットエラーを補正するように、LOが調整される。  (もっと読む)

(もっと読む)

局部発振器を調整する装置及び方法

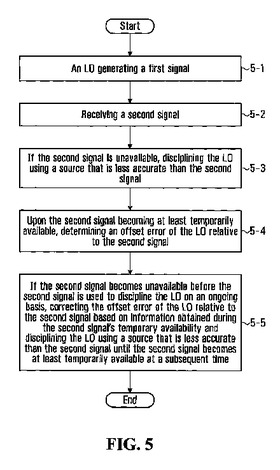

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

同期掃引シンセサイザ

【課題】 本発明は、スタート周波数からストップ周波数まで、階段状に周波数を高速変化させ、且つスイープタイミングに同期した同期パルスを出力することができる同期掃引周波数シンセサイザを提供する。

【解決手段】 電圧制御発振器11が、位相比較制御部でロックが検出されるまでは、特定のスタート周波数を提供し、ロックが検出された後は、階段波形となるスイープ周波数を提供し、位相比較制御部が、スイープのタイミングに同期した掃引同期パルスを出力する同期掃引周波数シンセサイザとしている。

(もっと読む)

位相同期回路、同期検波回路および放送受信装置

【課題】簡易な構成で入力信号と同一周波数、同一位相の再生信号を出力すること。

【解決手段】位相同期回路1は、VCO13、混合器11、LPF12からなる第1のフィードバックループで周波数を合わせ、第1のフィードバックループで得られた制御信号をVCO23、混合器21、LPF22、加算器24からなる第2のフィードバックループに供給することで、第2フィードバックループから周波数と位相がともに入力信号と同一な再生信号を出力する。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

PLL回路

【課題】直列接続されたPLL回路について、特にリセット時や電源投入時における異常なクロック信号の発生を抑制する。

【解決手段】直列接続された二つのPLL回路(10A,20)からなるPLL回路において、前段のPLL回路(10A)は、出力クロック信号を生成する電圧制御発振器(104)、及び電圧制御発振器(104)に入力される制御電圧が所定の範囲にあるか否かを検出し、当該検出結果を示す検出信号を出力する制御電圧検出回路(106)を備えている。後段のPLL回路(20)は、前段のPLL回路(10A)から出力された検出信号が第1の論理レベルのとき、停止する一方、当該検出信号が第2の論理レベルのとき、動作する。

(もっと読む)

1 - 14 / 14

[ Back to top ]