Fターム[5J500AA35]の内容

Fターム[5J500AA35]に分類される特許

1 - 15 / 15

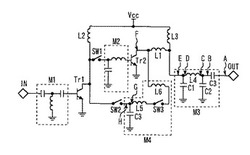

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3が接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M4の一端がスイッチSW2の他端に接続され、整合回路M4の他端が増幅素子Tr2の出力に直接に接続されている。

(もっと読む)

高周波増幅器

【課題】熱抵抗が下がり高周波増幅器全体の放熱性能が向上する高周波増幅器を提供する。

【解決手段】高周波増幅器10は、複数のトランジスタセル1a−1gで構成され、平面上に配置されている複数のトランジスタセル1a−1gのうち隣接している2つの各トランジスタセルにおけるx軸方向の各中心はy軸方向にずれている。

(もっと読む)

分布形増幅器

【課題】利得の低下を防止して、高利得、高出力、高効率及び広帯域特性を実現することができる分布形増幅器を得ることを目的とする。

【解決手段】並列に接続されている複数のトランジスタ1a〜1jと、複数のトランジスタ1a〜1jに対して入力側バイアス電圧を供給する電圧源2と、複数のトランジスタ1a〜1jに対して出力側バイアス電圧を供給する電圧源5,7とを備え、電圧源5,7から複数のトランジスタ1a〜1jに供給される出力側バイアス電圧のうち、トランジスタ1aに供給される出力側バイアス電圧が、トランジスタ1b〜1jに供給される出力側バイアス電圧と異なるように構成する。

(もっと読む)

スイッチング回路、分布定数型のスイッチング回路、及び包絡線信号増幅器

【課題】単一のスイッチング素子でインンダクタンス素子をスイッチングすることにより、半導体材料がシリコン又はガリウム砒素からなるスイッチング素子を用いたプッシュプルの増幅器よりも高周波且つ大電力の増幅が可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】スイッチング回路33aは、炭化珪素(SiC)を半導体材料とするn個のトランジスタ(FET)M1,M2,・・MnのゲートをコイルL1を介して縦続接続する入力側伝送線路と、各トランジスタM1,M2,・・MnのドレインをコイルL2を介して縦続接続する出力側伝送線路とを備える。入力端331から与えられて入力側伝送線路を伝播するPWM信号によってトランジスタMm(mは1からnまでの整数)を順次オンさせ、トランジスタMmのドレインに流入する電流と、出力側伝送線路を出力端332の方向に伝播する電流とを加算する。

(もっと読む)

広帯域ESD保護を与える方法とそれにより得られる回路

【課題】伝送ラインや分布増幅器などの分配電子回路を開示する。

【解決手段】本発明は、インプットターミナル(2)と、アウトプットターミナル(3)と、電力供給ライン(4、5)と、インプットターミナル(2)とアウトプットターミナル(3)との間に設けられ一つのセクションから別のセクションへ電気信号を伝送するように配置された一連セクション(61、62、63、64、65)とを含み、個々のセクション(61、62、63、64、65)は、電子放電静電(ESD)イベントの発生の際に対応するESD電流を電力供給ライン(4、5)に運ぶように構成されたESD保護(9)を含み、個々のセクション(61、62、63、64、65)のESD保護要素(9)は、ESDイベントの発生の際に、最初のセクション(61)の前に後続のセクション(62、63、64、65)が起動されるように選択されている分配電子回路である。

(もっと読む)

ドライバ回路

【課題】出力振幅を低減した際の出力波形品質の劣化を抑圧する。

【解決手段】ドライバ回路は、出力信号の振幅を調整可能な振幅可変増幅器VAと、少なくとも1つの増幅器DIFFaから構成される増幅回路とを備える。振幅可変増幅器VAは、入力信号DINP,DINNが入力される増幅用トランジスタを含む増幅部と、増幅用トランジスタとカスコード接続された振幅調整用トランジスタを含み、振幅調整用トランジスタに入力される振幅調整信号に応じて増幅用トランジスタの出力信号の振幅を調整する振幅調整部と、増幅部および振幅調整部に定電流を供給する電流源とから構成される。増幅器DIFFaは、振幅可変増幅器VAの出力信号を入力とする増幅用トランジスタを含む出力部と、この出力部に定電流を供給する電流源とから構成される。

(もっと読む)

高周波増幅器

【課題】反射特性や利得特性の劣化を小さくすることができる高周波増幅器を得ることを目的とする。

【解決手段】入力端子1から入力された信号を増幅する複数のトランジスタ9のドレイン側と接続されている複数のショートスタブ12と、出力側伝送線路6と並列に接続されている複数の容量10とを備え、複数のショートスタブ12における何れかのショートスタブ12にドレインバイアス端子13を接続するように構成する。これにより、反射特性や利得特性の劣化を小さくすることができるとともに、レイアウトの自由度を高めることができる。

(もっと読む)

分布型環状電力増幅器の構造

【課題】増幅されるRF信号の電力出力を効率的及び経済的に増加させる、分布型電力増幅器のトポロジー及びデバイスを提供する。

【解決手段】電力増幅器は、新規の環状で相互に接続された複数のプッシュプル増幅器を具えており、等しい大きさ及び逆相の入力信号で駆動される隣接する増幅デバイスの信号入力を有する能動素子の1次巻線として機能することが好ましい。また、そのトポロジーは、1次巻線の形状に適合する2次巻線150の使用と、個々の電力増幅器の電力を効率的に合成する働きをする変化に適応する変化を開示している。新規の構造は、RF、マイクロ波、ミリ波の周波数で低コストで、高集積で、ハイパワーである増幅器のデザインを可能としている。

(もっと読む)

分布型増幅器

【課題】 広帯域・高出力特性が得られ、かつ入力反射特性に優れた分布型増幅器を提供する。

【解決手段】 順次直列に接続される複数の伝送線路と、この複数の伝送線路を介して伝播された入力信号がゲート電極に入力される複数のFETを備え、入力信号の増幅を行う分布型増幅器であって、

複数の前記伝送線路の入力端子に直列にカットオフ周波数を基準として低周波数側では直列に抵抗が挿入され、高周波数側ではショートした特性を示すイコライザ回路を備えると共に、このイコライザ回路と直列にカットオフ周波数以上の周波数においてインピーダンス整合を行う入力側無損失整合回路を備える。

(もっと読む)

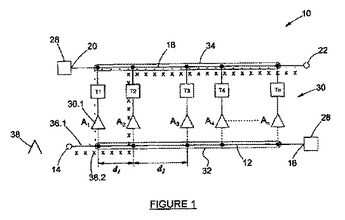

分散型低雑音増幅器

分散型低雑音増幅器(DLNA)(10)は少なくとも、増幅器の入力(14)から増幅器の出力(22)までの第1パス(36.1)を形成する第1増幅部(30.1)と、上記入力(14)から上記出力(22)まで第2パスを形成する第2増幅部(30.2)とを備える。上記第1パスおよび上記第2パスのそれぞれは、異なる位相の変化と関連付けられる。上記第1パスに沿って伝搬する、増幅器構成によって生成される雑音と、上記第2パスに沿って伝搬する、増幅器構成によって生成される雑音との間の位相差、及び、DLNAの出力(22)の前における雑音の相殺的干渉を発生させ、これによって雑音抑制帯域における雑音を抑制するために、上記差は雑音抑制帯域における周波数について30度よりも大きい。増幅部(30.1)から(30.n)における各ゲインは、上記増幅器(10)の上記入力(14)から上記出力(10)までの方向に減少し得る。  (もっと読む)

(もっと読む)

分布型電力増幅器

【課題】高周波電力増幅器における渦電流損失を、回路占有面積を増大させることなく低減する。

【解決手段】2つのゲインブロック(3aa,3ab−3da,3db)が各々に接続される1次インダクティブパス(2a−2d,4a−4d)および1次インダクティブパスと磁気結合する2次インダクティブパスに屈曲部(5)を設け、この屈曲部が中心を向くように配置する。2次インダクティブパス(4a−4d)を、順次配線(11a−11c)により相互接続し、未接続の2次インダクティブパス端部を出力端(15a、15b)として利用する。

(もっと読む)

分布型電力増幅器

【課題】分布型環状増幅器の出力波形歪を低減する。

【解決手段】環状に配置されるプッシュプル増幅段(PAS0−PAS3)において、一次側スラブ型トランスとして確保された領域(1a,1b)と交差しないように二次側トランスから出力を取出す。

(もっと読む)

増幅器及び差動型分布増幅器

【課題】マッハツェンダ型LN光変調器を駆動するための増幅器等として使用される増幅器に関し、高利得特性を持ち、かつ、出力段の差動型分布増幅器の入力側動作バイアスポイントを容易に調整できるようにする。

【解決手段】ソースフォロア回路部68には電流源を設けず、ソースフォロアトランジスタ11、14のソースを本発明の差動型増幅器の第1実施形態69の入力端子18、19に接続する。差動型増幅器69の入力側伝送線路20、21の終端抵抗22、23の接続点25にソースフォロア回路部68に必要な電流源70を接続する。

(もっと読む)

分布型増幅器

【課題】 設計性及び製造性に優れた高周波数帯域を有する分布型増幅器を提供する。

【解決手段】 カスコード型トランジスタを構成するゲート接地トランジスタ11のゲート端子を、伝送線路LgAと抵抗RgAからなる直列回路を介して高周波接地用キャパシタCgAに接続するとともに、伝送線路LgBと抵抗RgBからなる直列回路を介して高周波接地用キャパシタCgBに接続するようにして、伝送線路LgA、LgBの伝送線路長及び抵抗RgA、RgBの抵抗値に対する回路性能の感度を従来と比較して低下させて伝送線路長及び抵抗値の変化に対する回路特性への影響を低減し、伝送線路及び抵抗における設計マージン及び製造マージンを拡大する。

(もっと読む)

アクティブ・バイアスを使用したMMIC分布増幅器ゲート制御

電気回路が形成されているウェハ上にアクティブ・バイアス(10)が形成され、電気回路に追加的に印加される入力信号に印加されるバイアス電圧(Vout)を生成する。具体的には、アクティブ・バイアス(10)は、少なくとも1つのトランジスタを備え、電気回路に影響を及ぼすウェハ・ロット変動がアクティブ・バイアスの特性に対し相応して影響を及ぼすように、電気回路を形成するトランジスタ(10)と同型であることが好ましい。アクティブ・バイアス(10)は、ドレインが電気回路の出力に電気的に接続された1つの電界効果トランジスタ(10)を備える。加えて、ドレインはトランジスタのゲートに電気的に接続される。この点において、トランジスタ(10)を流れる電流は、トランジスタ(10)のドレインおよびトランジスタのゲートにそれぞれ電圧(Vout)を生成する。この電圧(Vout)は次いで、電気回路にバイアス電圧として印加される。この回路で、トランジスタ(10)を流れる電流はウェハ・ロット変動のため変動し、その結果、電気回路に印加されるバイアス電圧(Vout)が相応して変化する。アクティブ・バイアス(10)はさらに追加トランジスタを備えることができ、各トランジスタ(10)のチャネルは他のトランジスタのゲートに電気的に接続される。この点において、トランジスタを流れる電流は、トランジスタが流れる電流を過度に増減させるのを防止するために相互に調整される。  (もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]