Fターム[5J500AA46]の内容

Fターム[5J500AA46]に分類される特許

1 - 20 / 26

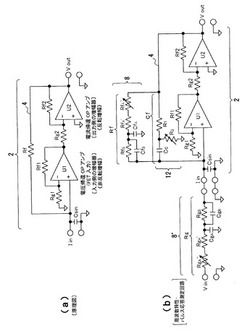

増幅回路および帰還回路

【課題】反転入力容量Csinが異なる場合、帰還容量Cfが小容量の固定値であっても、周波数特性の肩特性の劣化やピークがほとんど生じない増幅回路および帰還回路を提供する。

【解決手段】個別に負帰還をかけるとともに直列に接続された複数の増幅器と、前記複数の増幅器に含まれる出力側の増幅器の出力側と入力側の増幅器の入力側に接続された帰還手段(帰還回路)とを備え、前記複数の増幅器は奇数個の反転増幅器を含む構成である。

(もっと読む)

抵抗素子及び反転バッファ回路

【課題】無駄な電流や信号の歪みを発生させることなく、抵抗素子層の周辺の半導体基板や、抵抗素子層の上部を通過する電源線、信号線等の電位によって抵抗値が変化するのを抑えることのできる抵抗素子及び反転バッファ回路を提供する。

【解決手段】抵抗素子10は、半導体基板14上に、第1の電極11及び第2の電極12を有する抵抗素子層13が形成されている。第1の電極11の電位によってバイアスされた第1の導電層15と、第2の電極12の電位によってバイアスされた第2の導電層16とで、抵抗素子層13の下部が均等に覆われている。このように、両端をバイアスされた抵抗素子層13の下部又は上部の少なくとも一方を覆う第1の導電層15及び第2の導電層16によって、抵抗素子層13の周辺の半導体基板14等との電圧差による抵抗値の変化を相殺することで、抵抗値の変化を抑える。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

ダイナミックバイアスを有するRFバッファ回路

電圧制御発振器(VCO)に対するRFバッファ回路は、出力電圧波形の位相を選択的にフリップするために、ダイナミックバイアス回路を含んでいる。CMOSインプリメンテーションにおいて、PMOS/NMOSペアは、出力パス内に採用される。ハイ(電圧)スイングモード状態の最中に、出力の位相は、出力波形がPMOS/NMOSペアのゲートに出現する電圧に対して同相となるようにフリップされる。本技術は、それによって、ゲート−ドレイン間電圧を減少させ、低位相ノイズ及び低消費電力にしたがった構成内のMOSデバイスの改善された信頼性を許容する。  (もっと読む)

(もっと読む)

信号増幅回路、光受信回路、光モジュールおよびデータ交換システム

【課題】小面積で、電源雑音の信号への重畳を低減することが可能な光受信回路を提供する。

【解決手段】PMOSトランジスタ101とNMOSトランジスタ102とで構成されたCMOSインバータと、前記CMOSインバータに信号を入力する入力端子106と、前記CMOSインバータからの信号を出力する出力端子107と、前記CMOSインバータと接続された電源108と、前記CMOSインバータと各々接続される第一の素子103と第二の素子104と、を備え、互いに逆位相となる2種類の電源経路を有する光増幅回路である。

(もっと読む)

増幅器および発振器

【課題】MOSトランジスタの高周波領域におけるトランスコンダクタンスの劣化を招くことなく、低消費電力化を図ることが可能な増幅器などの提供。

【解決手段】この発明は、MOSトランジスタQ1などを含む増幅器である。MOSトランジスタQ1のゲートには第1の入力信号が入力され、MOSトランジスタQ1のバルクには第2の入力信号が入力され、MOSトランジスタQ1のソースから出力信号が出力される。そして、第1の入力信号と第2の入力信号とは同相の信号である。

(もっと読む)

アナログ増幅回路を用いた出力回路

【課題】アイドリング電流による静電保護抵抗の電圧降下の問題を回避しならが、出力特性を改善する。

【解決手段】出力回路が、アナログ増幅回路と、第1〜第n出力ノードと、出力パッドと、第1〜第n静電保護抵抗とを具備している。アナログ増幅回路は、入力電圧を受け取る差動増幅段と、第1〜第n出力系統とを備えている。第1〜第n出力系統のうちの第i出力系統は(iは、1以上n以下の任意の整数)、第1〜第n出力ノードのうちの第i出力ノードにドレインが接続され、ゲートが差動増幅段の第1出力に接続されたPMOSトランジスタと、第i出力ノードにドレインが接続され、ゲートが差動増幅段の第2出力に接続されたNMOSトランジスタとを備えている。第1〜第n静電保護抵抗は、それぞれ、第1〜第n出力ノードと出力パッドの間に接続されている。

(もっと読む)

サブスレッショルド集積回路におけるプロセスばらつき防止方法およびボディ電位変調回路

サブスレッショルド集積回路におけるプロセスばらつき防止方法とボディ電位変調回路が掲載されている。前記ボディ電位変調回路は、目標MOSデバイス(11)と、誘導MOSデバイス(12)と、電流−電圧変換回路(13)とを備えている。前記電流−電圧変換回路は、誘導MOSデバイスから出力された誘導電流を誘導電圧に変換するとともに、その誘導電圧を目標MOSデバイスのボディ端にフィードバックして、目標MOSデバイスのボディ電位を変調するためのものである。  (もっと読む)

(もっと読む)

コンパレータ回路及びそのコンパレータ回路を備えたLVDSレシーバ

【課題】高速動作しつつ、良好な信号を出力することができるコンパレータ回路及びLVDSレシーバを提供する。

【解決手段】コンパレータ回路20を構成する増幅部52は、カスケード接続された複数のインバータ回路を有する。複数のインバータ回路53〜55のうち初段のインバータ回路53に帰還抵抗R1を設けると共に、この初段のインバータ回路53の入力ノードt1と出力ノードt2に双方向ダイオードとして機能させたトランジスタQ33,Q34を接続する。

(もっと読む)

増幅回路、その起動方法、およびそれらを用いたオーディオ再生装置ならびに電子機器

【課題】ミュート解除時のノイズを抑制する。

【解決手段】増幅部10は、カップリングキャパシタC1を介して入力されたオーディオ信号S1を増幅する。充電回路20は、増幅部10の入力端子102に接続されるカップリングキャパシタC1の一端を充電する。電流検出部40は、充電回路20からカップリングキャパシタC1に対する充電電流Icをモニタする。バイパススイッチSW1は、増幅部10の出力端子側の第1ノードN1と、増幅部10の入力端子102側の第2ノードN2との間に設けられる。バイパススイッチSW1は、電流検出部40により充電電流Icが所定のしきい値より小さくなったことが検出されると、オンからオフに切りかえられる。

(もっと読む)

半導体装置

【課題】増幅回路の利得を補償するためにGm補償バイアス電圧を与えても、増幅回路の出力電流電圧の変動が少なく、出力信号の歪み特性が良好な半導体装置を提供する。

【解決手段】半導体装置において、利得制御回路と、前記利得制御回路により利得が一定に制御された第1の回路と、前記第1の回路に対するバイアス回路とを備え、前記第1の回路は、第1のトランジスタと負荷抵抗とを有し、前記第1の回路の増幅率又は減衰率は前記第1のトランジスタの相互コンダクタンスと前記負荷抵抗の抵抗値との積に比例し、前記負荷抵抗に印加される電圧を前記半導体装置の出力とし、前記バイアス回路は、前記第1のトランジスタに流れるドレイン電流に比例した電流と前記負荷抵抗値に反比例した電流との差分電流を生成して出力し、前記バイアス回路の出力は前記第1の回路の出力ノードに接続される。

(もっと読む)

増幅回路

【課題】増幅器の消費電力を抑制する。

【解決手段】インバータにより構成された差動増幅器110は、NMOSトランジスタ142を介して電源電圧VCCと接続され、PMOSトランジスタ144を介して接地電圧GNDと接続されている。NMOSトランジスタ142は制御信号端子PSと接続され、PMOSトランジスタ144は、インバータ150を介して制御信号端子PSと接続される。NMOSトランジスタ142とPMOSトランジスタ144は、制御信号端子PSからの制御信号により同時に切断可能に制御される。

(もっと読む)

反転増幅回路対、これを含む集積回路およびセット機器

【課題】ノイズ信号を軽減し、入力信号を安定に増幅動作させることができる反転増幅回路対を提供する。

【解決手段】抵抗1,2と演算増幅回路3からなる反転増幅回路9,10を2段直列に接続し、反転増幅回路9のマスクレイアウト、反転増幅回路10のマスクレイアウトを半導体回路チップ8上に隣接配置することにより、反転増幅回路9の出力ノイズ信号VN1は反転増幅回路10では極性が、反転増幅回路10に進入するノイズ信号VN2と逆極性となって、また反転増幅回路9と反転増幅回路10に進入するノイズは、反転増幅回路9と反転増幅回路10が、隣接配置されることで相関を持ち、ノイズの大きさ、時間的位置がほぼ同等となるので、打ち消す作用が生じ、信号に含まれるノイズレベルを軽減することができる反転増幅回路対を得る。

(もっと読む)

インバータアンプ

【課題】電界効果型トランジスタで構成されるインバータアンプは、定電流源である電界効果型トランジスタのゲート電圧変動により増幅率が悪化し、多段接続時には直流バイアス電線を介して電圧変動が混合するため互いに悪影響を及ぼし合い、所定の性能が得られない。

【解決手段】本発明のインバータアンプは、アンプを構成する定電流源である電界効果型トランジスタのゲート端子に電圧変動防止回路を備えている。電圧変動防止回路は、そのゲート端子に伝播する電圧変動などを抑制する。このような構成とすることによって、アンプを構成する電界効果型トランジスタのゲート電圧は変動せず、インバータアンプの増幅率を損うことなく増幅できる。また、多段接続の場合でも、各アンプが不安定となる要因を排除することができるから、大増幅を行うアンプも実現可能になる。

(もっと読む)

増幅回路、並びに半導体装置および制御方法

【課題】製造時のMOSバラツキを補正することができるようにする。

【解決手段】PMOSトランジスタQp2nは、PMOSトランジスタQp1nのソースにドレイン、Vddにソースが接続され、スイッチSW1nは、PMOSトランジスタQp2nのゲートに接続され、PMOSトランジスタQp2nのゲート電圧を、VddまたはVPに切り替える。NMOSトランジスタQn2nは、NMOSトランジスタQn1nのソースにドレイン、GNDにソースが接続され、スイッチSW2nは、NMOSトランジスタQn2nのゲートに接続され、NMOSトランジスタQn2nのゲート電圧を、GNDまたはVNに切り替える。スイッチSW1nおよびスイッチSW2nは、PMOSトランジスタの動作電流とNMOSトランジスタの動作電流との偏りがなくなるように、スイッチング動作することで、製造時のMOSバラツキを補正することができるようになる。本発明は、増幅回路に適用できる。

(もっと読む)

インバータアンプ

【課題】パワーダウン時のリーク電流が抑制されるインバータアンプの提供。

【解決手段】入力端子とバイアス供給回路との間にパワーダウン時リーク電流抑制用トランジスタを設ける。

(もっと読む)

低電力消費用途のためのシフトレジスタ

【課題】低電力消費および高速度動作を可能にするシフトレジスタステージを提供する。

【解決手段】高電圧シフトレジスタステージは、クロックバッファを用いることなく低電圧クロック信号入力を直接受け入れことができる。シフトレジスタステージ回路30は、低電圧スイングのクロック信号を用いて、単一状態ノードaを直接駆動させるステージ回路において作動する。このシフトレジスタステージは、表示装置や形態機器などにおいて用いられることができる。

(もっと読む)

インバータ回路および遅延回路

【課題】遅延回路などに適用した場合に、回路規模を小さくでき、貫通電流を防止でき、

かつ、消費電力を低減できるインバータ回路の提供

【解決手段】この発明は、入力信号IN1でオンオフするMOSトランジスタP11と、

入力信号IN2でオンオフするN型のMOSトランジスタN11と、直列接続されるとと

もにゲートとドレインが接続される2つのMOSトランジスタP12、N12とを備えて

いる。MOSトランジスタP11、MOSトランジスタP12、N12、およびMOSト

ランジスタN11は、第1電源VDDと第2電源VSSとの間に直列に接続されている。

MOSトランジスタP11とP12の共通接続部から出力信号OUT1を取り出し、MO

SトランジスタN11とN12の共通接続部から出力信号OUT2を取り出すようになっ

ている。

(もっと読む)

信号遅延回路およびこれを用いたパルス発生回路

【課題】高速信号に対し遅延時間を連続的に調整可能な信号遅延回路を提供すること。さらに、電源電圧が低い場合でも、遅延時間の変動を抑制できる回路を提供すること。

【解決手段】信号遅延回路1は、第1のインバータ回路101と、その出力端子に接続する第2のインバータ回路102と、第2のインバータ回路の出力端子からその入力端子に至る帰還回路105を備える。帰還回路の帰還量を制御することで、第1のインバータ回路の遅延時間を調整する。ここに、帰還回路はMOSトランジスタ106で構成し、MOSトランジスタのゲート電圧を制御することで遅延時間を調整する。また、電源電圧の変動に応じて帰還量を調整し、信号遅延回路の遅延時間の変動を抑制する。

(もっと読む)

反転増幅器

【課題】これまでの反転増幅器では内部の増幅器の構成によっては発振を起こしてしまう問題があった。

【解決手段】反転増幅器において、入力信号を増幅する第1トランジスタ108と、該第1トランジスタの出力信号を増幅する第2トランジスタ110と、該第2トランジスタの出力信号を増幅する第3トランジスタ111と、該第3トランジスタの出力信号を前記第1トランジスタの出力部に帰還する内部帰還抵抗112とを備える多段増幅器を備える。かかる構成によれば、3段のトランジスタで構成される多段増幅器の利得を低下させることができるので発振はしないで、必要な利得を設定することができる。

(もっと読む)

1 - 20 / 26

[ Back to top ]