Fターム[5J500AC04]の内容

Fターム[5J500AC04]の下位に属するFターム

電源電圧低下の影響低減 (35)

Fターム[5J500AC04]に分類される特許

1 - 20 / 151

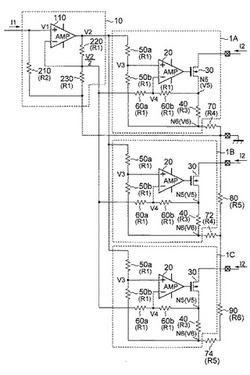

定電流回路

【課題】1または複数の他の定電流回路との間で共通インピーダンスを共有する定電流回路の出力電流に、他の定電流回路の出力電流に起因した誤差が生じることを防ぐ。

【解決手段】オペアンプと、当該オペアンプの出力端子にゲートが接続されドレインが当該定電流回路の出力端となる電界効果トランジスタと、この電界効果トランジスタのソースと共通インピーダンスとの間に介挿された抵抗と、を有する定電流回路に、共通インピーダンスおよび抵抗の共通接続点の電圧を第1の基準電圧とし、オペアンプの非反転入力端子には、第2の基準電圧と第1の基準電圧と電位差を所定の分圧比で分圧した電圧を印加し、同反転入力端子には、電界効果トランジスタのソースおよび抵抗の共通接続点の電圧と第3の基準電圧との電位差を所定の分圧比で分圧した電圧を印加する分圧回路を設ける。

(もっと読む)

信号処理装置

【課題】 抵抗及び小さな静電容量を用いた回路により、検出素子の出力信号を直流成分を除いて増幅する小型な信号処理装置を得る。

【解決手段】 入力信号が第1のインピーダンスを介して反転入力端子に入力される第1のオペアンプと、第1のオペアンプの反転入力端子と出力端子とに接続された第2のインピーダンスと、基準電圧が非反転入力端子に入力され、出力端子が第1のオペアンプの非反転入力端子に接続された第2のオペアンプと、第2のオペアンプの反転入力端子と出力端子とに接続された第1の静電容量と第1のスイッチと、第2のスイッチを介して第1のオペアンプの出力端子と前記第2のオペアンプの反転端子とに接続された第3の抵抗と、第3のスイッチを介して第1のオペアンプの出力端子と第2のオペアンプの反転端子とに接続された第4の抵抗とを備えた。

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

カレントミラー回路及びそれを有する増幅回路

【課題】電源電圧の変動に対する出力電流の変動が小さいカレントミラー回路を提供すること。

【解決手段】カレントミラー回路5は,トランジスタM12の第2のドレイン電流を第2の比率で複製した第2の複製電流を生成する第2の複製電流生成回路J2と,基準電流と第2の複製電流が流入する接続ノード接続ノードQ1とグランドとの間に設けられ,トランジスタM11の第1のドレイン電流を第1の比率で複製した第1の複製電流を生成する第1の複製電流生成回路J1とを有し,出力トランジスタM10のゲートとトランジスタM11,M12のゲートと接続ノードQ1とが接続されている。

(もっと読む)

増幅装置

【課題】電力効率の低下を抑制する。

【解決手段】増幅部1は、電力ノードN1に供給される電力によって入力信号を増幅する。電源部2は、電力ノードN1に固定電圧の電力を供給する。電源部3は、入力信号のエンベロープに基づくエンベロープ信号と、電力ノードN1の電圧とに基づいて、電力ノードN1に可変電圧の電力を供給する。AS部4は、電源部2が電力ノードN1に電力を供給し、電源部3が電力ノードN1に電力を供給しない固定電圧電力モードにおいて、電力ノードN1のインピーダンスを下げる。合成部5は、固定電圧電力モードにおいて、電源部3がAS部4による電力ノードN1の電圧変化によって、電力ノードN1に電力を供給しないように、エンベロープ信号にキャンセル信号を合成する。

(もっと読む)

低雑音増幅器

【課題】製造上の素子の特性ばらつきや電源電圧の変更やばらつきに対しても安定化させる。

【解決手段】入力端子2と、入力端子に入力された入力信号を増幅するトランジスタ1と、トランジスタの出力信号を出力する出力端子3と、トランジスタの出力信号の帰還量として振幅を調整して出力する帰還量調整回路10と、トランジスタに供給されるバイアス電流を生成するバイアス回路9と、帰還量調整回路の出力電圧と参照電圧とを比較して入力信号が前記トランジスタの利得抑圧を発生させることを判定したときトランジスタのバイアス電流を増加させるようにバイアス回路を動作させる差動電圧比較器11と、参照電圧を生成して差動電圧比較器の一方の入力端に印加させる第1の第1の入力バイアス回路12と、帰還量調整回路の出力電圧にバイアス電圧を付加して差動電圧比較器の他方の入力端に印加させる第2の第2の入力バイアス回路13と、を備える低雑音増幅器。

(もっと読む)

電力変換装置

【課題】大出力でスピーカが駆動された場合でも、出力電圧の変動を抑制することができる電力変換装置を提供する。

【解決手段】入力信号を増幅するアンプである負荷駆動回路2に対し、コントローラ11によってNMOSQ1をオンオフすることで電力を供給するDC/DCコンバータ1と、スピーカSPを駆動するアンプ出力電圧を検出するアンプ出力電圧検出機能と、検出したアンプ出力電圧の変化量とDC/DCコンバータ1の出力電圧とを演算した誤差信号をDC/DCコンバータ1にフィードバックするフィードバック機能とを備えたフィードバック回路4とを具備し、コントローラ11は、フィードバックされた誤差信号に基づいて、アンプ出力電圧が増加すると供給する電力量を増加させ、アンプ出力電圧が減少すると供給する電力量を減少させる。

(もっと読む)

電力増幅器用バイアス回路

【課題】差分周波数Δfが数百MHzにおいても電力増幅器用バイアス回路のリップル電圧ΔVが抑制されてバイアス回路電圧が平滑化され、マイクロ波/ミリ波/サブミリ波帯の高周波に適用可能な電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器の出力側整合伝送線路のバイアス回路接続点に接続された第1ボンディングワイヤと、第1ボンディングワイヤの終端に接続された第2ボンディングワイヤと、第1ボンディングワイヤの終端に接続されたオープンスタブ伝送線路と、第2ボンディングワイヤの終端に接続されたバイパスリザバーキャパシタとを備える電力増幅器用バイアス回路。

(もっと読む)

レベルシフト回路及び半導体装置

【課題】電源電圧が低電圧化したときの動作不良の発生を抑制することのできるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、第1の高電位電圧VLを信号レベルとする入力信号Siに応じて相補的にスイッチング制御されるNチャネルMOSトランジスタTN1,TN2を有するレベル変換部10を備える。レベルシフト回路1は、第1の高電位電圧VLの低下を検出したことを示す検出信号DSを生成する検出部20と、検出信号DSに応じて、トランジスタTN1,TN2の閾値電圧が低くなるようにトランジスタTN1,TN2のボディバイアスVbbを制御する制御部30とを備える。

(もっと読む)

パルス駆動回路

【課題】高周波増幅用のFETのドレインに印加されるパルス電圧の安定化を図る。

【解決手段】駆動用電源11の出力電圧に基づきMOS−FETQ1を駆動する。Q1はパルス信号源12から出力される基準パルス信号bでスイッチングさせ、Q1オン時は、コンデンサC1の電荷を移行させて得られる電圧でQ1を非飽和状態で駆動する。Q1のスイッチングによりソース電極に得られるパルス電圧を、ゲート電極に供給される高周波信号を増幅する高周波電力FETQ2の駆動電圧としてドレイン電極に印加する。Q2のドレイン電極に発生するパルス電圧dと基準パルス信号bの電圧をオペアンプOP2で比較し、Q1のゲート電極にフィードバックする。非飽和状態で駆動されるQ1にフィードバックさせたことで、Q1に印加されるパルス内ドレイン電圧の低下を防止することができる。

(もっと読む)

映像信号出力回路

【課題】 電源電圧や周囲温度が変動した場合にも、出力DCレベルがずれるのを回避するとともに、動作電源電圧範囲が広く電源リップルリジェクション特性の優れた映像ドライバを提供する。

【解決手段】 映像信号が入力される入力端子の電位をクランプするクランプ回路と、入力された映像信号および所定の基準電圧を入力とし映像信号を増幅して出力する差動増幅回路と、クランプ回路に供給するバイアス電圧および差動増幅回路に供給する基準電圧を生成する分圧回路と、分圧回路により生成されたバイアス電圧または基準電圧に所定のオフセット電圧を付加または減算してクランプ回路または差動増幅回路に供給するオフセット回路と、を備えた映像信号出力回路において、オフセット回路は、pnpバイポーラトランジスタおよびnpnバイポーラトランジスタを備え、2つのトランジスタのベース・エミッタ間電圧の差に応じた電圧を出力するように構成した。

(もっと読む)

半導体装置及びこれを用いた電子機器

【課題】電源電圧のばらつきに依ることなく、入力信号を適切に電力増幅して出力信号を生成することが可能な半導体装置、及び、これを用いた電子機器を提供する。

【解決手段】半導体装置100は、VDDとGNDとの間でパルス駆動される入力信号Sinを増幅し、VCC(>VDD)とGNDとの間でパルス駆動される出力信号Soutを生成するドライバZ20と、VCCからVDDを生成するVDD生成部Z30と、を有するものであって、ドライバZ20は、VDDの入力を受けて動作し出力信号Soutの帰還経路となる1次積分器(AMP、R1、R2、C1)を含み、VDD生成部Z30は、VCCを分圧してVDDを生成する分圧器(R3、R4)を含む。

(もっと読む)

バイアス回路

【課題】プロセス、温度及び/又は電源電圧の変動による電流源の電流の変動を防止することができるバイアス回路を提供することを課題とする。

【解決手段】バイアス回路は、第1の定電位のノードと前記第1の定電位よりも低い第2の定電位のノードとの間の第3の電位のノードに接続される第1の抵抗(R11)と、ドレインが前記第1の抵抗を介して前記第3の電位のノードに接続され、ゲート及びソースが前記第2の定電位のノードに接続されるデプレッション型電界効果トランジスタ(Q11)とを有し、前記デプレッション型電界効果トランジスタのドレインは、第1の電流源のバイアス電圧を出力する。

(もっと読む)

光受信回路用のトランスインピーダンスアンプ

【課題】電源電圧の変動に関わらず、クロスポイントのシフト幅を安定させることが可能な光受信回路用のトランスインピーダンスアンプを提供する。

【解決手段】TIA15は、互いに直列に接続された負荷抵抗23、入力FET22及びカスコードFET21を含み、入力FET22のゲート端子が入力端15aに接続された入力部20と、互いに直列に接続されたソースフォロワFET31及び電流源FET33を含み、ソースフォロワFET31のゲート端子にカスコードFET21のドレイン電圧を受けるとともに、ソースフォロワFET31のソース端子が帰還抵抗34を介して入力端15aに接続されたソースフォロワ部30と、電流源FET33のゲートバイアスを生成するバイアス生成部40とを備える。電流源FET33を流れる電流は、電源電位線18における電源電圧の大きさに基づいて可変とされている。

(もっと読む)

差動増幅回路

【課題】電源電圧変動除去比を向上させつつ、回路内の消費電流の低減及び回路自体の小型化を図ることができる差動増幅回路を提供する。

【解決手段】電源電圧源に接続された電源ラインと、2つの差動入力素子からなる入力回路と、2つの差動入力素子にそれぞれが接続された2つのトランジスタからなる能動負荷とからなり、2つの差動入力素子のそれぞれに入力される入力信号に応じて差分信号を生成する入力部と、差分信号を増幅して出力電圧生成信号を生成する増幅部と、増幅部から供給される出力電圧生成信号と、電源電圧源から供給される電源電圧と、に基づいて出力電圧を生成する出力部と、2つのトランジスタのそれぞれの制御端と電源ラインとの間に接続され、電源電圧のノイズ成分のみを透過させるノイズ透過部と、を有することを特徴とする差動増幅回路。

(もっと読む)

D級増幅器

【課題】小さな回路規模の回路で電源電圧変動による誤差を低減する。

【解決手段】D級増幅器(10)は、ブリッジ回路(24)と、電源電圧検知部(30)と、PWM利得制御部(22)とを具備する。ブリッジ回路(24)は、誘導性負荷(40)を駆動する。電源電圧検知部(30)は、ブリッジ回路(24)に供給する電源電圧の電圧変動を示す量子化電源電圧信号を出力する。PWM利得制御部(22)は、量子化電源電圧信号に基づいて利得を制御し、入力信号を増幅して前記ブリッジ回路に出力する。電源電圧検知部(30)は、ブリッジ回路に供給する電源電圧と量子化電源電圧信号との差分を積分して量子化信号を出力する誤差積分部(39)と、量子化信号の高周波成分を除去して量子化電源電圧信号を出力するデジタルフィルタ(38)とを備える。PWM利得制御部(22)は、電源電圧の変動を相殺するように入力信号を増幅する利得を制御する。

(もっと読む)

高周波回路

【課題】低電圧のバッテリを用いて高電力を得ることが可能であり、且つ、低電力時の動作安定性を確保した高周波回路を提供する。

【解決手段】送信すべき高周波信号を増幅する増幅回路を複数並列に接続し、各増幅回路の出力を合成して空中線に供給する増幅部と、増幅部に低出力の動作をさせるローパワーモード時に、ローパワー信号を出力する制御部と、ローパワー信号によって複数の増幅回路のうち一部を停止させる動作抑制回路とを備えた。

(もっと読む)

カレントミラー回路

【課題】出力電流の変動の少ないカレントミラー回路を提供する。

【解決手段】ゲート電極同士が接続された第1および第2MOSトランジスタ11、12と、ソース電極が第1MOSトランジスタ11のドレイント電極に接続され、ドレイン電極が第1および第2MOSトランジスタ11、12ゲート電極に接続されて電流入力端子15に接続された第3MOSトランジスタ13と、ゲート電極が第3MOSトランジスタ13のゲート電極に接続され、ソース電極が第2MOSトランジスタ12のドレイン電極に接続され、ドレイン電極が電流出力端子16となる第4MOSトランジスタ14と、第3および第4MOSトランジスタ13、14のゲート電極にバイアス電圧を与えるためのバイアス回路17と、を具備する。

(もっと読む)

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

利得変動補償装置

【課題】電圧源から提供する電圧が変動した場合でも増幅回路に流れる電流量を制御し、利得の変動を補償する利得変動補償装置を提供すること。

【解決手段】利得変動補償装置100は、電圧源111から提供される電圧及び定電流源を用いて入力信号を増幅する増幅回路110と、電圧源111から提供される電圧の変動を検知する電源電圧変動検知部120と、電源電圧変動検知部120により検知された電圧の変動量に応じて、増幅回路110に流れる電流量を制御する電流可変回路130とを備える。利得変動補償装置100は、増幅回路110又はその差動回路の定電流源トランジスタと並列に電流可変回路130を接続し、事前に電流可変回路130に電流を流し、電源電圧変動検知部120において電源電圧の変動を検知する。電流可変回路130は、電圧変動量に応じて電流量の調整を行い、増幅回路110に流れる電流量を制御する。

(もっと読む)

1 - 20 / 151

[ Back to top ]