Fターム[5J500AC22]の内容

増幅器一般 (93,357) | 目的、効果 (9,357) | 歪低減(直線性改善を含む) (1,554) | 振幅歪の低減 (315)

Fターム[5J500AC22]の下位に属するFターム

スイッチング歪、ノッチング歪の低減 (22)

クロスオーバー歪の低減 (15)

振幅の飽和防止 (57)

Fターム[5J500AC22]に分類される特許

1 - 20 / 221

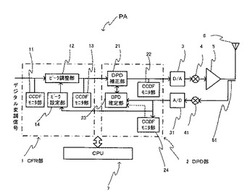

電力増幅器

電力増幅器および増幅制御方法

【課題】バックオフが最小化されC/Nの良い電力増幅器とその信号ピークレベル調整方法を提供する。

【解決手段】CFR部1の入出力と、DPD部2の出力とアンテナへ出力される信号のループバック信号とのCCDFをCCDFモニタ部11、13、22、24でそれぞれ測定し、CCDFモニタ部24で測定したCCDFのPAPRがCCDFモニタ部13のそれよりも狭くならないようにピーク設定部14と、ピーク調整部12を制御する。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】低ノイズ係数(NF)、高利得、及び低電流消費と共に、非常に高い三次入力インターセプトポイント(IIP3)を有する低ノイズ増幅器(LNA)を提供する。

【解決手段】修正された微分重ね合わせ(DS)低ノイズ増幅器(LNA)222は、メイン電流経路320とキャンセル電流経路322を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタ306,308が、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

増幅器

【課題】歪の発生を少なくする。

【解決手段】入力信号(IN)を受ける初段増幅回路(PREA)と、ゲートに初段増幅回路(PREA)の出力信号を受けるソース接地の第1のトランジスタ(Tr1)と、ソースを第1のトランジスタ(Tr1)のドレインに接続し、ドレインから出力信号(OUT)を送出すると共にドレインに対して電源供給がなされるゲート接地の第2のトランジスタ(Tr2)と、初段増幅回路(PREA)の電源端と第2のトランジスタ(Tr2)のソースとの間に介在する第1のインピーダンス回路(Z1)と、を備える。第1のインピーダンス回路(Z1)は、直流を通過させると共に、所定の周波数帯域において所定のインピーダンス以上となるように構成された回路である。

(もっと読む)

歪補償装置

【課題】 FDD方式及びTDD方式のいずれの通信方式にも適用することができ、有効データ区間を精度良く反映した遅延調整を実現する歪補償装置を提供する。

【解決手段】 歪補償装置は、歪補償部1が送信信号に歪補償テーブルを用いて歪補償を行い、遅延調整部2が歪補償前の送信信号と歪補償後の送信信号の帰還信号との遅延を調整し、誤差演算部3が遅延調整された送信信号と帰還信号との遅延誤差が小さくなるように歪補償テーブルを更新する。そして、有効データ区間イネーブル生成部5が送信信号に含まれる制御信号を用いて送信信号中に送信データが存在する区間(有効データ区間)を示す信号を生成し、遅延調整部2が上記の遅延調整を有効データ区間で行なう。

(もっと読む)

増幅装置

【課題】誤った遅延調整の実行を抑制させることで、歪補償性能の劣化を防止するようにした増幅装置を提供する。

【解決手段】入力信号を増幅器2により増幅する増幅装置において、入力信号を遅延させる遅延部3と、遅延された入力信号と増幅器1の出力を帰還させた帰還信号に基づいて、増幅器1による増幅において発生する歪を補償するための補正情報を作成する歪補償制御部4と、入力信号に対して補正情報に基づく歪補償処理を施す歪補償部1と、遅延された入力信号と帰還信号について、各信号の波形のずれの程度が小さくなるように遅延部3の遅延量を調整する遅延調整部5、入力信号に周波数成分が所定の低さの波形の区間が含まれることを検出し、当該区間についての各信号を遅延調整部5による調整に用いないように制御するバースト信号検出部6、を備えた。

(もっと読む)

増幅装置及び無線通信装置

【課題】LINC方式において、振幅がゼロ付近の出力信号の生成を容易にする。

【解決手段】複数の増幅器702a,702bによって増幅された信号間の位相差に応じて、入力信号に含まれている振幅情報が再生されるLINC方式の増幅装置701であって、前記複数の増幅器702a,702bに対して、入力信号に含まれる振幅情報が保持された信号が入力されるよう構成されている。

(もっと読む)

ボルテージフォロワ回路

【課題】動作電流を大きく増大させることなく、入力信号変化に対する出力追従性を向上させることのできるボルテージフォロワ回路を提供する。

【解決手段】実施形態のボルテージフォロワ回路は、P型差動対101と、N型差動対102と、折り返しカスコード型中間増幅段103と、出力段104とを備える演算増幅回路100を使用するボルテージフォロワ回路であって、出力変化加速部1が、P型差動対101に接続された定電流源I101からP型差動対101へ電流が流れないときに、出力段104へ加速電流I1を印加して出力段104の出力変化を加速し、出力変化加速部2が、N型差動対102に接続された定電流源I102からN型差動対102へ電流が流れないときに、出力段104へ加速電流I2を印加して出力段104の出力変化を加速する。

(もっと読む)

変調電源回路

【課題】出力電圧誤差が少ない、多出力DC電源部およびその切り替え回路と誤差増幅器を用いた変調電源回路を提供する。

【解決手段】多出力DC電源部101と、それらの各出力経路に直列に接続され、エンベロープ信号アナログ入力部103から入力されるエンベロープ信号と閾値とを比較する切り替え電圧の閾値判定部114の出力で制御される切り替え回路102と、入出力をAC結合した誤差増幅器105と、切り替え電圧の閾値判定部114とこの切り替え電圧の閾値判定部114の出力に接続された任意電圧発生部106とを備え、切り替え電圧を任意電圧分だけずらすように構成する。これにより、高周波増幅器109に誤差の少ない電圧を出力することができる。

(もっと読む)

アクティブポストディストーション線形化を有する差動増幅器

【課題】電力消費量を低下させ、回路面積を縮小した線形性がより高いLNAを提供する。

【解決手段】差動増幅器300の一腕は第1トランジスタ310及び第2トランジスタは320、第1のカスケード対として結合され、第3トランジスタ330及び第4トランジスタ340は、第2のカスケード対として結合される。第3トランジスタ330は、第2トランジスタ320のソースに結合したゲートを有し、第4トランジスタ340は、第2トランジスタ320のドレインに結合したドレインを有する。第3トランジスタ330は、第1トランジスタ310によって生成される3次歪み成分を除去するのに用いられる歪み成分を生成する。誘導子350は、第1トランジスタ310に対してソースディジェネレーションを提供し、歪み除去を向上させる。第2トランジスタ320及び第3のトランジスタ330の大きさは、利得損失を低減させるために選択される。

(もっと読む)

リニアライザ

【課題】ダイオードから見るインピーダンスが変化しても、利得特性と位相特性の単調変化を実現することができるリニアライザを得ることを目的とする。

【解決手段】アノードが信号路3に接続されて、順方向に電圧が印加されているダイオード15と、アノードが信号路4に接続されて、順方向に電圧が印加されているダイオード16とを備え、ダイオード15のカソードとダイオード16のカソードとの接続点がバイアス接地用ビアホール17に接地されている。

(もっと読む)

差動増幅回路

【課題】基本波周波数のゲイン変化を生じさせることなく、2次高調波のみを抑圧および低減した回路面積の小さい差動増幅回路の実現。

【解決手段】差動対をなし、差動信号S,ZSが入力される2個のMOSトランジスタTr1,Tr2と、2個のMOSトランジスタTr1,Tr2のドレイン間に直列に接続された2個の容量素子C1,C2と、2個の容量素子C1,C2の接続ノードとバイアス電源端子GND間に接続されたインダクタンス素子L1と、を有する差動増幅回路。

(もっと読む)

高周波増幅回路

【課題】低出力モードで出力電力を変化させても、ゲインの差が殆ど生じない高周波増幅回路を実現する。

【解決手段】高周波増幅回路100Aは増幅用トランジスタ10を備える。増幅用トランジスタ10のベースは、バラスト抵抗素子52を介してエミッタフォロワ用トランジスタ20のエミッタに接続する。エミッタフォロワ用トランジスタ20のベースには、抵抗素子51を介してバイアス電源が接続されている。エミッタフォロワ用トランジスタ20のコレクタには、抵抗素子53を介してモード制御電源が接続されている。抵抗素子53は固定抵抗値の抵抗素子である。モード制御電源は、可変電圧型であり、モードに応じて直流のモード制御電圧Vmodeを発生する。モード制御電圧Vmodeは、低出力モード時には低電圧となり、高出力モード時には高電圧となる。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に含まれる増幅回路における入出力特性の線形性が劣化するのを抑えるとともに、増幅器自体における入出力特性の線形性が劣化するのを抑えることができる半導体装置を提供する。

【解決手段】本発明は、外部と接続する複数の端子を有する配線基板72に、半導体チップ71を実装してパッケージングしてある半導体装置である。半導体装置は、半導体チップ上に形成してある、少なくとも一つの差動増幅器61と、平衡信号線路を差動増幅器61と接続し、半導体チップ71上に形成してある、少なくとも一つのバラン62とを備える。差動増幅器61の接地配線と、バラン62の接地配線とは、半導体チップ71上に分離して形成してあり、差動増幅器61の一つの接地配線と配線基板72とを接続するボンディングワイヤ77の数が、バラン62の一つの接地配線と配線基板72とを接続するボンディングワイヤの77数より多い。

(もっと読む)

前置歪み部を制御する装置及び方法、並びに電力制御状態を検出する方法

【課題】本発明は、前置歪み部を制御する装置及び方法、並びに電力制御状態を検出する方法に係る。

【解決手段】電力増幅器へ入力される信号を予め歪ませる前置歪み部を制御する方法は、前置歪み部によって使用される前置歪み係数を記憶するステップと、電力増幅器の出力電力を示すインデックスを得るステップと、インデックスに基づき、電力増幅器が電力制御を受けている状態にあるかどうかを検出するステップと、電力増幅器が電力制御を受けている状態にあると検出される場合には、記憶されている前置歪み係数を前置歪み部へ供給し、電力増幅器が電力制御を受けている状態にないと検出される場合には、前置歪み係数適応更新動作を実行するユニットによって計算される前置歪み係数を前置歪み部へ供給するステップとを有する。

(もっと読む)

差動増幅回路

【課題】入力電力に対する利得の線形動作領域を広くすることができる差動増幅回路を提供することを課題とする。

【解決手段】差動増幅回路は、ゲートが第1の差動入力信号端子に接続され、ソースが基準電位ノードに接続され、ドレインが第1の差動出力信号端子に接続される第1のトランジスタ(211)と、ゲートが第2の差動入力信号端子に接続され、ソースが基準電位ノードに接続され、ドレインが第2の差動出力信号端子に接続される第2のトランジスタ(212)と、第1のトランジスタのゲート及び第2のトランジスタのドレイン間に接続される第1の可変容量(401)と、第2のトランジスタのゲート及び第1のトランジスタのドレイン間に接続される第2の可変容量(402)と、第1の差動出力信号端子又は第2の差動出力信号端子の信号の包絡線を検波する第1の包絡線検波器(405)とを有する。

(もっと読む)

低歪み可変利得増幅器(VGA)

【課題】非対称な信号の非対称性を補正する。

【解決手段】第1抵抗は、増幅器の入力ノード及び出力ノードの間に接続され、入力ノードは非対称信号を受信する。第2抵抗は、増幅器の入力ノードに接続される。第2抵抗は、線形レジスタを含む。第3抵抗は、第2抵抗に接続される。出力ノードにおける非対称信号を補正するべく、増幅器によって提供される非対称補正量を調整するように第3抵抗を変化させる。非対称補正量は、第1抵抗及び第2抵抗と第3抵抗との組み合わせの関数である。

(もっと読む)

抵抗素子及び反転バッファ回路

【課題】無駄な電流や信号の歪みを発生させることなく、抵抗素子層の周辺の半導体基板や、抵抗素子層の上部を通過する電源線、信号線等の電位によって抵抗値が変化するのを抑えることのできる抵抗素子及び反転バッファ回路を提供する。

【解決手段】抵抗素子10は、半導体基板14上に、第1の電極11及び第2の電極12を有する抵抗素子層13が形成されている。第1の電極11の電位によってバイアスされた第1の導電層15と、第2の電極12の電位によってバイアスされた第2の導電層16とで、抵抗素子層13の下部が均等に覆われている。このように、両端をバイアスされた抵抗素子層13の下部又は上部の少なくとも一方を覆う第1の導電層15及び第2の導電層16によって、抵抗素子層13の周辺の半導体基板14等との電圧差による抵抗値の変化を相殺することで、抵抗値の変化を抑える。

(もっと読む)

信号増幅回路、電流電圧変換回路、および光受信器

【課題】入力電流の大きさの変化に応じた出力電圧波形の歪みを抑えることができる信号増幅回路、電流電圧変換回路、および光受信器を提供する。

【解決手段】プリアンプ13は、トランジスタ21、及び該トランジスタ21と電源電位線18との間において出力信号を提供するノードAを有し、光電流Iinを受ける信号入力端13aにトランジスタ21のエミッタが接続され、ノードAにトランジスタ21のコレクタが接続されたベース接地回路20と、ノードAに接続され、出力電圧Voutの平均レベルから利得制御信号Vagcを生成する検知回路50と、ベース接地回路20に対して並列に接続されたトランジスタ31を有し、そのベースに利得制御信号Vagcを受ける分流回路30とを備える。検知回路50は、平均レベルの上昇に応じてトランジスタ31を流れる電流が大きくなるように利得制御信号Vagcを生成する。

(もっと読む)

1 - 20 / 221

[ Back to top ]