Fターム[5K029EE18]の内容

直流方式デジタル伝送 (8,390) | 通信方式 (506) | 通信制御 (45) | 伝送単位の操作(例;直並列変換) (15)

Fターム[5K029EE18]に分類される特許

1 - 15 / 15

送信装置、受信装置及びシリアル伝送システム

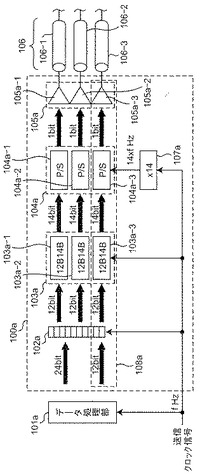

【課題】24ビット、36ビットのデータを送信する場合に効率的なデータ符号化及び復号化方式を行うシリアル伝送システムを提供する。

【解決手段】自然数n×12ビットのパラレルデータをn個のシリアルデータに変換して各自然数mビットの送信信号を送信する送信装置であって、入力されるパラレルデータを12ビット毎のn個の12ビットのパラレルデータに分割する分割手段と、分割されたn個の12ビットのパラレルデータをそれぞれ14ビットのパラレルデータに12B14B変換して出力する符号化回路と、12B14B変換されたn個の14ビットのパラレルデータをそれぞれ1ビットのシリアルデータにパラレルシリアル変換して出力するパラレルシリアル変換回路と、パラレルシリアル変換されたn個の1ビットのシリアルデータを増幅してmビットの送信信号としてそれぞれn個の伝送路に送信するmビットドライバ回路とを備える。

(もっと読む)

クロックド・シリアル・インタフェース

【課題】様々な波形のコントロール信号を生成し出力できるクロックド・シリアル・インタフェース(CSI)を提供する。

【解決手段】コントロール信号の波形を決定するパターンデータが書換可能に格納される複数のシフトレジスタと、これらシフトレジスタ内のパターンデータに応じてコントロール信号を生成する生成手段と、を備える。具体的には、CSI60は、3つのシフトレジスタ81,82,83を有し、これらシフトレジスタ内のパターンデータに応じた波形のコントロール信号を生成し出力する。

(もっと読む)

データ伝送システムと装置と方法

【課題】高速なデータ伝送を可能としながら、CMOS素子の消費電力の低減を可能とするシステム、装置、方法の提供。

【解決手段】前後して入力される二つのNビット幅データを並列配置したビット幅が2×NのビットのN+Nビット幅データを出力する送信装置において、検出回路(トグル検出器)2は、前記二つのNビット幅データを予め定められた正順で上位側と下位側に配置した第1の配置と、前記二つのNビット幅データを、前記第1の配置とは上位側と下位側を交換した逆順で配置した第2の配置とのうち、前回並列出力したN+Nビットデータから反転するビットの個数が小さい方の配置はいずれであるかを検出して前記配置情報(A)として出力し、ビット幅変換回路3は、前記検出回路2からの前記配置情報(A)にしたがって、前記前後して入力される二つのNビット幅データを配置してN+Nビットデータを並列に出力するとともに配置情報を出力する。

(もっと読む)

ビット変換回路、転送ユニット、通信システム、ビット変換方法及びプログラム

【課題】ビット変換の変換テーブルを小さいゲート規模で実装したビット変換回路、転送ユニット、通信システム、ビット変換方法及びプログラムを提供する。

【解決手段】例えば、8b/10bエンコーダ11によれば、変換後のデータが有する‘0’と‘1’の数が一致するか否かに応じて、8b/10b変換の際に利用するエンコードテーブルのパターン分けを行う。そして、入力データがデータを示すDコードであるとき、‘0’と‘1’の数が同じである場合には、入力データの数が同じであることを利用して算出し、そうでない場合には、エンコードテーブルに従って片方の極性の変換を行った後、インバータにより他方の極性の変換を行う。

(もっと読む)

送信機および通信システム

【課題】周波数の変化に対応でき、且つクロストークに起因するジッターの低減を図ることができる送信機、および通信システムを提供する。

【解決手段】送信機2は、発振回路4と、送信部5とを備える。発振回路4は、基準クロックCKrefを入力して、同一の周期を有すると共に位相が互いに異なるN相(Nは2以上の整数)のクロックCK1〜CKNを生成して出力する。送信部5は、発振回路4から出力されたクロックCK1〜CKNを入力して、このクロックCKn(nは1以上N以下の各整数)にシリアルデータ信号Snを同期させて高速シリアル伝送線路Lnを介して受信機3に送信する。

(もっと読む)

高速シリアル伝送システム及びその制御方法

【課題】伝送システムの使用環境に応じて伝送帯域や伝送品質を柔軟に適用制御する。

【解決手段】高速シリアル伝送システム200が、無線通信に適した所要の伝送帯域に基づいて、所要の伝送帯域に適応するよう伝送レートの設定を適応制御する伝送レート設定制御部105を有しており、伝送レート設定制御部105が、適応制御を行うか否かの指定及び伝送レートの制御範囲の指定を行い得る。また、無線通信に適した所要の伝送品質、及び受信される信号の伝送品質状況に基づいて、所要の伝送品質に適応するよう送信振幅及び送信プリエンファシスの設定を適応制御する送信振幅プリエンファシス設定制御部108を有しており、適応制御を行うか否かの指定及び送信振幅及び送信プリエンファシスの制御範囲の指定を行い得る。

(もっと読む)

シリアル通信装置

【課題】制御信号に適したシリアル伝送によって配線数を削減することが可能なシリアル通信装置の提供する。

【解決手段】複数の送信制御信号を送信シリアル信号に変換して外部に出力するP/S変換器と、外部から入力された受信シリアル信号を外部から入力された受信転送クロックを用いて複数の受信制御信号に変換するS/P変換器と、送信シリアル信号に同期した送信転送クロックを外部に出力するクロック出力回路と、受信シリアル信号に同期した受信転送クロックをS/P変換器に出力するクロック入力回路とを具備する。

(もっと読む)

送信装置、受信装置および同期式シリアル通信システム

【課題】データ種別の切換誤検出が容易で、2以上の種別データを通信する際にデータ種別の切換え判別を容易に行える同期式シリアル通信システムの提供を目的とする。

【解決手段】データ信号設定をクロック信号の立上り(または立下り)エッジで行い、データ信号読込みをクロック信号の立下り(または立上り)エッジで行う同期式シリアル通信において、2種類のデータを送る場合にデータ種別の切換え時にデータ信号設定をクロック信号の立下り(または立上り)エッジで行い、データ信号読込みをクロック信号の立上り(または立下り)エッジで行う様に切換え、データ種別の区間中それを継続することを特徴とする。

(もっと読む)

信号伝送システム、信号伝送方法及びプログラム

【課題】シリアルデータバスを用いた多対1ノード間のデータ転送を簡単な構成で良好に行うことができる信号伝送システム、信号伝送方法及びプログラムを提供する。

【解決手段】シリアルバス4を介して複数のスレーブノード3から1つのマスターノード1へのデータ伝送する際、シリアルデータに埋め込まれるクロック信号の位相を予めマスターノード1側の基準クロック信号に合わせることにより、スレーブノード3が切り換わっても再同期のオーバーヘッドが生じないようになる。

(もっと読む)

音声出力装置

【課題】伝送フォーマットの異なる各デジタルオーディオ信号を外部出力する音声出力装置において、デジタルオーディオ信号を外部出力するための端子数を削減すること。

【解決手段】第一の伝送フォーマットに基づいたデジタルオーディオ信号を出力するベースバンド処理部12を有する音声出力装置1において、オーディオデータ信号、LRチャンネル選択信号及びビットクロックからなるデジタルオーディオ信号が、第一の伝送フォーマットと異なる第二の伝送フォーマットに基づいた形式となるようにオーディオデータ信号を変換する変換回路13を備える。第一及び第二の伝送フォーマットのデジタルオーディオ信号をそれぞれ外部出力する複数の出力端子21〜24のうち、第一及び第二の伝送フォーマットで共通しているビットクロック及びLRチャンネル選択信号の各出力端子21,23を共用化する。

(もっと読む)

信号伝送システム及び送信装置及び受信装置

【課題】送信する信号数の増加に伴う受信回路の複雑化、大規模化を防止する。

【解決手段】送信装置1000と受信装置2000とを具備する信号伝送システムであって、送信装置は、第1の信号A、又は第1の信号Aと第1の信号に隣接する第2の信号Bとの排他的論理和である第3の信号102aのいずれかを出力する論理信号出力部103と、第1の信号と第2の信号の、論理値0から論理値1への遷移状態、又は論理値1から論理値0への遷移状態に基づいて、論理信号出力部に第1の信号と第3の信号のいずれを出力させるかを判定する判定部101と、論理信号出力部からの出力信号A’と、第2の信号B(B’)を受信装置に出力する信号出力部104とを備え、受信装置は、送信装置から出力された論理信号出力部からの出力信号A’と、第2の信号Bとを受信する受信部と、論理信号出力部からの出力信号A’から第1の信号を復元する復元部201とを備える。

(もっと読む)

シリアル通信のシステム及び方法

【課題】 クロック信号線及びデータ信号線以外に信号線を増やすことなく、シリアル通信の同期を可能とする。

【解決手段】 クロック(CLK)信号202及びコマンド(CMD)信号203を供給する装置本体100と、該装置本体にステータス(STS)信号204を供給する外部装置20bとの間で、CLK信号に同期してシリアル通信を行うときに、装置本体で、CMD信号のレベルを変化させて通信の開始を通知し、外部装置では、CMD信号から分岐したCMD割込み信号205のレベルの変化を検出して、通信の開始を判断する。

(もっと読む)

エンコーダ装置およびデコーダ装置

【課題】 3本の伝送路を用いてより高速にデータを伝送する。

【解決手段】 第1及び第2の3ビットラッチは、クロックN100の立ち上がり及び立ち下がりで交互にホールド動作を繰り返す。第1の状態遷移部は、クロックの立ち上がりに対応して、3ビット信号N154〜N156をデータ112の値で決まる方向に遷移し、クロックでホールドして反転した結果を第1のラッチ出力N134〜N136へ出力する。第2の状態遷移部は、クロックの立ち上がりに対応して、3ビット信号N134〜N136を、データ113の値で決まる方向に遷移し、クロックでホールドして反転した結果を第1のラッチ出力N154〜N156へ出力する。第3の3ビット2入力1出力マルチプレクサは、クロックN102及びN103により第1及び第2の3ビットラッチの出力のうち後から変化した方を選択し、エンコード出力N187〜N189とする。

(もっと読む)

データ転送方式

【課題】commonとなるGNDの弱い状態(GND間にインピーダンスの発生するような)下において発生していたクロストークやグランドバウンスによる論理反転・発振等を回避することができるデータ転送方式を提供すること。

【解決手段】送信側領域と受信側領域との領域を持ち、送信側領域中には調整クロック制御手段、同期データラッチ、調整クロック・データラッチを具備し、受信側領域中には調整クロック制御手段、同期データラッチ、調整クロック・データラッチを具備し、前記調整クロック制御手段に対して制御パラメータを設定する調整クロック制御指示手段をシステム中に具備する。

(もっと読む)

シリアルリンクトランスミッタにおける節電

シリアルリンクトランスミッタにおける節電の局面を説明する。局面は、セグメントのパラレル配列を設けることを含み、各セグメントは、シリアルリンクトランスミッタのプレバッファと出力段回路とを備え、各セグメントは、独立にイネーブルされて、シリアルリンクトランスミッタの信号路における実質的に一定の伝搬遅延を維持しながら、複数の電力レベルと、プリエンファシスの複数のレベルとを実現する。さらなる局面は、セグメントにおける制御可能なアイドル状態を実施するためのプレバッファ段回路におけるバイパス路と、スルーレート制御機能のためのセクション化された部分として、プレバッファ回路における末尾電流および抵抗負荷要素とを設けることを含む。トランスミッタ信号路におけるプリエンファシス遅延回路を有する制御要素を設けて、プリエンファシス遅延回路の最終遅延化ビットの反転を可能にして、プリエンファシスの重みの極性変更を実現することも含まれる。

(もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]