Fターム[5K029HH14]の内容

直流方式デジタル伝送 (8,390) | 受信部 (1,135) | サンプリングをするもの (131) | 1ビット内のサンプリング点が多数あるもの (30)

Fターム[5K029HH14]に分類される特許

1 - 20 / 30

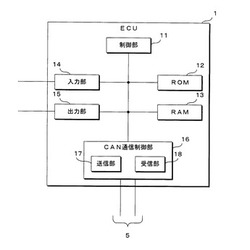

電子装置

通信システム、通信装置、通信方法及び通信パラメータ決定方法

【課題】リンギングの影響を低減し、通信の高速化を実現可能な通信システム、通信装置、通信方法及び通信パラメータ決定方法を提供する。

【解決手段】ECU1の送信部17が、送信データがドミナントの場合に、1ビット分の送信時間より短いパルス幅Tpに亘る所定信号レベルの信号を通信線5へ出力し、その後は通信線5へ信号出力を停止してハイインピーダンス状態とすると共に、送信データがレセシブの場合に、通信線5へ信号出力をせずハイインピーダンス状態とする。またECU1の受信部18が、サンプリング期間Tdに亘って信号線5の信号レベルをサンプリングし、サンプリングした信号レベルの平均値を算出し、算出した平均値が閾値を超えるか否かに応じてドミナント/レセシブの判定を行う。

(もっと読む)

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

誤り率測定装置及び誤り率測定方法

【課題】CDRを用いずにデータの受信を可能にする。

【解決手段】データ処理部4は、シフトされたデータの変化点に基づくヒストグラム上で計数値が最大値を示すビットの位置を変化点とし、この変化点から次の変化点までの略中央にデータの取得位置が来るべくシフト量を算出する。タイミング制御部6は、リファレンスクロックと同期が取れ、入力データのビットレートに応じたクロックを出力し、このクロックの周期を、シフト量が所定の限界処理ビットを超えたときに入力データをシフトするクロックの1周期だけ増減して調整する。FIFO5は、ドロップされたデータを順次取り込んで保持する。この保持されたデータは、シフト量が限界処理ビットを超えたか否かに応じたタイミング制御部6のクロックのタイミングにより取り出される。

(もっと読む)

受信装置及び通信システム

【課題】伝送路上のノイズによるメイン処理の実行効率低下が発生することなく、且つ、CPUなどに通信処理のための外部割込ポートを必要としない受信装置及び通信システムを提供する。

【解決手段】CPU11が第1サンプリング部21及び第2サンプリング部22を備え、第1サンプリング部21及び第2サンプリング部22が、プリアンブルの各ビットのビット幅と同じサンプリング周期で、且つ、ビット幅の1/2の時間ずらしたタイミングで、入力ポート11aに入力される2値信号のサンプリングを行う。第1サンプリング部21又は第2サンプリング部22の少なくとも一方でプリアンブルを検出した場合に、CPU11がデータの受信を開始することができる。リモコン3及びUHF受信IC12等は、プリアンブルに係る誤差が許容範囲内となるようにCPU11へ信号を送信する。

(もっと読む)

信号受信装置及び信号処理方法

【課題】簡易な構成で、PPM信号を確実に再生するために正確にPPM信号をサンプリングできる信号受信装置を提供する。

【解決手段】パルス位置変調信号のうち検出対象区間から任意のHパルスの立ち上がりまたは立ち下がりエッジを開始点として設定する第1の設定手段と、前記検出対象区間における複数のHパルスの間隔に基づいてサンプリング周期を算出する算出手段と、前記検出対象区間について、前記開始点から前記サンプリング周期の倍数を基準点とし、前記基準点からの前記複数のHパルスの発生位置を検出する検出手段と、前記複数のHパルスの発生位置についてヒストグラムを生成する生成手段と、前記基準点に前記ヒストグラムでピークとなる値を加えた位置を前記パルス位置変調信号における再生対象信号区間のサンプリング点と決定する決定手段と、前記サンプリング点に基づいて前記再生対象信号区間を再生する再生手段とを有する。

(もっと読む)

信号処理装置、信号処理方法、及び信号処理プログラム

【課題】所定信号のアイダイアグラムにおけるアイ開口を高精度に最適化すること。

【解決手段】信号処理装置は、入力信号の所定帯域を増幅して出力信号を出力するイコライザー手段と、イコライザー手段により増幅された出力信号を、多相クロック方式で、かつ振幅方向へオフセットさせつつサンプリングを行うサンプラー手段と、サンプラー手段によりサンプリングされた出力信号に基づいて、出力信号のアイダイアグラムにおけるアイ開口の面積情報を算出する面積情報算出手段と、面積情報算出手段により算出されたアイ開口の面積情報に基づいて、イコライザー手段の増幅を制御する制御手段と、を備えている。

(もっと読む)

オーバーサンプリング回路

【課題】オーバーサンプリング型CDR回路で用いる多相クロックの相互の位相差が等間隔になるように高精度に位相を補正できるオーバーサンプリング回路を提供する。

【解決手段】多相クロックを生成する多相クロック生成部200と、多相クロックの位相差を検出して、該検出結果に基づいて位相制御信号を発生する位相制御部205と、多相クロックの本数分の遅延回路を有し、多相クロックをそれぞれの遅延素子に入力された信号の通過時間を、位相制御信号に基づいて調整することで多相クロック間の位相差を調整する位相調整部203と、を備え、各遅延回路300は、直列に接続されたサイズの異なる複数のインバーターと、該複数のインバーターの後段に接続したインバーターと、からなり、複数のインバーターから選択される一つインバーターの出力抵抗と、後段に接続したインバーターの入力容量の積に基づいて通過時間を調整する。

(もっと読む)

非対称な遅延に関して通信システムを診断する方法及び装置

本発明は、非対称な遅延に関して通信システムを診断するための方法及び装置に関し、非対称な遅延は、少なくとも1つの閾値と比較される。 (もっと読む)

シリアル通信方式

【目的】

非同期シリアル通信において、機器間での同期ずれが発生することによる受信データの誤りを防ぐことを目的とする。

【構成】

調歩同期方式や独立同期方式により複数のデータをシリアル伝送する方式の非同期シリアルデータ通信方法において、k個のサンプリング値に0からk−1までの番号を付与するサンプリング番号付与部と、k/2番目のサンプリング値とk/2−1番目のサンプリング値を比較するサンプリング値比較部と、前記サンプリング値比較部により2つの値が異なる時にk−1番目のサンプリング値を受信データとする代表値決定部と、k−1番目のサンプリング位置をk/2番目になるようにサンプリング番号を修正するサンプリング番号修正部からなるシリアル通信方式。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】通信の信頼性を保ちつつ応答性を向上させる。

【解決手段】増幅部51乃至復調部53は、符号化プリアンブルと符号化データを含む符号化フレームが送信元から送信されてきた場合、符号化フレームをアナログ信号として受信する。サンプリング部61は、符号化フレームを、ビット区間を単位として、1単位につき2以上のサンプリング数でサンプリングする。ビット判別部62は、1単位分のサンプリングの結果に基づいて、ビット区間の符号化前のビットを判別する。ビットサンプリング数変更部81は、符号化プリアンブルに対するサンプリングの結果に基づいて、符号化データに対するサンプリングを行う場合のビットサンプリング数を変更する制御を行う。本発明は、例えば、パッシブエントリシステムに適用できる。

(もっと読む)

非同期シリアルデータ受信装置

【課題】オーバーサンプル方式の非同期シリアル通信におけるクロックの周波数の調整を、低コストで精度高く行うことができるようにする。

【解決手段】発振器121は、周波数f0の原振クロックを生成し、分周器122は、原振クロックを分周して周波数fosのオーバーサンプル用クロック信号を生成し、オーバーサンプラ123が、受信データをオーバーサンプルする。分周器128は、原振クロックを分周して周波数fbrの受信用クロック信号を生成する。ボーレート計測部125は、信号ライン120に伝送される信号のボーレートを計測することで、送信側のクロック周波数を得る。演算部126が、分周器128に設定すべき分周比mを演算し、記憶部127に記憶された分周比mを16で除することにより、演算部129が分周器122に設定する分周比oを演算して、記憶部130に記憶させる。

(もっと読む)

無線装置

【課題】パルスの形状が変動しても、正確な波形サンプルが可能な無線装置を提供する。

【解決手段】入力信号とクロック信号を同期させる同期装置は、入力信号を、所定の間隔の第1と第2のサンプルタイミングでサンプルするサンプル手段102,103と、同期引き込み時に、第1と第2のサンプルタイミングをともにずらし、同期追従時に、第1と第2のサンプルタイミングの間隔を狭める遅延制御手段112とを備える。同期状態判定部105は位相誤差算出部104から出力された位相誤差量から同期しているか否かを判定し、遅延量制御部106に同期状態を出力する。遅延量制御部106は位相誤差算出部104から出力される位相誤差量と同期状態判定部105から出力される同期状態から、可変遅延器107および108に現在設定している遅延量の増減を制御する。

(もっと読む)

ユニットインターバルに含めるオーバーサンプルデータの決定方法

【課題】本発明は、どのオーバーサンプルデータを、受信信号のビット値を決定する際に使用されるオーバーサンプルデータの異なるグループ(ユニットインターバル)の一部にすべきかを決定するための回路、方法、及びシステムを提供する。

【解決手段】一部の実施形態では、チップは、受信信号からオーバーサンプルされたデータを生成するためのサンプリング回路と、オーバーサンプルデータのうちのいずれを異なるユニットインターバルの一部分にすべきかを決定するためのロジックとを含み、ユニットインターバルの一部は、ユニットインターバルに通常含まれるオーバーサンプルデータの数とは異なる数のオーバーサンプルデータを有する。他の実施形態についても説明され特許請求される。

(もっと読む)

クロックデータ復元装置

【課題】トランスミッタ・クロック・ジッタや符号間干渉が大きい場合であっても安定してクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、サンプラ部10、検出部20、オフセット決定部30、クロック出力部40およびDA変換部50を備える。クロック信号CK,CKXの位相は、入力デジタル信号の位相と一致するよう調整される。サンプラ部10におけるオフセット付与量(±Voff)は、値D(n-1)がハイレベルである場合の第1信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整され、値D(n-1)がローレベルである場合の第2信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整される。復元されたクロック信号として、クロック信号CK,CKXの何れかが出力される。復元されたデータとして、デジタル値D(n)の時系列データが出力される。

(もっと読む)

プログラマブルロジックデバイス用のデジタル適応回路網および方法

【課題】プログラマブルロジックデバイス用のデジタル適応回路網および方法を提供すること。

【解決手段】本発明は、着信データ信号の等化を制御する方法を提供する。該方法は、該データ信号の中の2つの連続する異なる値を有するビットを検出することと、該2つのビット間の該着信データ信号における遷移が、比較的遅いか、あるいは比較的早いかを決定することと、該遷移が、比較的遅い場合、該着信データ信号の該等化を増加させることとを包含する。

(もっと読む)

オーバーサンプリング回路及びオーバーサンプリング方法

【課題】等間隔の位相でオーバーサンプリングされたデータを生成することができるオーバーサンプリング回路及びオーバーサンプリング方法を提供する。

【解決手段】多相クロックを生成する際に、全ての回路が等価であるとは考えず、それぞれ異なる遅延時間を持つ遅延部を用いて多相クロックを生成し、そのサンプリングデータを元に等間隔の位相でオーバーサンプリングされたデータを生成するものである。また、位相の検出にはサンプリングされたデジタルデータを用いるので、小さい回路規模で高精度な位相検出を行う事ができる。従って、等間隔の位相でオーバーサンプリングされたデータを生成することができる。

(もっと読む)

ビット長のカウンタを備えた非同期式シリアルデータ伝送用の集積回路

【課題】ビット長のカウンタを備えた非同期式シリアルデータ伝送用の集積回路を提供する。

【解決手段】本発明は、非同期式シリアルデータ伝送用の集積回路(7)であって、

非同期式シリアルデータ(d)を与える入力端子(30)と、

該入力端子に与える走査クロック(aclk)によって非同期式シリアルデータ(d)を走査する走査器(5)と、

走査クロック(aclk)のクロック数(m)またはビット長のカウンタクロック(xclk)の計数によってビット時間を決定するビット長のカウンタ(4)と、を構成するための構造を有する集積回路において、

ビット長のカウンタ(4)のクロック数(m)の可変設定用のビット長端子(32)が集積回路(7)及び/またはビット長のカウンタ(4)に構成されている集積回路に関する。

(もっと読む)

1 - 20 / 30

[ Back to top ]