Fターム[5K029LL08]の内容

直流方式デジタル伝送 (8,390) | 基本回路 (285) | 遅延回路;単安定マルチ (67)

Fターム[5K029LL08]に分類される特許

61 - 67 / 67

無線通信方法および機器

本発明の1つの態様は、ある無線網において、異なる無線網で動作するように設計されたデバイスを動作させることに関する。1つの態様において、GSM無線網で動作するように設計されたデバイスを、PHS無線網での通信に用いることができる。  (もっと読む)

(もっと読む)

信号受信回路及び信号受信方法

【課題】広いノイズ・マージンを有し、実装面積が小さく、且つ低消費電力で動作する信号受信回路を提供する。

【解決手段】閾値制御端子CNTに入力される閾値制御電圧信号の電圧値により論理閾値電圧を連続的に制御することが可能な論理閾値可変インバータ(VT−INV)2の入力端子に入力される入力信号Vinを、閾値制御端子CNTの閾値制御端子に入力する構成とする。この構成により、VT−INV2の論理閾値電圧にシュミットトリガ・インバータと同様のヒステリシス特性を持たせ、ノイズ・マージンを広げることができる。また、実装面積・消費電力はCMOSインバータと同程度に抑えられる。

(もっと読む)

パルス駆動回路及びパルスリンギング抑制回路

【課題】 本発明は、パルス駆動回路及びパルスリンギング抑圧回路において、入力信号が急激に変化するようなとき、例えば、周波数が高く、ゲインが高い時の入力信号の立ち上がり、立ち下がり時の電圧変動を出力信号に伝えてリンギングをリンギング抑制回路により有効に抑える様にする。又、リンギング抑制調整回路の制御信号を切り替えることによってリンギング抑制回路を調整し、入力信号の電圧変動を伝えるゲインと遅延時間をそれぞれ制御することで、リンギングが変化した場合に対してもリンギングを抑制する様に出来るものを得る。

【解決手段】 本発明のパルス駆動回路及びパルスリンギング抑圧回路は、パルス駆動回路1にリンギング抑制回路5a,5bを設け、入力パルスの立下り或いは立下りを出力信号の立ち上がり或いは立下りにより交流的に加算し、出力波形に生ずるリンギングを軽減すると共にリンギング抑制回路5a,5bの遅延量又は/及び遅延時間τを調整可能なものを得る。

(もっと読む)

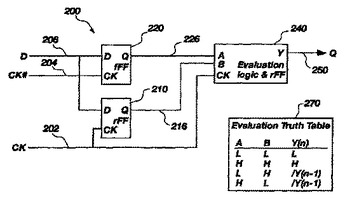

高速入力サンプリングのための方法及び装置

信号の高速入力サンプリングのための信号サンプラ及び方法が記述される。第1のサンプラはクロック信号の立ち上がりエッジでデータ信号をサンプリングして第1のサンプリングされた信号を生成する。第2のサンプラは反転クロック信号の立ち下がりエッジでデータ信号をサンプリングして第2のサンプリングされた信号を生成する。第1及び第2のサンプリングされた信号は組み合わされて次の信号サンプラ出力を決定する。評価は、第1及び第2のサンプリングされた信号がアサートされたならば出力信号をアサートすること、第1及び第2のサンプリングされた信号がネゲートされたならば出力信号をネゲートすること、及び、第1及び第2のサンプリングされた信号が反対の論理状態であるならば出力信号を切り換えることを含む。信号サンプリングの信号サンプラ及び方法は、半導体ウェーハ上に作成されて電子システムに含まれる半導体デバイスに組み込まれる。  (もっと読む)

(もっと読む)

フェイルセーフ差動増幅器回路

周波数限界よりも低い周波数に結びつけられた差動信号の欠如か又は低過ぎる差動信号を検出する差動入力フェイルセーフ回路構成を開示した。ここで、最終的なセーフ条件が検出されて、信号が送られる。前記フェイルセーフ回路構成からの出力信号は、所与の状態にホールドされる。該所与の状態とは、差動入力信号の無効表現である。限界周波数ロールオフによって補助増幅器を相補的にオフセットする周波数検出器が、フェイルセーフ条件を検出するために使用される。更には、フェイルセーフ回路がアクティブになる前に、いくらかの時間が存在するフェイルセーフ条件を必要とする遅延回路が使用される。初期化回路構成が、適切な電力投入条件を保証する。ここで、該回路構成は、前記フェイルセーフ条件を検出するためにイネーブルにされて、信号の以前の状態とは無関係に、信頼できるフェイルセーフ動作を保証する。  (もっと読む)

(もっと読む)

デターミニスティックジッターイコライザ

シリアルデータ通信のためのイコライザは、デターミニスティックジッターの効果を補うために設定できる。イコライザは、負荷サイクルひずみジッターと同様、受信したシリアルデータストリームに、データ依存ジッターの効果を補うために設定できる。イコライザは、以前に受信した一つ以上のシンボルの値を判断し、回復したシンボルと比較するために設定することが出来る。イコライザは、受信データストリームの一部に基づく、データ経路に遅延を取り込むために、シリアルデータ経路に位置する可変遅延器を調整することが出来る。イコライザは、回復したシンボルと、一つ以上の以前に受信したシンボルのいずれかと異なる場合に、遅延を変化するように設定することができ、回復したシンボルと、一つ以上前に受信したシンボルのいずれかと同じ場合に、遅延を一定に維持するように設定することができる。  (もっと読む)

(もっと読む)

ジッタ測定装置及びそれを内蔵した集積回路

【課題】 パルス信号の周期の測定を必要とせずに、また、必要な測定精度に応じてパルス数の制限無くジッタ量を測定することができるジッタ測定装置とそれを内蔵した集積回路を提供する。

【解決手段】 ジッタ量を測定すべきパルス信号1は、m分周回路13で分周された後、パルス遅延回路14でnビットの遅延パルスとなり、nビットフリップフロップ16にクロック入力として与えられる。nビットフリップフロップ16の出力は第1のジッタ情報ラッチ回路17に格納され、次の回で新たなデータが第1のジッタ情報ラッチ回路17に格納されると同時に前回のデータは第2のジッタ情報ラッチ回路18に移される。第1及び第2のジッタ情報ラッチ回路17,18のデータがジッタ比較回路19で比較され、パラレル/シリアル変換回路20を経て出力される。

(もっと読む)

61 - 67 / 67

[ Back to top ]