Fターム[5K029LL08]の内容

直流方式デジタル伝送 (8,390) | 基本回路 (285) | 遅延回路;単安定マルチ (67)

Fターム[5K029LL08]に分類される特許

41 - 60 / 67

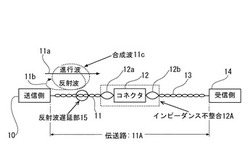

信号伝送装置及び信号伝送方法

【課題】通信の品質を向上させること。

【解決手段】送信側10からの複数のパルス幅を有する信号を伝送路11Aである、ツイストペア線の線路11,13及び中間コネクタ12を介して受信側14に伝送する際、線路11に形成された反射波遅延手段としての反射波遅延部15により、信号の進行波11aが反射して発生する反射波11bを、進行波11aの最小パルス幅のλ/4時間となるように遅延させ、進行波11aに対し波形の乱れを生じさせる反射波11bの影響を小さくし、合成波11cの正の振幅と負の振幅の各々の周期(半周期)での時間差を小さくして合成波11cのジッタが少なくなるようにした。

(もっと読む)

差動信号伝送システム及びその信号線路のスキュー調整方法

【課題】高速のデジタル信号を2本のペアとなる信号線路で伝送する場合において、レシーバ回路の直前での同相雑音印加にも強い差動信号伝送システムを提供することにある。

【解決手段】本発明は、差動信号を送信するドライバ回路10と前記差動信号を受信するレシーバ回路40とを設け、前記ドライバ回路から送信される差動信号と前記レシーバ回路で受信される差動信号とを少なくとも2つの信号線路30を用いて接続して構成した差動信号伝送システムであって、前記ドライバ回路において、前記差動信号の一方の信号と他方の信号との間に任意の時間差をつけて送信するように構成したことを特徴とする。

(もっと読む)

送信装置、通信システム、およびインパルス無線変調方法

【課題】インパルス無線通信において、繰り返しデータから生じる離散成分を抑圧すること。

【解決手段】プレフィックスビット生成部104は、1つまたは複数のプレフィックスビットをランダムに生成し、プレフィックスビット結合部106は繰り返しソースデータにプレフィックスビットを付加する。最初のプレフィックスビットは、繰り返しソースデータの先頭に付加する。差動符号化部108は、プレフィックスビットが付加されたシーケンス107に対し差動符号化を施し、IR変調部110は差動符号化後のシーケンス109に対しインパルス無線変調を施し、RF送信部112は、インパルス無線変調信号に所定の無線送信処理を施し、アンテナ114を経由して送信する。

(もっと読む)

ディジタル伝送システムおよびディジタル伝送方法

【課題】波形劣化要因の状況が高速ないし低速(長周期)で変動する伝送路どちらに対しても対応可能であり、伝送品質劣化を抑圧し、安定した通信を可能にする。

【解決手段】伝送キャリアには光を使用し、変調光を偏波スクランブルし、伝送路としては光ファイバを使用し、等化特性を予め固定して設定したトランスバーサル型等化回路を有する受信装置を用いて偏波スクランブルされた変調光を受信して復調する。また、伝送路の途中に一つないし複数の偏波スクランブル回路を挿入して変調光を偏波スクランブルすることもできる。この場合には、送信側における偏波スクランブルに代えて伝送路の途中に挿入された偏波スクランブル回路によって変調光を偏波スクランブルすることもできる。

(もっと読む)

プリエンファシス自動調整方法及びデータ伝送システム

【課題】回路の簡略化と共に、自動調整時間の短縮化等を図る。

【解決手段】シシングルパルスパターンの信号がシングルパルスパターン発生部11から出力される。セレクタ13を通った信号は、送信回路14で互いに位相が反転した2つの信号にされて受信回路20へ伝送される。Teye判定部21は、上記2つの信号とサンプリングクロック制御部22からサンプリングクロックとによってアイ波形の時間方向のアイ開口を計測する。調整制御部23は、計測されたアイ開口と目標値との大小を判定し、判定結果を送信回路14へ送信する。送信回路14は、判定結果に基づいてプリエンファシスを調整する。

(もっと読む)

データ受信装置

【課題】EOP期間とその前期間で安定した受信データを得ることができ、シリアルデータを安定して受信することができるデータ受信装置を提供すること。

【解決手段】データ受信装置100は、第1の信号線101aと第2の信号線101bを差動入力とする受信用コンパレータ102と、第1の信号と第2の信号が逆位相から同一位相に変化したときの論理出力をトリガ信号として出力するNOR回路105と、受信用コンパレータ102の出力RCVを、NOR回路105からのトリガ信号で取り込み保持するD−FF回路107とを備え、選択回路108は、第1の信号線101aの第1の信号と第2の信号線101bの第2の信号が互いに逆位相の場合には受信用コンパレータ102出力を選択するとともに、第1の信号と第2の信号が逆位相から同一位相に変化した場合にD−FF回路107に保持された値を受信データとして出力する。

(もっと読む)

信号伝送システム

【課題】

ラッチポイントとノイズの位置関係が最適になるように遅延時間を制御し、信号波形品質の悪化を避ける。

【解決手段】

少なくとも1つの出力回路と、少なくとも1つの入力回路と、それぞれの入出力回路に接続する伝送線とを有するインターフェース回路において、遅延時間調整回路と遅延時間制御回路を設置する。遅延時間調整回路は信号を伝送する時間を調整する機能を有し、遅延時間制御回路は遅延時間調整回路の遅延時間を制御する機能を有する。遅延時間制御回路はラッチポイントとノイズの位置関係が最適になるように遅延時間を決定し、遅延時間調整回路に通知する。遅延時間調整回路は遅延時間制御回路が決定した遅延量に従い遅延時間を設定する。

(もっと読む)

差動信号制御回路

【課題】差動信号制御回路における貫通電流を完全に排除し、かつ位相の揃った差動出力信号を出力することを可能とする。

【解決手段】差動入力信号(Ai,Bi)を入力して差動出力信号(Ao,Bo)の各々を出力するための2つのプッシュプル回路(NMOSトランジスタN1,N2とPMOSトランジスタP1,P2からなる)を備えた差動信号制御回路において、差動出力信号の出力レベルが反転する際に、各プッシュプル回路が必ずハイインピーダンス状態を経由するようにするために、一方の差動入力信号を遅延する第1の遅延回路11と、他方の差動入力信号を遅延する第2の遅延回路12と、これらの第1,第2の遅延回路11,12の出力と差動入力信号とを入力して各プッシュプル回路を制御するための制御信号を出力する条件判定回路10を備えた。

(もっと読む)

直流成分除去フィルタ、方法およびプログラム

【課題】 回路規模の削減および処理内容の簡素化が可能な直流成分除去フィルタ、方法およびプログラムを提供すること。

【解決手段】 直流成分除去フィルタ100は、入力データに対してN個の移動平均を計算する遅延回路110、112、加算器120、122、D型フリップフロップ130、係数乗算器132からなる移動平均演算手段と、移動平均の計算対象となっているN個の入力データの中から中央の入力データを取り出してこの入力データの値から移動平均値を減算する加算器124からなる減算手段とを備えている。

(もっと読む)

信号伝送装置

【課題】信号伝送装置に関し、クロストークにより発生する信号のエッジ部の時間的な揺らぎを抑制することを課題とする。

【解決手段】複数の信号を送信する送信部と、複数の信号を受信する受信部と、送信部から出力された複数の信号をそれぞれ受信部へ伝送する複数の配線を収容したケーブルと、信号を遅延させる少なくとも2つの遅延部とを備え、第1の遅延部が、前記送信部と、第1の信号を伝送するケーブル内の第1の配線との間に配置され、第2の遅延部が、第2の信号を伝送するケーブル内の第2の配線と前記受信部との間に配置され、前記ケーブルの第1の配線と前記ケーブルの第2の配線との伝播遅延時間が等しく、前記第1の遅延部と第2の遅延部との信号遅延時間が等しく、第1の信号と第2の信号とが遅延部の遅延時間分ずれたタイミングでケーブル内を伝送されることを特徴とする。

(もっと読む)

クロックフリー起動回路

入来データストリームからデータを回復させるための回路を提供する。一実施形態に係る回路は、キャパシタと、キャパシタを充電するためのほぼ一定の電流源とを含む。サブ回路は、入来データストリームにおいて第1の種類の遷移を検出するとキャパシタを放電させる信号を生成し、キャパシタは、少なくとも部分的に放電されると再び充電する。コンパレータは、キャパシタに連結されたノードの電圧を基準電圧と比較し、コンパレータは、ノードの電圧が基準電圧よりも高ければ第1の信号を出力し、ノードの電圧が基準電圧よりも低ければ第2の信号を出力する。第1の信号は第1の論理値に関連付けられ、第2の信号は第2の論理値に関連付けられる。  (もっと読む)

(もっと読む)

タイミングで出力データを初期強化する出力ドライバー及び出力ドライブ方法

【課題】ドライブされる電圧レベルの強化が要求されない出力ドライバー及び出力ドライブ方法の提供。

【解決手段】タイミングで出力データを初期強化する出力ドライバー及び出力ドライブ方法を開示する。本発明の出力ドライバーは、選択信号を発生する選択信号発生部、基準データとして発生する基準データ発生部、及び選択部を備える。前記選択信号は、所定の持続数以上のビット区間の間に同一の論理状態を持続した後に発生する前記入力データの遷移時点で活性化状態である。そして、前記基準データは、前記入力データに対して、前記ビット区間より短い遅延時間だけ遅延する。前記選択部は、前記選択信号に基づいて、前記入力データ及び前記基準データのいずれか一つの論理状態の遷移に応答して前記出力データの論理状態を遷移させるように駆動される。

(もっと読む)

バースト先頭検出回路

【課題】バースト信号の先頭を検出して、バースト信号間の無信号期間のノイズを除去する。

【解決手段】バースト先頭検出回路は、バースト信号AOP,AONを入力とするハイパスフィルタ3と、ハイパスフィルタ3を通過したフィルタ出力信号HOP,HONを入力とし、所定のしきい値を超えるフィルタ出力信号の変化を検出するヒステリシスコンパレータ4と、ヒステリシスコンパレータ4によりバースト信号の先頭が検出されるまで、後段の回路へのバースト信号の出力を遮断し、バースト信号の先頭が検出されたときに、バースト信号を後段の回路へ出力するスイッチ6とを有する。

(もっと読む)

主側通信装置および従側通信装置

【課題】複雑な判断フローで複数の受信系信号を高速に処理する必要がなく、機器構成が複雑かつ大型化し、消費電力の増加、機器の高額化のない従側通信装置を実現する。

【解決手段】従側通信装置102において、タイミング調整用の信号である同期用信号発生タイミング情報は、受信した信号Aと同期用信号とを元に同期用信号発生タイミング情報送信部108にて生成され、同期用信号発生タイミング情報として主側通信装置101に送信される。同期用信号発生タイミング情報は主側通信装置101の同期用信号発生タイミング情報受信部105で受信され、ここで読み出された自局の送信した信号Aと、信号Aを受信した従側通信装置102の同期ずれ情報を、送信用信号発生タイミング調整部104に入力し、自局の送信タイミングを変更することで従側通信装置102との同期を行う。

(もっと読む)

出力バッファ回路

【課題】 ディエンファシスが連続する場合でも消費電力の小さい出力バッファ回路を提供する。

【解決手段】 プレエンファシス機能を有し、分布定数回路として振る舞う伝送線路に論理信号を送出するための出力バッファ回路であって、論理信号に論理値を与える第1の信号を入力して伝送線路を駆動するメインバッファ8と、第1の信号と所定の論理関係を有する第2の信号を入力し、第1のバッファと協働して伝送線路を駆動するプリバッファ9と、論理信号の論理値の変化を検出する手段とを備え、第2のバッファの出力インピーダンスは、伝送線路での信号の減衰量が改善される限度において第1のバッファの出力インピーダンスよりも高く設定されており、ディエンファシス状態が連続する場合には、第2のバッファを第1のバッファと協働させて伝送線路を駆動するようにデータ生成部1で制御信号を生成する。

(もっと読む)

符号変換回路

【課題】 NRZ符号のデータ信号をNRZ符号の別のデータ信号に変換する符号変換回路に関し、動作速度の低い回路素子により構成する。

【解決手段】 NRZ符号のデータ信号を複数に分離する多重分離部1と、分離された複数の並列データ信号を入力する変換回路2と、複数の並列出力のデータ信号を多重化する多重化部3とを備え、複数の並列データ信号の中の一つのデータ信号と他のデータ信号を遅延回路11により1ビット遅延したデータ信号との排他的論理和を求める第1の排他的論理和回路12と、この第1の排他的論理和回路12の出力信号と前記並列データ信号の伝送速度のクロック信号との論理積を求める論理積回路13と、この出力信号を入力するTフリップフロップ14と、この出力信号のNRZ符号のデータ信号と前記他のデータ信号との排他的論理和を求める第2の排他的論理和回路15とを含む構成を有する。

(もっと読む)

パルス発生器及びそれを用いた送信機

【課題】 UWB伝送用パルス発生器における構成の簡易化、低消費電力化と、LO信号を使わないことによるLOリークの抑制。

【解決手段】 所定の周期のクロックを与えるクロック発生装置(CLK)と、遅延時間制御機能を持ち前記クロックを遅延させる遅延回路(DLY)と、前記遅延回路から出力される遅延時間の異なる信号同士を比較することで遅延回路一段分の遅延時間差に相当するパルス幅を持つ方形波パルスを、拡散符号により拡散された情報を受け取ることで位相を変調して出力する方形波パルス発生回路(SWPG)と、前記方形波パルス発生回路から異なるタイミングで出力される方形波パルス列を受け取ることにより、前記方形波のパルス幅を持ち所定の振幅でインパルス列を出力し、重ね合わせる振幅制御ユニット(AMPC)を有し、所定の包絡線形状を有するパルスを生成する。

(もっと読む)

クロック抽出回路

【課題】外部より受信した符号化信号からクロック信号を適切に抽出する。

【解決手段】伝送対象のデジタル信号をクロック信号に基づいて符号化した符号化信号を受信して当該符号化信号から前記クロック信号を抽出するクロック抽出回路において、受信した前記符号化信号の立ち上がりエッジ及び立ち下がりエッジを検出して当該検出した旨を示すエッジ検出パルスを生成するエッジ検出部と、前記受信した符号化信号の一周期毎に生成される前記エッジ検出パルスに基づいて、前記一周期毎の前記エッジ検出パルスの生成を契機として位相反転されるマスク信号を生成するマスク信号生成部と、制御可能な遅延時間分、前記マスク信号を遅延させたマスク遅延信号を生成するマスク信号遅延部と、前記マスク遅延信号のエッジに基づいて前記クロック信号を生成するクロック生成部と、前記生成されたクロック信号のデューティ比を所定値に設定すべく、前記マスク信号遅延部の遅延時間を制御する遅延制御部と、を有する。

(もっと読む)

UWB受信機並びにデータ伝送方法及びシステム

本発明は、受信された信号の波形をサンプリングする少なくとも第1の組のサンプリングセルと;前記受信された信号の波形を所定の遅延δでサンプリングする少なくとも第2の組のサンプリングセルと;このようにしてサンプリングされた前記波形の間の相関に依存した情報を供給する少なくとも1つの相関器と;を有するような超広帯域信号受信機に関するものである。 (もっと読む)

光データリンク

【課題】送信器側のオン/オフ時に、電源を介して受信器側に高速で回り込んでくるノイズを効果的に抑制するとともに、劣化のない光出力を送出するようにした光データリンクを提供する。

【解決手段】光受信部と光送信部を1組以上備えた光データリンクであって、光受信部は受光素子11からの信号を、前置増幅器12を経て主増幅部分13に入力するように構成され、光送信部は送信信号が入力された入力バッファ18からの出力を遅延回路16に入力し、この遅延回路により遅延された信号を駆動回路15に入力し、この駆動回路に接続された発光素子14を作動するように構成される。入力バッファ18からの出力を取出して擬似ノイズ信号発生回路17に入力し、この擬似ノイズ信号発生回路で生成された信号出力を主増幅部分13に逆相で入力する。

(もっと読む)

41 - 60 / 67

[ Back to top ]