Fターム[5K046EE10]の内容

有線伝送方式及び無線の等化、エコーの低減 (13,292) | 等化一般 (2,382) | 等化器構成 (876) | 判定帰還型等化器 (122)

Fターム[5K046EE10]に分類される特許

1 - 20 / 122

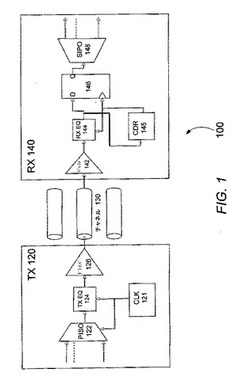

フレキシブルな受信器アーキテクチャ

【課題】高速データインクのための回路網を提供すること。

【解決手段】データリンクのための受信器回路であって、該受信器回路は、第1の等化回路網を含む第1の信号経路と、第2の等化回路網を含む第2の信号経路と、該第1の信号経路および該第2の信号経路のうちの1つの信号経路を選択するように構成された経路選択器回路とを含む、受信器回路。一実施形態において、前記第1の信号経路は、決定フィードバック等化器回路を含む。

(もっと読む)

等化装置及び等化方法

【課題】順方向等化と逆方向等化において適正な周波数オフセット推定値を用いて周波数オフセット補償を行い、等化性能の劣化を抑制する。

【解決手段】RSSI最小位置判定部106は現フレームと次フレームの各同期ワード区間のRSSI値最小位置情報を、RSSI比較部107はRSSI値と閾値とを比較したRSSI閾値比較情報を、それぞれ、周波数オフセット推定値選択部108へ出力する。周波数オフセット推定値選択部108は、RSSI値最小位置情報とRSSI閾値比較情報とにより、順方向等化処理部103と逆方向等化処理部104で求められた周波数オフセット推定値のうち、より正しいと思われる周波数オフセット推定値を現フレームの周波数オフセット推定値とする。周波数オフセット補償部101は、現フレームの周波数オフセット推定値と周波数オフセット補償量とによって次フレームの周波数オフセット補償量を算出する。

(もっと読む)

等化装置及び等化方法

【課題】伝搬路の状態を正しく推定できない場合に等化性能の劣化を適正に回避することができ、受信環境に依らず安定した遅延等化性能を得ること。

【解決手段】伝搬路推定精度判定部104は、伝搬路変動判定部103から出力された伝搬路変動の大きさの推定精度と、遅延波遅延量判定部102から出力された遅延波の遅延量の推定精度とに基づいて、伝搬路推定精度の高/低を判定する。パラメータセット選択部105は、伝搬路推定精度が高いときは伝搬路の状態に応じたパラメータセット(等化処理に使用するタップ数及びタップ係数の更新に用いる忘却係数)を選択し、伝搬路推定精度が低いときは平均的な性能が得られるパラメータセットを選択する。等化処理部106は、パラメータセット選択部105が選択したタップ数及び忘却係数を用いて受信信号の等化処理を行う。

(もっと読む)

受信装置及び受信方法

【課題】回路規模を増大することなく、フェージング環境においても周波数オフセット推定精度を向上させる受信装置及び受信方法を提供する。

【解決手段】順方向等化処理部103のトレーニング部104は、順方向に同期ワードをトレーニングし、周波数オフセット推定部109は、順方向にトレーニングされた同期ワードを用いて順方向周波数オフセット推定値を求める。逆方向等化処理部106のトレーニング部107は、逆方向に同期ワードをトレーニングし、周波数オフセット推定部110は、逆方向にトレーニングされた同期ワードを用いて逆方向周波数オフセット推定値を求める。選択部111は、等化誤差の小さい等化方向の周波数オフセット推定値を選択し、周波数オフセット補償部101は、選択された周波数オフセット推定値に基づいて、受信信号の周波数オフセットを補償する。

(もっと読む)

連続時間判定帰還型等化器

【課題】判定帰還型等化器を用いて、伝送中に歪んだ信号歪みを低減する。

【解決手段】フィルタリング済フィードバック信号を入力から減算するよう適合された加算器と、前記加算器からの出力を受信するよう適合されたシンボル判定装置と、前記シンボル判定装置からの出力をフィルタリングし、前記フィルタリング済フィードバック信号を前記加算器に送信するよう適合され、振幅を調整可能な増幅器および極を調整可能なフィルタを備えるフィードバックフィルタと、最小平均二乗誤差基準に基づいて、極設定および振幅設定の両方を同時に適応させるよう適合された適応アルゴリズムと、を備える。前記加算器、前記シンボル判定装置、および、前記フィードバックフィルタが、伝送中に歪んだ電気信号を再構築するために用いられるフィードバック回路を形成する。

(もっと読む)

等化器

【課題】既知のシンボル部分を含むフレームからなる受信信号を等化処理する等化器で、効果的な等化処理を行う。

【解決手段】後方順方向等化処理手段102、106が既知のシンボル部分より後方の信号に対して順方向等化処理を行い、前方順方向等化処理手段103、106が既知のシンボル部分より前方の信号に対して順方向等化処理を行い、前方逆方向等化処理手段104、107が前方の信号に対して逆方向等化処理を行い、後方逆方向等化処理手段105、107が後方の信号に対して逆方向等化処理を行い、前方取得手段109、110、112が前方の信号について順方向と逆方向の等化処理における誤差を比較して良好な方の等化処理の結果を取得し、後方取得手段108、111、112が後方の信号について順方向と逆方向の等化処理における誤差を比較して良好な方の等化処理の結果を取得する。

(もっと読む)

ストレージ装置、電子機器及び周波数帯域補償レベル調整方法

【課題】入力信号の所定の周波数帯域での減衰度合いに適合するように等化器の周波数帯域補償レベルを調整できるようにする。

【解決手段】実施形態によれば、ストレージ装置は、第1の等化器と、第2の等化器と、調整手段とを具備する。第1の等化器は、ホストによってストレージインタフェースを介して転送された第1の信号の所定の周波数帯域を補償した第2の信号を出力する。第2の等化器は、周波数帯域が補償された第2の信号を判定フィードバック補償により等化する。調整手段は第2の等化器による判定フィードバック補償の状態に応じて第1の等化器の周波数帯域補償のレベルを調整する。

(もっと読む)

等化装置、等化方法及びプログラム

【課題】低消費電力で符号間干渉を除去することができる等化装置を提供する。

【解決手段】等化装置は、2相のクロックに応じた等化部1a,1bを備える。等化部1a,1bは、入力信号をサンプルホールドするサンプルホールド部2a,2bと、サンプルホールド部2a,2bの出力と2ビット前からNビット前までに受信した信号の判定結果信号TAP2〜TAPNを積分して加算する電流積分型加算部3a,3bと、閾値を基に電流積分型加算部3a,3bの出力を判定する動的閾値制御判定ラッチ部4a,4bと、動的閾値制御判定ラッチ部4a,4bの出力信号を、逆相のクロックを用いる等化部へ判定結果信号TAP1として帰還するインバータ5a,5bと、判定結果信号TAP2〜TAPNを出力するラッチ部6a−1〜6a−(N−1),6b−1〜6b−(N−1)とを備える。

(もっと読む)

データ伝送のためのアナログ連続時間位相等化器によるシステム及び方法

【課題】データ伝送のためのアナログ連続時間位相等化器による方法等を提供する。

【解決手段】方法は、通信チャネルにわたる送信によって位相等化信号から歪ませられた位相歪み信号、又は送信データを含む送信データ信号を、入力信号として受信するステップと、連続時間領域における遅延演算子を入力信号に適用して入力信号の非微分形を生成するステップと、連続時間領域における微分演算子を入力信号に適用して入力信号の微分形を生成するステップと、入力信号の非微分形に正数である第1の係数を乗じて第1の積信号を生成するステップと、入力信号の微分形に負数である第2の係数を乗じて第2の積信号を生成するステップと、第1及び第2の積信号を加算し出力信号を生成するステップとを有する。

(もっと読む)

適応位相等化のためのシステム及び方法

【課題】ISIによる信号歪みを補償する適応位相等化のための方法等を提供する。

【解決手段】方法は、データ検出部によって位相等化信号に含まれる送信データに基づき位相等化信号から回復データ信号を生成するステップと、位相歪み検出部によって位相等化信号及び回復データ信号を互いに比較するステップと、比較に基づき位相歪み検出部によって位相歪みレベルを決定するステップと、位相歪み検出部によって位相歪みレベルに基づき位相歪みレベル信号を生成するステップと、積算部によって位相歪みレベル信号に基づき位相等化レベル信号を生成するステップと、位相等化部によって位相等化レベル信号に基づき送信データを含む送信データ信号を調整するステップとを有し、送信データ信号の調整により、位相等化信号、又は通信チャネルにわたる送信によって位相等化信号へと歪むよう構成された位相前置歪み信号が提供される。

(もっと読む)

送信回路、受信回路及びこれらを有する通信システム

【課題】従来の磁気結合を利用した通信システムで用いられる送信回路は、1つのインダクタだけでは、インダクタの自己共振周波数よりも高いデータレートで通信を行うことができない問題があった。

【解決手段】本発明にかかる送信回路は、インダクタを駆動して、絶縁された他の半導体チップにデータを送信する送信回路であって、前記インダクタの自己共振周波数よりも高いデータレートの送信データを受信して、当該送信データのデータレートで前記インダクタを駆動する送信信号を出力する駆動回路を有する。

(もっと読む)

判定帰還型自動等化器評価装置および判定帰還型自動等化器評価方法

【課題】従来の判定帰還型自動等化器(DFE)の評価装置では、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【解決手段】

既知のデジタル入力信号を受けてDFEから出力されるデジタル信号をDFEの各タップに対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

サンプリングされた前記デジタル信号から各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備える。

(もっと読む)

受信回路

【課題】補間誤差を低減することができる受信回路を提供することを課題とする。

【解決手段】受信回路は、入力データ信号をクロック信号に基づいてサンプリングしてサンプリング信号を出力するサンプリング回路(201)と、前記入力データ信号に対する前記サンプリング信号の位相情報に基づいて前記サンプリング信号を補間して補間データ信号を出力するデータ補間回路(202)と、前記サンプリング信号と前記位相情報とに基づいて補間誤差を出力する補間誤差判定回路(203)と、前記補間誤差に基づいて設定される等化係数によって前記補間データ信号を等化し、前記等化された補間データ信号を判定して判定信号を出力する判定等化回路(204)と、前記判定信号又は前記等化された補間データ信号に基づいて前記位相情報を生成し、前記データ補間回路及び前記補間誤差判定回路に前記位相情報を出力する位相検出回路(205)とを有する。

(もっと読む)

等化装置及び等化方法

【課題】等化性能の劣化を回避すると共に、演算量を削減する等化装置及び等化方法を提供する。

【解決手段】遅延量算出部102は、遅延プロファイルから受信信号の最大遅延量を算出し、伝搬路変動算出部103は、受信信号から伝搬路変動としてドップラー周波数を算出する。パラメータセット選択部104には、伝搬路変動の大きさと遅延波の遅延量とに基づいて、タップ数及び忘却係数の組み合わせが予め設定されており、パラメータセット選択部104は、算出された最大遅延量とドップラー周波数とに対応するタップ数及び忘却係数の組み合わせを選択する。等化処理部105は、選択されたタップ数及び忘却係数の組み合わせを用いて受信信号の等化処理を行う。

(もっと読む)

信号処理装置、信号処理方法、及び、プログラム

【課題】シングルキャリア信号と、マルチキャリア信号との両方を受信する受信装置を、小型に構成する。

【解決手段】等化部77では、シングルキャリア信号、及び、マルチキャリア信号の信号処理が、複数のフィルタとしての、例えば、フィルタの係数であるタップ係数が可変の2つの可変係数フィルタ203及び206を共有して行われる。本発明は、例えば、シングルキャリア信号と、マルチキャリア信号との両方を受信する受信装置に適用できる。

(もっと読む)

受信装置、受信方法、およびプログラム

【課題】エコーの遅延量が大きい場合や主波とエコーの判定を誤りやすい場合であっても、チャネル推定を精度よく行うことができるようにする。

【解決手段】PN相関計算部91においては、PN信号に含まれる系列と同じ系列のデータであるPN系列と、DTMB規格の各フレームの信号である入力信号ID(t)との相関値が求められる。相関値格納メモリ92には、1フレーム長の入力信号ID(t)とPN系列との相関値を記憶可能な容量が用意されており、PN相関計算部91により求められた相関値corr(t)が記憶される。1フレーム分の相関値corr(t)が記憶されたとき、相関値格納メモリ92に記憶されている1フレーム分の相関値corr(t)が読み出され、遅延プロファイル判定部93によりチャネルが推定される。本発明は、シングルキャリア伝送とマルチキャリア伝送に対応した受信装置に適用することができる。

(もっと読む)

受信回路

【課題】ビット幅の広いデジタル演算を必要とせずに、小さい回路面積及び消費電力で適応等化処理を実現できる受信回路を提供する。

【解決手段】受信回路は、等化係数に応じた等化処理を受信信号に施して等化された信号を出力する等化回路と、等化された信号と第1閾値との大小関係に応じた0及び1の信号値を有する第1の信号を求め、等化された信号と第2閾値との大小関係に応じた0及び1の信号値を有する第2の信号を求め、第1の信号中に現れる所定の0及び1のパターンの出現回数と第2の信号中に現れる所定の0及び1のパターンの出現回数との差分を計算する誤差計算回路と、差分に応じて等化係数を調整する適応等化制御回路とを含む。

(もっと読む)

受信装置、受信方法、およびプログラム

【課題】シングルキャリアを使ったデータ伝送とマルチキャリアを使ったデータ伝送の双方のデータ伝送に対応した受信装置の回路規模を抑えることができるようにする。

【解決手段】演算部74においては、シングルキャリア伝送によって伝送されたデータの受信時、入力信号と等化部71からの等化後信号に基づいて、等化に用いられる情報を求めるための演算が時間域の信号を用いて行われる。また、マルチキャリア伝送によって伝送されたデータの受信時、入力信号と除算部73からの等化後信号に基づいて、等化に用いられる情報を求めるための演算が周波数域の信号を用いて行われる。等化部71と除算部73においては、それぞれ、演算部74により求められた情報を用いて等化が行われる。本発明は、シングルキャリア伝送とマルチキャリア伝送に対応した受信装置に適用することができる。

(もっと読む)

データ判定回路および受信装置

【課題】パイプライン型ADCを用いたデータ判定回路および受信装置における消費電力の低減を図る。

【解決手段】パイプライン型A/D変換回路601,602を有するデータ判定回路20であって、前記パイプライン型A/D変換回路は、該パイプライン型A/D変換回路における少なくとも上位2ビットのパイプラインステージ602(1st stage, 2nd stage)から出力される判定結果に応じて、それよりも下位ビットのパイプラインステージ602(3rd stage, …, Nth stage)の動作を停止する。

(もっと読む)

判定帰還型波形等化器

【課題】直前ビットの受信判定データを利用することなく、第1ポストカーソルのISIを補正する判定負帰還型波形等化器を提供する。

【解決手段】判定帰還型波形等化器は、受信データを入力する増幅回路と、フリップフロップを含み、増幅回路の出力がフリップフロップに入力され、フリップフロップにより増幅回路の出力を判定するデュオバイナリ信号判定器と、フリップフロップに保持された判定結果を逐次シフトさせるシフトレジスタと、シフトレジスタの各出力を入力とし、出力を増幅回路の出力に帰還し、その電位を制御する複数の電流制御ブロックとを有し、フリップフロップに保持された判定結果をシフトレジスタでシフトさせることなく増幅回路の出力の出力に帰還しない。

(もっと読む)

1 - 20 / 122

[ Back to top ]