Fターム[5L106CC31]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538) | 不良部の不使用 (227)

Fターム[5L106CC31]の下位に属するFターム

アドレス変換を用いるもの (172)

Fターム[5L106CC31]に分類される特許

1 - 20 / 55

メモリコントローラ

半導体装置

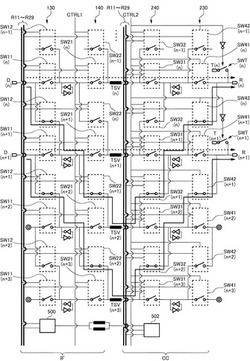

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

半導体装置

【課題】不良選択線のアドレスを記憶するための回路に必要とされる占有面積を削減する。

【解決手段】一例として、それぞれが複数のメモリセルに接続された複数の第1及び第2の選択線と、複数の第1の選択線のうち欠陥である第1の選択線が置換可能であり、複数の第2の選択線のうち欠陥である第2の選択線が置換不可能な第1の冗長選択線と、欠陥である第1及び第2の選択線のいずれをも置換可能な第2の冗長選択線とを備える。これにより、欠陥である第1の選択線は第1及び第2の冗長選択線のいずれかに置換され、欠陥である第2の選択線は第1の冗長選択線に置換されることなく第2の冗長選択線に置換される。その結果、第1の冗長選択線を選択するアドレスビットの数は、第2の冗長選択線を選択するアドレスビットの数よりも少なくなり、対応する不良アドレスを記憶するROMの数も少なくなる。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】 本発明は単一の半導体装置を構成する複数個のチップでヒューズ情報を伝送できる半導体装置に関することである。

【解決手段】半導体装置は信号伝送部及び信号受信部を含む。信号伝送部は第1チップに配置されて、伝送制御信号に同期してヒューズ情報を伝送する。信号受信部は第1チップ及び第2チップに各々配置されて、受信制御信号に同期して前記ヒューズ情報を受信する。

(もっと読む)

不揮発性半導体記憶装置及びそのベリファイ方法

【課題】フューズを用いずにベリファイ読み出しの判定をワイアードオア構成により行うことを可能とし、フューズを設けない分、チップサイズを従来に比較して低減した不揮発性半導体記憶装置を提供する。

【解決手段】本発明の不揮発性半導体記憶装置は、複数のビット線及び複数のワード線各々が交差し、交差した部分に不揮発性のメモリセルが配置されたメモリセルアレイと、メモリセルアレイの欠陥ビット線と置換する冗長ビット線を備える不良置換回路と、ビット線毎に設けられ、ワード線で選択されたメモリセルに書き込むまたは読み出したデータを記憶するラッチを含むページバッファと、ベリファイ処理でビット線から読み出し、ページバッファのラッチに書き込まれたデータを、複数のビット線単位で一括判定する一括判定回路と、欠陥ビット線に対応するページバッファにおけるラッチに疑似データを書き込む疑似データ書込回路とを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メインメモリで発生した不良を救済するために面積効率の悪化しない不揮発性半導体記憶装置の提供。

【解決手段】不揮発性半導体記憶装置は、不良ビット検出回路を有し、メインメモリの不良ビットを検出する。検出したメインメモリの不良モードと不良アドレスとの情報に応じて、書き込み及び読み出しを行う際のスタートアドレスを任意に設定可能なアドレス選択回路を有する。これにより予備のメモリ領域(冗長メモリ)を設けることなく、メインメモリで発生した不良を救済することが可能である。

(もっと読む)

半導体装置及び欠陥メモリ置換方法

【課題】置換に用いる生死情報が記憶する記憶部を有する半導体装置を提供する。

【解決手段】本発明は、通常メモリセルにおける欠陥メモリセルを置換するために設けられた冗長メモリセルを、置換単位の冗長ブロック毎に試験し、冗長ブロック全体の冗長メモリセルが良品であるか否かをテストするテスト回路を有している。また、テスト回路にの試験結果で、冗長ブロック全体の冗長メモリセルが良品の場合、冗長ブロックを良品であることを示し、冗長ブロックのいずれかの冗長メモリセルが不良の場合、冗長ブロックが欠陥メモリセルの置換に使用できない不良であることを示す生死情報を記憶するROM領域を有している。パッケージング後の試験で検出された欠陥メモリセルを、冗長メモリセルと置換する際、ROM領域からいずれの冗長ブロックが置換に使用できるかを確認するため、ROM領域から生死情報を読み出すための読出回路を有している。

(もっと読む)

電気光学装置

【課題】電気光学装置の走査線駆動回路において、救済用の単位シフトレジスタの駆動能力の向上および動作の高速化を図る。

【解決手段】救済用単位シフトレジスタSRBkは、液晶アレイ部10を挟んで正規の単位シフトレジスタSRの反対側に配設される。救済用単位シフトレジスタSRBkは、2行前のゲート線駆動信号Gk-2を受け、その活性化の2水平期間後に活性化するクロック信号に同期して、自己が出力するゲート線駆動信号Gkを活性化させる。

(もっと読む)

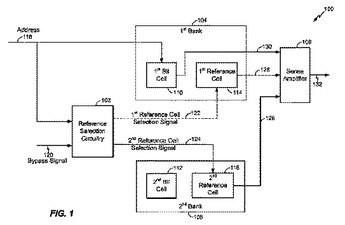

参照セルを選択するためのシステムおよび方法

参照セルを選択するためのシステムおよび方法が開示される。ある特定の実施形態では、メモリの第1のバンクの中のビットセルに対応するアドレスを受け取るステップを含む、方法が開示される。方法はまた、第1のバンクの第1の参照セルがバイパスされるものとして示されることに応答して、メモリの第2のバンクの第2の参照セルにアクセスするステップも含む。  (もっと読む)

(もっと読む)

半導体装置及びその制御方法

【課題】不良チップが存在する場合であっても、メモリ容量を2のべき乗とする。

【解決手段】コアチップCC0〜CC7と、コアチップCC0〜CC7にそれぞれ対応する不良チップ信号SK0〜SK7を供給するインターフェースチップIFを備える。インターフェースチップIFは、コアチップCC0〜CC7のうち良品チップの数を検知する枚数検知回路40を有し、枚数検知回路40によって検知された良品チップの数をX個とし、2n≦X<2n+1(nは自然数)とした場合、X−2n個の良品チップを不使用チップとする。本発明によれば、良品チップであっても不使用チップとすることが可能であることから、不良チップが発見された場合においてもメモリ容量を2のべき乗とすることができる。これにより、いわゆるパーシャル品においてコントローラの制御が複雑化することが無くなる。

(もっと読む)

不揮発性半導体記憶装置

【課題】ECC動作を消去モードの最初に行うことで、高速読み出し動作可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置10は、データ格納用の不揮発性メモリセルが配列されたメモリ領域(メイン消去ブロック110−2〜110−n)と、メモリ領域が不良領域である場合にメモリ領域と置換される冗長領域(冗長用消去ブロック110−1)と、消去動作を示すコマンドが入力されると、消去動作に先立って前記メモリ領域からデータを読み出し、誤り検出を行い、誤り検出結果に基づいて前記冗長領域へと置換する前記不良領域を検出する制御部(制御部12)と、を備える。

(もっと読む)

メモリデバイスのフェイル救済方法およびリダンダンシ演算装置

【課題】フェイル救済にかかる時間を短縮することが可能なメモリデバイスのフェイル救済方法およびリダンダンシ演算装置を実現する。

【解決手段】DUTの記憶領域のフェイル箇所を示すフェイルデータに基づき、記憶領域のフェイル箇所に代替記憶領域となるスペアラインを割り当てるリダンダンシ演算を行い、DUTのフェイル救済をするメモリデバイスのフェイル救済方法において、最小限のスペアラインで可能な限り多くの未救済ビットフェイルを救済する組み合わせを求める組み合わせ演算処理を行い、ラインフェイルを救済した後に未救済ビットフェイル数と未使用スペアライン数とを比較し、未使用スペアライン数が未救済ビットフェイル数以上ある場合、最小限のスペアラインで可能な限り多くの未救済ビットフェイルを救済する組み合わせを求める組み合わせ演算処理をせずに未救済ビットフェイルに未使用スペアラインを割り当ててビットフェイルを救済する。

(もっと読む)

ビット誤り閾値、及びリマップしたメモリ装置にアドレス指定する内容アドレス指定可能メモリ

【課題】メモリ装置の寿命を、比較的少数のメモリセルにおける寿命よりも、大多数のメモリセルにおける寿命まで延ばし信頼性の向上を図る。

【解決手段】メモリ装置から読み出したデータを表す読み出し信号を受信し、前記読み出し信号に関連づけられたビット誤り率および/またはビット誤り数を決定する、誤り訂正コーディング(ECC)デコーダと、および前記ビット誤り率および/または前記ビット誤り数がエラー閾値と一致または超過するか否かに、少なくとも部分的に基づいて、前記メモリ装置のリマップしたリマップアドレスを内容アドレス指定可能メモリ装置(CAM)に供給する、リマップコントローラと、を備えた、システムを提供する。

(もっと読む)

解析装置および解析方法

【課題】試験パターン情報のデータ量の削減を図ること。

【解決手段】関数ライブラリ格納メモリ212は、メモリ試験の各アルゴリズムに対応する各計算式を記憶する。FAIL情報解析部230は、メモリ試験の試験結果を取得する。アルゴリズム特定部237は、FAIL情報解析部230によって取得された試験結果に基づいてメモリ試験のアルゴリズムを特定する。計算式選択部238は、関数ライブラリ格納メモリ212によって記憶された各計算式のうちの、アルゴリズム特定部237によって特定されたアルゴリズムに対応する計算式を選択する。計算処理部240は、試験結果と、計算式選択部238によって選択された計算式と、に基づいてフェイルビットマップを作成する。計算処理部240は、作成したフェイルビットマップを出力する。

(もっと読む)

フェイル情報取得装置

【課題】被検査デバイスの欠陥救済のための演算、フェイル解析に要する時間を短縮することができるフェイル情報取得装置を提供する。

【解決手段】フェイルメモリ(14)から欠陥情報を順次読み出してフェイルカウントメモリ(13)内のライン毎のフェイルカウント数を更新し取得するフェイル情報取得装置において、複数の計数手段(CNT)と該複数の計数手段のうち任意の2以上の計数手段の出力値を加算可能な加算手段(16)とを設け、フェイルメモリから欠陥情報が読み出された場合にフェイルカウントメモリからフェイルカウント数を読み出して更新し、更新した値をフェイルカウントメモリの元の位置に書き戻すのと並行して、救済ラインを共有する他のラインのフェイルカウント数を前記加算手段によって加算し、該加算結果をフェイルカウントメモリの他の領域に格納するように構成した。

(もっと読む)

半導体記憶装置

【課題】メモリセルにショート不良が生じた場合においても、不良のメモリセルにおけるリーク電流を低減して、誤書き込み/誤読み出し等を防止する。

【解決手段】ショート不良検出回路30は、ダイオードDiが短絡不良したメモリセルMCを検出するため、メモリセルMCに逆バイアスを印加し、ワード線WLに電流が流れるか否かを電流検出器33により検出する。また、ビット線BLに関しては、電圧が所定値より上昇するか否かを差動増幅器31により検知する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルトランジスタの劣化を判定する。

【解決手段】メモリシステム1は、複数のメモリセルトランジスタを含む不揮発性メモリ10と、メモリセルトランジスタの電流経路の一端に電気的に接続されたビット線BLと、メモリセルトランジスタの電流経路の他端に電気的に接続されたソース線SLと、メモリセルトランジスタのゲート電極に電気的に接続されたワード線WLと、ビット線BLに電気的に接続され、かつメモリセルトランジスタからデータを読み出すセンスアンプ回路13と、ワード線WLに電気的に接続され、かつメモリセルトランジスタがオンする読み出し電圧をワード線WLに印加するロウデコーダ11と、オン状態のメモリセルトランジスタに流れるセル電流を測定して当該メモリセルトランジスタの劣化を判定するステートマシン18とを含む。

(もっと読む)

半導体装置

【課題】 高信頼動作の大容量相変化メモリ・モジュールを実現する。

【解決手段】 本発明による半導体装置は、カルコゲナイド材料を用いた記憶層とダイオードで構成されたメモリセルを積層した構造のメモリアレイを有し、選択されたメモリセルが位置する層に応じて、初期化条件及び書き換え条件が変更されるものである。カレントミラー回路を動作に応じて選択するとともに、電圧選択回路とカレントミラー回路におけるリセット電流の制御機構により、初期化条件及び書き換え条件(ここでは、リセット条件)を動作に応じて変更する。

(もっと読む)

半導体記憶装置

【課題】置換を行うワード線のアドレスをメモリブロック毎に切換える方式と固定する方式とを切換え可能な半導体記憶装置を提供する。

【解決手段】ヒューズ部22に高速動作ヒューズHSFUSEを設け、高速動作ヒューズHSFUSEが切断されたときに、シフト冗長回路6が置換を行うアドレスが、アドレス信号によらずヒューズ素子FUSE0に固定されるように構成する。また高速動作ヒューズHSFUSEが切断されたときに、センスアンプの活性化信号であるセンスアンプイネーブル信号の遅延時間が少なくなるように構成する。

(もっと読む)

1 - 20 / 55

[ Back to top ]