Fターム[5L106CC32]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538) | 不良部の不使用 (227) | アドレス変換を用いるもの (172)

Fターム[5L106CC32]に分類される特許

1 - 20 / 172

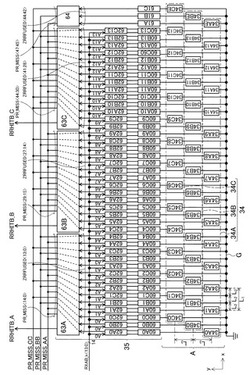

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】ロールコールテストに要する工数を削減できる半導体記憶装置及びそのテスト方法を提供する。

【解決手段】不良アドレスが格納される不揮発性の記憶素子を備えた半導体記憶装置にロールコールテスト時にマスク用テストモード信号を出力するテスト制御回路とロールコール回路とを備える。ロールコール回路は、アドレス信号と不良アドレスとをビット単位で比較し、その比較結果を出力する。また、ロールコール回路は、マスク用テストモード信号が入力されると、アドレス信号の所望のビットに対応する比較結果をマスクして上記アドレス信号と不良アドレスとが一致していることを示す値を出力すると共に、マスクされていないビットに対するロールコールテストを可能にする。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体集積回路

【課題】プロセッサとメモリを備えた半導体集積回路の前記メモリをテストする際に、テスト回路による回路規模の増大を最小限にすることができる半導体集積回路を提供する。

【解決手段】SIMDプロセッサ2が、MBIST・リペアコントロール回路6によりテストされたRAM4の不良の有無と、不良アドレス(不良セル)の位置情報を解析し、メモリコントローラ回路3内部に保持して、通常動作時には、不良メモリの不良アドレスへのアクセス時にはメモリコントローラ回路3がリペア用RAM5へのアクセスするように制御する。

(もっと読む)

半導体装置

【課題】不良チップの救済効率を向上させ歩留まりを向上させる。

【解決手段】第1半導体チップのメモリセルアレイは、ノーマルセルアレイとスペアセルアレイとを備える。第1不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第1不良アドレスデータを出力する。第1比較回路は、アドレスデータと第1不良アドレスデータとを比較して第1の一致信号を出力する。第2不良アドレスデータ出力回路は、メモリセルアレイ中の不良メモリセルのアドレスを示す第2の不良アドレスデータを出力する。第2比較回路は、アドレスデータと第2の不良アドレスとを比較して第2の一致信号を出力する。

(もっと読む)

メモリ装置

【課題】少ない情報で不良メモリセルを冗長メモリセルに切り替えることができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、複数のメモリセルと、冗長メモリセルと、複数のメモリセルの中の不良メモリセルを冗長メモリセルに切り替えるセレクタとを含む複数のメモリセルブロック(501〜503)と、複数のメモリセルブロックの各々が不良メモリセルを有するか否かの不良情報、及び不良メモリセルを有するメモリセルブロック内の不良メモリセルを特定するための特定情報に基づき、複数のメモリセルブロックのセレクタの制御信号を出力する制御回路(522)とを有し、制御回路は、複数のメモリセルブロックのセレクタの制御信号の各ビット線に対応して設けられ、特定情報をシリアルにシフトするための複数のフリップフロップ(FF0〜FF8)を有する。

(もっと読む)

半導体装置

【課題】アドレス比較回路に入力される判定信号の期間であって、アドレス比較回路が誤判定を起さない期間、を評価工程において求めることができる半導体装置を提供する。

【解決手段】供給されるヒューズ判定信号(ヒューズ判定信号RRFDETA)が活性レベルの場合に、入力されるアドレスがヒューズに記憶したアドレスと一致するか否かを判定するアドレス比較回路(FUSE判定回路20)と、外部から半導体装置に供給される外部クロックのレベルの遷移に応じて、前記ヒューズ判定信号の活性レベル及び非活性レベルを制御するヒューズ制御回路(FUSE制御回路18a)と、を備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】不良メモリセルからのデータ読み出しを無効にし、救済メモリセルからのデータ読み出しを有効にする読み出し制御技術を改良した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリバンクと、自己に対応するメモリバンク内のメモリセルからデータを読み出す複数のリードアンプと、複数のメモリバンク内の不良メモリセルの代わりの救済メモリセルと、データの入出力を行う入出力部と、不良メモリセルのアドレスを受け付けた場合にヒット信号を出力する判定部と、ヒット信号に応答して、不良メモリセルを有するメモリバンクに対応する特定リードアンプと入出力部とを非接続状態にし、特定リードアンプとは異なる所定リードアンプと入出力部とを接続状態にする接続制御部とを含み、所定リードアンプは、データ読出し時にヒット信号に応答して救済メモリセルからデータを読み出し入出力部に出力する。

(もっと読む)

半導体記憶装置

【課題】内蔵メモリの不良救済のための冗長部としてロウアドレスにより指定されるメモリセル列と置き換えられるロウ冗長部と、内蔵メモリの診断を行う自己診断回路を有する半導体記憶装置において、連続したサイクルで発生するロウ置換判定処理の演算速度マージンを改善する。

【解決手段】置換判定単位の区切りを示すアドレス検知信号をロウアドレスの下位ビットに基づいて生成するアドレス切替検知回路と、アドレス検知信号が非アクティブの時にアクティブになるまで全体比較結果信号(自己診断回路による比較結果出力)を保持する不良情報保持回路とを備え、置換ロウアドレスの重複判定処理を置換判定単位内でアドレス検知信号がアクティブの期間でのみ行うようにする。それにより、連続したサイクルで発生する置換ロウアドレスの重複判定処理を置換判定単位の間隔に分散させることが可能になり、ロウ置換判定処理の演算速度マージンが改善される。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】電圧検出部12は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)へ供給される書き込み電圧を検出し、書き込み電圧が所定の閾値電圧以上となると、書き込み制御部11に、書き込み信号に係わらず電気ヒューズ素子2への書き込みを停止させることで、書き込み電圧に異常が発生し、過電圧になることによる誤書き込みを抑制できる。

(もっと読む)

不揮発性記憶装置、集積回路装置、及び電子機器

【課題】繰り返し書き換えを行ってもメモリーセルの過剰消去をなくし、読み出し動作の誤動作の回避及び書き換え回数の向上を実現する不揮発性記憶装置等を提供する。

【解決手段】不揮発性半導体記憶装置100は、複数の不揮発性メモリーを有する正規メモリーセルアレイ120と、それぞれが正規メモリーセルアレイ120内の不良メモリーセルを救済するための複数の不揮発性メモリーセルを有する冗長メモリーセルアレイ132〜138と、冗長メモリーセルアレイ132〜138のうち少なくとも1つの冗長メモリーセルアレイを選択する冗長メモリーセルアレイ選択回路140とを含む。冗長メモリーセルアレイ選択回路140は、消去動作時において、入力アドレス情報と不良メモリー情報とに基づいて消去単位で決定される複数の冗長メモリーセルアレイの中から、消去単位を分割したブロック単位の優先順位に従って冗長メモリーセルアレイを選択する。

(もっと読む)

半導体装置及びその製造方法

【課題】高速アクセス時に初めて不良となるアドレスを救済する。

【解決手段】メモリセルアレイ101に含まれる不良メモリセルを置換するための冗長回路102,103と、不良メモリセルのアドレスを記憶する電気ヒューズ回路142と、メモリセルアレイ101から読み出されるテストデータの正誤判定を行うことによって判定信号を生成するデータ判定回路107aと、第1の動作モードにおいては判定信号P/Fが活性化している場合に与えられたアドレス信号を電気ヒューズ回路142に供給し、第2の動作モードにおいては判定信号P/Fに関わらず外部から供給されるデータマスク信号DMが活性化している場合に与えられたアドレス信号を電気ヒューズ回路142に供給する解析回路143と、を備える。本発明によれば、高速アクセス時に初めて不良となるアドレスについても正しく救済することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】不良メモリセルのアドレスを解析するのに必要なメモリの記憶容量を削減する。

【解決手段】メモリセルアレイ101に含まれる不良サブワード線及び不良ビット線をそれぞれ置換するためのロウ冗長回路102及びカラム冗長回路103と、不良サブワード線及び不良ビット線のアドレスをそれぞれ記憶する電気ヒューズ回路142a,142bと、第1の動作モードにおいては、判定信号P/Fが活性化している場合に与えられたアドレス信号に基づいて電気ヒューズ回路142a,142bの一方を選択し、第2の動作モードにおいては、判定信号P/Fが活性化している場合に与えられたアドレス信号に基づいて電気ヒューズ回路142a,142bの他方を選択するヒューズ選択回路146を備える。本発明によれば、冗長ワード線を用いた置換と冗長ビット線を用いた置換をフレキシブルに切り替えることができる。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

不揮発性半導体記憶装置の領域設定方法および不揮発性半導体記憶装置

【課題】カンパニー領域専用のブロックが不要な不揮発性半導体記憶装置の領域設定方法を提供する。

【解決手段】不揮発性半導体記憶装置1のメモリセルアレイ2のブロックに不良ブロックが含まれていた場合に、ブロックにユーザー領域とカンパニー領域とを設定する方法において、メモリセルアレイは複数のバンクに分かれていて、各バンクはユーザー領域として使用する複数の通常ブロックと、1つ以上の冗長ブロックとを有していて、カンパニー領域を所定バンクの冗長ブロックに初期設定するステップと、通常ブロックのうちのいずれかが不良ブロックであった場合に、当該不良ブロックの代わりに使用する代替ブロックを、当該不良ブロックが属するバンクの冗長ブロックに設定するステップと、代替ブロックがカンパニー領域と重なった場合に、カンパニー領域を、空いている冗長ブロックに移動させるステップとを有している。

(もっと読む)

半導体メモリ、および製造方法

【課題】冗長セルに置き換え可能な不良セルを増加でき、歩留まりを向上させること。

【解決手段】メモリセルアレイ102はワードごとにxビット分のデータセルとyビット分の冗長セルとを有している。位置情報記憶部103はワードごとに不良セルの位置情報を記憶する。指定ワードの読み出し処理の場合、不良ビット代替回路104は、位置情報記憶部103内の指定ワードの不良セルの位置情報であるFAIL DATAに基づいて、メモリセルアレイ102内の指定ワードのx+yビット分のRAW READ DATAから不良セルのデータを除いたxビット分のREAD DATAを出力する。指定ワードへの書き込み処理であれば、不良ビット代替処理回路104は、FAIL DATAを用いて、xビット分のWRITE DATAをデータセルと冗長セルに書き込むx+yビットのRAW WRITE DATAに変換し、メモリセルアレイ102に書き込む。

(もっと読む)

半導体メモリ装置での冗長プログラム回路

【課題】半導体メモリ装置の冗長プログラム回路を提供する。

【解決手段】マスタヒューズを有し、該マスタヒューズのカッティングの有無を示す状態信号として動作イネーブル信号を生成するマスタヒューズ部と、マスタヒューズ部の動作イネーブル信号に応じて制御され、アドレス信号のビット数だけに対応する制御ヒューズを有し、欠陥セル情報に従い制御ヒューズのカッティングの有無をそれぞれ示す状態信号として第1−第M制御信号ペア(Mは前記アドレス信号ビットの数)を生成する制御ヒューズ部と、アドレス信号がデコーディングされたアドレスの信号ビットを第1−第M制御信号ペアの組合せ論理入力により対応的にデコーディングして、デコーディングアドレスの信号ビットのうち欠陥セル情報を有する論理状態がデコーディング出力端にそのまま伝達されるようにするデコーディング部と、を備える半導体メモリ装置での冗長プログラム回路を備える。

(もっと読む)

リペア分析装置およびその方法

【課題】メモリ内で発見された不良セルに対する情報を利用してリペア解を算出するリペア分析装置および方法を提供する。

【解決手段】リペア分析装置は選択部610および分析部620を備え、選択部610は、制御コードに応答して、複数のスペアピボット不良セルのローアドレスのうち一部を選択し、カラムアドレスのうち一部を選択し、分析部620は、複数のノンスペアピボット不良セルのローアドレスが選択部610によって選択されたローアドレスに含まれているか否か、および複数のノンスペアピボット不良セルのカラムアドレスが選択部610によって選択されたカラムアドレスに含まれているか否かを表す分析信号を生成する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、メインワード線の断線故障が起きた場合に、断線箇所から先がフローティング状態になることにより、正常なワード線の信号に影響を及ぼすことを防止する。

【解決手段】メインワード線の遠端にラッチ回路を設け、断線箇所から先に電位が、ハイ電位に固定されるようにし、正常なワード線に影響しないようにする。

(もっと読む)

半導体集積回路装置、制御記憶装置の制御方法及びプログラム

【課題】ブロック単位で構築された冗長構成の利点を最大限利用すると共に、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても対処可能にする。

【解決手段】エラー検出部22は、読み出し制御部21が通常の運用時における制御装置3の動作を規定する通常運用データを冗長メモリ11,12から読み出す前に、通常運用データを格納するブロックに対してチェック処理を行う。当該チェック処理によるエラー情報はエラー情報保持部13に保持させる。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、エラーが検出されたブロックに冗長構成的に対応する健全なブロックが存在するか否かを判定し、健全なブロックが存在する場合には、通常運用データの読み出しを行う。

(もっと読む)

1 - 20 / 172

[ Back to top ]