Fターム[5L106DD26]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465) | 試験装置 (1,037) | 試験結果の表示 (163)

Fターム[5L106DD26]に分類される特許

1 - 20 / 163

半導体記憶装置

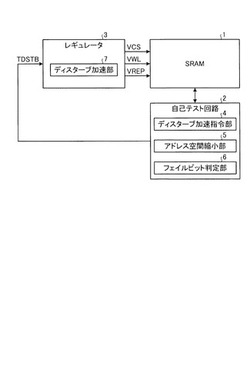

【課題】メモリセルの各トランジスタの特性のランダムばらつきについてのテストを効率化する。

【解決手段】メモリセルMCの動作をテストする自己テスト回路2と、自己テスト回路2からの加速指令に基づいて、メモリセルMCのディスターブが加速するようにワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSを設定するレギュレータ3とを備える。

(もっと読む)

半導体装置

【課題】半導体装置の動作テストのスループットを向上させる。

【解決手段】判定回路112は、2つのメモリバンクBANK(A)、BANK(E)から読み出される計16ビットのテストデータを検査する。検査対象となる16ビットのメモリセルMCにはすべて「H」の書き込みが実行されており、いずれのメモリセルMCに異常がなければそのまま「H」が読み出される。判定回路112は、メモリバンクBANK(A)のテストデータ同士を比較する第1検出回路124とメモリバンクBANK(E)のテストデータ同士を比較する第2検出回路126に加えて、更に、メモリバンクBANK(A)のテストデータとメモリバンクBANK(E)のテストデータを比較する第3検出回路128を備える。

(もっと読む)

メモリを試験するためのシステムおよび方法

【課題】メモリを試験するためのシステムおよび方法を提供すること。

【解決手段】複数のメモリを試験するためのシステムは、複数のメモリ試験デバイスおよびコントローラを含む。メモリ試験デバイスの各々は、メモリの1つに結合される。コントローラは、試験ベクトルを生成し、その試験ベクトルをメモリ試験デバイスに送るように構成される。メモリ試験デバイスの各々は、その結合されたメモリを試験ベクトルに従ってそれぞれ試験し、試験結果をコントローラに送る。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

半導体メモリ装置及びそのテスト方法

【目的】少ない外部端子によって、半導体メモリ装置に構築されているメモリが故障しているか否かの製品出荷時のテスト及びその故障要因を特定することが可能な半導体メモリ装置及びそのテスト方法を提供することを目的とする。

【構成】半導体メモリ装置に構築されているメモリが読出指令に応答したか否かを判定し、メモリが読出指令に対して非応答であった場合にはメモリから読み出されたメモリデータに代えてエラーコードを外部出力する。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

半導体集積回路

【課題】回路規模の増加を抑制しつつ、テスト時間の短縮を図る半導体集積回路を提供する。

【解決手段】BIST回路1は、アドレス信号を生成するアドレス生成回路1bと、書き込みデータ及び書き込みデータに対応する期待値データを生成するデータ生成回路1aと、メモリを制御するチップイネーブル信号生成回路1cと、メモリの書き込み動作及び読み出し動作を制御する制御信号を生成する制御信号生成回路1dとを有する。メモリブロック化回路2は、複数のメモリを有し、アドレス信号から複数のメモリのうちテスト対象となるメモリのアドレスに対応するアドレス入力信号を生成し、且つ、複数のメモリからテスト対象のメモリを選択するメモリ選択信号を生成するアドレス変換回路Aを有し、メモリ選択信号に基づいて、複数のメモリのうちテスト対象のメモリが出力するデータを選択して出力するメモリ出力選択回路DSと、を有する。

(もっと読む)

半導体装置

【課題】テスト時間を短縮させる。

【解決手段】フラッシュメモリLSI1は、データを記憶する記憶部であって、予め定められたビット数のデータ領域を複数有するフラッシュメモリ部8と、フラッシュメモリ部8から読み出したデータとデータの期待値とが不一致であるビットを示す不良ビットの数が、予め定められた閾値以下であるか否かを、データ領域ごとに判定する判定回路部10と、判定回路部10が判定した判定結果に応じた出力を出力端子(RB#端子)に出力させるRB制御回路部60と、を備える。

(もっと読む)

ROMテスト時間の短縮方法

【課題】 従来の技術においては、ROM3個分のテスト時間を2個分のテスト時間までしか短縮できないという問題、或いは、加算或いは減算をおこなうため、データビット数の変動の虞があると共に、信頼性が低下する虞があった。

【解決手段】 複数個のROMに書き込まれたデータをテストする場合のROMテスト時間の短縮方法に於いて、複数個のROMの二つずつのROMの出力データのビット毎の比較を行う比較手段を備え、該比較手段の出力を複数個のROMに対応してそれぞれ記憶させ、該複数の記憶手段の出力データに対して、演算の順序が異なる少なくとも二つの異なる内容の演算を行い、該演算結果を期待値と比較することでROMデータを検査する。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑制でき、評価精度を落とすことなく、パラレルテストの時間の増大を抑制できる半導体装置を提供する。

【解決手段】複数のメモリアレイと、読み出し動作においては、メモリセルからの読み出しデータを増幅して外部へ出力するリードデータを生成し、書き込み動作においては、外部から供給されるライトデータに基づいてメモリセルへの書き込みデータを生成する、複数のメモリアレイに共通に設けられたリードライトアンプ(RWAMP)と、複数のメモリアレイ毎に設けられたスイッチと、複数のメモリアレイのうち活性化するメモリアレイのスイッチを順次導通させる第1の制御信号(LMIOSW)を生成する第1の制御回路(12b)と、リードライトアンプを活性化する第2の制御信号(DAE)を、活性化するメモリアレイの個数に基づいて発生する第2の制御回路(14)と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】アクセス性能の向上を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、データバッファに格納されエラー訂正されたリードデータを第1の入出力ピンから出力するのに同期して、エラー訂正されたリードデータに対応する第1のパリティフラグを第2の入出力ピンから出力する。

(もっと読む)

半導体記憶装置

【課題】製造ばらつきにより生じる不良ブロックを判定可能な半導体記憶装置を提供する。

【解決手段】メモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページのうち、第1カラムに対応する第1メモリセルにデータを書き込むとき、プログラム動作を繰り返した第1回数を保持する第1記憶部63と、前記ページのうち、前記第1カラムとは異なる第2カラムに対応する第2メモリセルにデータを書き込むとき、プログラム動作を繰り返した第2回数を保持する第2記憶部64と、第1回数と第2回数の差が規定値を超えたとき、前記第1メモリセルと前記第2メモリセルとを含むブロックを不良ブロックとして登録する制御部6とを備える。

(もっと読む)

半導体装置

【課題】アドレス比較回路に入力される判定信号の期間であって、アドレス比較回路が誤判定を起さない期間、を評価工程において求めることができる半導体装置を提供する。

【解決手段】供給されるヒューズ判定信号(ヒューズ判定信号RRFDETA)が活性レベルの場合に、入力されるアドレスがヒューズに記憶したアドレスと一致するか否かを判定するアドレス比較回路(FUSE判定回路20)と、外部から半導体装置に供給される外部クロックのレベルの遷移に応じて、前記ヒューズ判定信号の活性レベル及び非活性レベルを制御するヒューズ制御回路(FUSE制御回路18a)と、を備えることを特徴とする。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

試験装置および試験方法

【課題】精度良く被試験デバイスを試験する。

【解決手段】データ信号とクロック信号とを授受する被試験デバイスを試験する試験装置であって、被試験デバイスにデータ信号およびクロック信号を試験信号として供給する試験信号供給部と、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、調整時において、データ信号を取得するタイミングを生成するためのクロック信号の遅延量を調整する調整部とを備える試験装置を提供する。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を低コストで実現可能な半導体装置を提供する。

【解決手段】例えば、相補メモリを備えた半導体装置において、書き込み時に、(N+1)ビットの正極(Posi)データに対してパリティービットを生成し、(N+1)ビットの負極(Nega)データに対してパリティービットを生成する。読み出し時には、正極側および負極側のそれぞれに対してパリティーチェックを行うと共に、正極データと負極データを各ビット番号毎に比較する。ここで、正極データと負極データが同一データとなっているビット番号が存在した場合、正極側のパリティーチェック結果が異常であれば正極データの当該ビット番号を誤データとして特定でき、逆に負極側のパリティーチェック結果が異常であれば負極データの当該ビット番号を誤データとして特定できる。

(もっと読む)

記憶装置、記憶装置の試験プログラム、及び記憶装置の試験方法

【課題】仕様で求められる記憶容量の信頼性を確保しつつ、記憶容量に応じてコストを調節する。

【解決手段】記憶装置は、メモリセルと、前記メモリセルにデータの書込みまたは読出しを行うデータ入出力回路とをそれぞれ有する複数のメモリブロックと、前記メモリブロックごとに、前記データ入出力回路に前記メモリセルへの試験用データの書込みまたは読出しを行わせて、当該メモリブロックが使用可能かまたは使用不能かを試験する試験部と、設定される記憶容量に対応する個数の使用可能な前記メモリブロックへの電源をオンにし、それ以外の前記メモリブロックへ電源をオフにする第1の制御部とを有するので、仕様で求められる記憶容量の信頼性を確保しつつ、記憶容量に応じて記憶装置のコストを調節できる。

(もっと読む)

半導体装置

【課題】従来は、外部機器側で情報の書き込みが正常に成されたか否かを判断していた。また、半導体装置ないに大掛かりな回路を構成しなければ、正しく書き込みを判断できなかった。

【解決手段】外部機器から入力される書込パルスのうち、そのパルス長で、搭載する不揮発性記憶手段に情報が正しく書き込まれたか否かの判定を行なう判断手段を設けた。判断手段は、書込パルスのパルス長が所定の範囲にあるか否かや、書込パルスの到来と同時に時間を計測する計時手段などを用いることで、パルス長が正しいか否かを判定する。これにより、簡便な構成で、正しい情報の書き込みを判断できる。

(もっと読む)

半導体集積回路、故障診断システム、および、故障診断方法

【課題】埋め込みメモリの故障タイプを判定することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1のアドレス方向および第2のアドレス方向に配置された所定のデータを記憶する複数のメモリビットを含むメモリと、メモリの故障を診断するためのBIST回路と、を備える。BIST回路は、メモリに対するBISTを制御するBIST制御回路を有する。BIST回路は、第1のアドレス方向のBISTにより故障であると判断されたビットセルの第1のアドレス方向のアドレスである第1の不良ビットセル位置を格納し、第1の不良ビットセル位置におけるビットセルのフェイル数を格納し、フェイル数が予め設定された上限値を超えたか否かを示すフェイルオーバーフローフラグを格納する故障情報テーブルを有する。BIST回路は、メモリに対するBISTにより得られたBIST結果を出力する結果解析器と、を有する。

(もっと読む)

1 - 20 / 163

[ Back to top ]