Fターム[5M024AA70]の内容

Fターム[5M024AA70]に分類される特許

1 - 20 / 39

記憶素子の駆動方法及び半導体装置の駆動方法

【課題】記憶素子(DRAM)の保持情報の多値化を簡便に行うこと。

【解決手段】記憶素子(DRAM)が有するトランジスタがオン状態の期間において、当該記憶素子(DRAM)に対して情報の書き込みを行う配線(ビット線)の電位を変動させることで、当該記憶素子(DRAM)が有する容量素子に蓄積される電荷量を制御する。これにより、当該記憶素子(DRAM)を有する半導体装置の構造を複雑化せずとも記憶素子(DRAM)の保持情報を多値化することが可能である。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体メモリチップ及びこれを用いるマルチチップパッケージ

【課題】マルチチップパッケージのパッケージングを容易にし、半導体メモリチップとマルチチップパッケージのパッドとを接続するボンディングによって伝送される信号のローディングを一定にすることができるようにした半導体メモリチップを提供すること。

【解決手段】第1のデータ信号と第1のストローブ信号と第1のマスク信号とが入力される第1のパッド部と、第1のモードでは、前記第1のデータ信号と前記第1のストローブ信号と前記第1のマスク信号とを第1の書き込み経路回路に伝達し、交換モードでは、前記第1のデータ信号と前記第1のストローブ信号と前記第1のマスク信号とを第2の書き込み経路回路に伝達する第1の選択伝達部と、を備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ時間のマージンを十分に確保しつつ、微細化が可能な半導体記憶装置を提供することを目的とする。

【解決手段】メモリセルを、読み出しトランジスタ、書き込みトランジスタ、キャパシタにより構成する。かかる構成において、キャパシタは読み出しトランジスタのゲートにかかる電位を制御する。書き込みトランジスタは、データの書き込みおよび消去を制御するとともに、キャパシタに蓄積された電荷が、該書き込みトランジスタのリーク電流で消失しないように、オフ時の電流が小さいトランジスタで構成する。書き込みトランジスタを構成する半導体層は、読み出しトランジスタのゲート電極とソース領域の間を架橋するように設ける。キャパシタは、読み出しトランジスタのゲート電極と重畳するように設ける。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体メモリ装置

【課題】カラムリペア効率を向上させることができる半導体メモリ装置を提供する。

【解決手段】カラム方向に配置された複数のノーマルセルブロックO0〜O7とリダンダンシセルブロックR1とからなるバンクを備え、第1の入出力ストローブ信号に応じて、複数のノーマルセルブロックO0〜O7からそれぞれデータを入出力する複数のノーマルデータ入出力部300と、第1の入出力ストローブ信号に応じて、リダンダンシセルブロックR1からデータを入出力するリダンダンシデータ入出力部320と、カラムアドレスに応じて、複数のノーマルデータ入出力部300とリダンダンシデータ入出力部320とを選択的に複数のローカルデータラインに接続させる接続選択部340と、第2の入出力ストローブ信号に応じて、複数のローカルデータラインと複数のグローバルデータラインとの間でそれぞれデータを入出力する複数のローカルデータ入出力部360とを備える。

(もっと読む)

第2のコントロールゲートを絶縁層の下に埋め込んだSeOIDRAMメモリセルをコントロールする方法

【課題】DRAMメモリセルでより小型のトランジスタを使用できる方法を提供する。

【解決手段】ゲート誘電体7によってチャネルから分離されているフロント・コントロール・ゲート8、およびベース基板に配置され、かつ絶縁層(BOX)によってチャネル4から分離されているバック・コントロール・ゲート9と、を有するトランジスタからなるDRAMメモリセルコントロール方法において、セルプログラミング動作において、フロント・コントロール・ゲートおよびバック・コントロール・ゲートが、第1の電圧をフロント・コントロール・ゲートに、第2の電圧をバック・コントロール・ゲートに印加することによって共に使用され、第1の電圧の大きさは、バック・コントロール・ゲートに電圧が印加されない場合にセルをプログラミングするのに必要な電圧の大きさよりも小さい。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】貫通電極に接続されているすべての双方向バッファ回路の出力バッファがハイインピーダンスとなった場合でも、貫通電極が論理不定状態となることを防止する。

【解決手段】半導体装置10は、積層された複数のコアチップCC0〜CC7及びインターフェースチップIFとを備えている。複数のコアチップCC0〜CC7及びインターフェースチップIFの各々は、半導体基板を貫通する複数の貫通電極TSV1と、貫通電極TSV1を駆動する双方向バッファ回路BUとを含み、インターフェースチップIFは、貫通電極TSV1の論理レベルを保持する論理レベル保持回路26をさらに含んでいる。双方向バッファ回路BUは、入力バッファIB及び出力バッファOBを含み、論理レベル保持回路26の第1のインバータINV1の駆動能力は、双方向バッファ回路BUの出力バッファOBの駆動能力よりも小さい。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

マルチポートメモリおよびその制御方法

【課題】 マルチポートメモリのページ動作を容易に実行する。

【解決手段】 マルチポートメモリは、メモリセルを有する複数のメモリコアと、クロック信号を受けるクロック端子、メモリセルを選択するためにクロック信号に同期して供給されるアドレス信号を受けるアドレス端子、およびデータ信号を入出力するデータ入出力端子をそれぞれ有する複数の入出力ポートと、メモリコアにそれぞれ対応し、入出力ポートから供給されるアドレス信号のいずれかを選択し、選択したアドレス信号に応じてメモリセルをアクセスする制御回路と、複数個のメモリセルに対応するデータを保持するバッファとを有する。メモリセルに対して読み書きされるデータは、バッファを介してデータ入出力端子およびメモリセルに伝達される。

(もっと読む)

半導体集積回路装置

【課題】雑音特性が優れ、かつサイズが小さいメモリアレイ及びそのメモリアレイを備えた半導体集積回路装置を提供する。

【解決手段】ビット線と定電圧との間に、順番に直列に接続された2つのトランジスタと1つの記憶蓄積素子とを備えたメモリセルは、2つのトランジスタのゲート電極に第1のワード線、第2のワード線がそれぞれ接続され、メモリアレイは、メモリセルがビット線と第1のワード線が交差する全ての交点に配置されたマットと、同一マット内のビット線対を入力とするセンスアンプと、第1及び第2のワード線を出力する第1及び第2のワードドライバと、を備える。

(もっと読む)

遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法

【課題】レイアウトの大きさを増大させず、速やかに位相を固定させることができる遅延固定ループ及び遅延固定ループにおけるクロック遅延固定方法を提供すること。

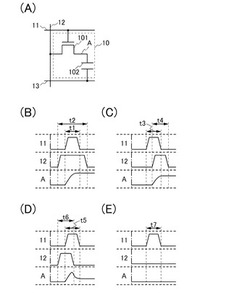

【解決手段】遅延ライン部は、第1の遅延時間d1を各々有する複数の第1の単位遅延セルを有し、クロック信号clkを遅延する第1遅延ラインと、第2の遅延時間d2を各々有する複数の第2の単位遅延セルを有し、第1遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第2遅延ラインと、第3の遅延時間d3を各々有する複数の第3の単位遅延セルを有し、第2遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第3遅延ラインとを備え、第1の遅延時間d1が第2の遅延時間d2より短く、第2の遅延時間d2が第3の遅延時間d3より短い。

(もっと読む)

半導体記憶装置

【課題】チップ面積を増やすことなく電源補償容量を確保する。

【解決手段】センスアンプ回路に電源を供給する電源ラインに、動作時の電源補強補償用として、メモリセル部の製造プロセス上必要なダミー配線であるダミーワード線を、電源供給配線として用いる半導体記憶装置。

(もっと読む)

半導体装置

【課題】 新たなメモリセルの選択方式を導入することによって、上述した諸問題を解決し安価なDRAMを提供することである。さらには、本選択方式は、その他のDRAMセル、あるいはスタティック・ランダムアクセスメモリ(SRAM)の高性能化にも寄与する。

【解決手段】 アレーを構成する行線Xと列線Yの交点にメモリセルMCが接続され、該1個のメモリセルは行線Xと列線Yで制御され、行線Xと列線Yのそれぞれにパルス電圧が印加されることによって該メモリセルMCが選択されてデータ線DLと信号の授受を行う。

(もっと読む)

半導体記憶装置

【課題】ECC機能を搭載したビット幅の広いメモリ装置においては、メモリアレイ部からECC回路部へのデータパスの配線レイアウトや遅延時間の増大を招く。またECC回路の処理ビット幅を広くすると回路段数の増加により、アクセス性能が悪化しレイアウト面積も増大する。

【解決手段】ワード線と直交する方向に形成されるデータ線に対して、データ線の延伸方向にデータラッチ300、マルチプレクサ601,602、ECC回路部401、入出力回路部500を列状に隣接して配置し、データパス系のレイアウトをビットスライス状に形成する。更に各ビットの遅延時間を均一化するため、パリティビットを均等に分散配置する。

(もっと読む)

半導体記憶装置と品種展開方法

【課題】同一チップで一度にアクセスされるデータ転送量を変えてもトータルのピークバンド幅を一定に保つ半導体記憶装置の提供。

【解決手段】複数のバンクと、複数のデータ入出力端子と、制御信号端子と、アドレス信号端子と、バンクをまとめて一つの独立したチップとして動作可能な少なくとも1つ又は複数のバーチャルチップを備え、複数のデータ入出力端子のそれぞれは1又は複数のバーチャルチップのいずれか一つに属すると共に、複数の制御信号端子と複数のアドレス信号端子は、1又は複数のバーチャルチップのそれぞれで共有される。

(もっと読む)

2つのゲート用トランジスタを有する多値メモリ記憶装置

本発明は、記憶素子(105)に結合された第1及び第2のノードをそれぞれ有し、互いに並列に配置された第1のゲート用トランジスタ(101)及び第2のゲート用トランジスタ(103)を具える多値メモリセル(111)と、前記第1のゲート用トランジスタ及び第2のゲート用トランジスタのそれぞれの第3のノード及び第4のノードに結合され、前記多値メモリセル(111)の記憶電圧を検出する検出回路(113、115)とを具えるデジタルメモリ装置及びシステム、並びにデジタルメモリ装置の動作方法を提供する。実施例では、第1及び第2のゲート用トランジスタ(101、103)を互いに異なるしきい値電圧レベルで駆動されるように構成する。  (もっと読む)

(もっと読む)

メモリの駆動方法、および、半導体記憶装置

【課題】リフレッシュ動作の頻度が少なく、データ保持時の消費電流が低く、さらに、小型化に優れたメモリを提供する。

【解決手段】メモリ駆動方法は、メモリセルのデータ劣化を回復させるリフレッシュ動作を実行する際に、フローティングボディの電位が或る臨界値よりも大きい場合には、フローティングボディ内に注入される多数キャリア数がフローティングボディから排出される多数キャリア数よりも多く、フローティングボディの電位が臨界値よりも小さい場合には、フローティングボディ内に注入される多数キャリア数がフローティングボディから排出される多数キャリア数よりも少ない。

(もっと読む)

1 - 20 / 39

[ Back to top ]