Fターム[5M024BB07]の内容

DRAM (26,723) | 改良の場所/タイミング (5,148) | 場所 (3,103) | アドレスデコーダ (78)

Fターム[5M024BB07]に分類される特許

1 - 20 / 78

半導体装置

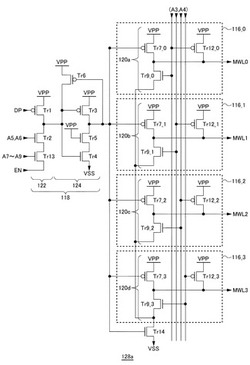

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

半導体装置

【課題】回路ブロックの数が2のべき乗で表すことのできない数であっても、簡単な回路構成でプリデコード動作を行う。

【解決手段】それぞれ異なるロウアドレスが割り当てられた複数のワード線WLを含む複数のメモリマットと、メモリマットにそれぞれ含まれるワード線WLの最小アドレスMINADDとアドレス信号のビットとを比較することによって、メモリマットのいずれかを選択するマットセレクタ12aと、アドレス信号のビットに基づいて、選択されたメモリマットに含まれるワード線WLのいずれかを選択するワードセレクタ12bとを備える。

(もっと読む)

アドレスデコーディング方法とこれを用いた半導体メモリ装置

【課題】半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

(もっと読む)

半導体装置

【課題】 隣接する他のワード線と短絡したワード線に接続されているメモリセルについて個々の評価試験を可能にする。

【解決手段】 半導体装置は、入力されるテストモード信号が活性化されたときに、一つのメインワード線に繋がる複数のサブワード線をそれぞれ駆動する複数のプリデコード信号を同時に活性化するプリデコード回路を含んでいる。

(もっと読む)

ローカル列デコーダに関連付けられた互い違いに配置されたセンスアンプを有する半導体メモリ

【課題】本発明は、少ししか列アドレスバスを必要としない半導体メモリを提供する。

【解決手段】本発明は、半導体メモリであって、ビット線と、メモリセルアレイと、少なくとも1組のセンスアンプバンクであって、各センスアンプは、交互の配列により、対応するビット線に接続されていることによって、ビット線と平行な各センスアンプバンクの組で利用可能なスペースに相互接続することを備え、各センスアンプバンクは、センスアンプバンクの少なくとも1つのセンスアンプを選択する、少なくとも1つのローカル列デコーダを備え、前記ローカル列デコーダは、ビット線と平行な利用可能な相互接続スペース内に走っている出力線によってセンスアンプバンクの少なくとも1つのセンスアンプと電気的に結合されたことを特徴とする半導体メモリに関するものである。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においていずれかのバンクがアクティブ状態であるか否かを判定する。

【解決手段】バンクアドレス信号BA及びアクティブ信号ACT0を出力するインターフェースチップIFと、インターフェースチップIFに積層され、それぞれ対応するバンクアドレス信号BA及びアクティブ信号ACT0を受けて独立にアクティブ状態となる複数のメモリバンクを備えるコアチップCC0〜CC7とを備える。コアチップCC0〜CC7は、其々に含まれる複数のメモリバンクの少なくとも1つがアクティブ状態であるか否かを示すローカルバンクアクティブ信号MCIDTをインターフェースチップIFに其々出力し、インターフェースチップIFは、ローカルバンクアクティブ信号MCIDTの少なくとも1つが活性状態を示すときにバンクアクティブ信号PMCITを活性化させる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

メモリ装置及びメモリシステム

【課題】アドレス空間の大きさが異なる複数のメモリ装置を同時にテストすることができるメモリ装置を提供することを課題とする。

【解決手段】アドレス空間の大きさが異なる複数のメモリ装置に対して複数ビットのアドレスのうちの一部のビットが共通のアドレスを入力して同時にテストを行う際のアドレス空間の小さい方のメモリ装置であって、アドレスにデータを記憶するメモリセルアレイと、メモリセルアレイのアクセスの回数をカウントするカウンタ(702)と、カウンタによりカウントされたアクセスの回数と回数設定値とを比較する比較回路(703)と、テストモードにおいて、カウンタによりカウントされたアクセスの回数が回数設定値に到達するとメモリセルアレイへのアクセスを禁止する動作停止制御回路(704)とを有するメモリ装置が提供される。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】アドレス信号を伝達するための回路を有する半導体メモリ装置及びその動作方法を提供する。

【解決手段】ノーマルアドレス信号に応答してリペアアドレス信号を生成するリペアアドレス生成部340と、リペアアドレス信号の有効性の可否に応じて、ノーマルアドレス信号とリペアアドレス信号とを混合してライン選択アドレス信号を生成するライン選択アドレス生成部350と、リペアアドレス信号の有効性の可否に応じて、ノーマルセル領域およびリダンダンシセル領域のうちいずれか一方のセル領域を選択し、選択したセル領域に具備された多数のローカルセルラインのうちいずれか一つのローカルセルラインを、ライン選択アドレス信号に応答して選択するセルラインデコーディング部320とを具備する半導体メモリ装置を提供する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】書き込み用トランジスタと読み出し用トランジスタで、共通のビット線を使用することで、単位メモリセル当たりの配線数を削減する。情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極またはドレイン電極の一方と、読み出し用トランジスタのゲート電極が電気的に接続されたノードにビット線の電位を供給し、その後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させる。情報の読み出しは、読み出し用トランジスタのソース電極またはドレイン電極の一方と接続された読み出し信号線に、所定の読み出し用の電位を供給し、その後、ビット線の電位を検知することで行う。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース電極またはドレイン電極と、が、第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、を異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

アドレス制御回路及び半導体メモリ装置

【課題】ライト動作でスキューの発生を最小化できるアドレス制御回路及び半導体メモリ装置を開示する。

【解決手段】リード動作実行のための第1のバースト区間で、アドレスからリードカラムアドレスを生成するリードカラムアドレス制御回路と、ライト動作実行のための第2のバースト区間で、前記アドレスからライトカラムアドレスを生成するライトカラムアドレス制御回路と、を含むアドレス制御回路を提供する。

(もっと読む)

メモリ装置を動作する方法、メモリ装置のリフレッシュ動作遂行方法、メモリ装置、及びメモリシステム

【課題】サブスタンダードメモリセルの位置に基づいたロウアドレスコード選択を提供する。

【解決手段】メモリ装置はサブスタンダードメモリセルを含むメモリブロックを識別し、ロウアドレスコードを決定してリフレッシュ動作の間にロウアドレスコードをメモリブロックに印加する。ロウアドレスコードはメモリブロックのうち同時にリフレッシュされるメモリブロックを決定し、他のメモリセルよりさらに短い周期でリフレッシュするべきサブスタンダードメモリセルを含むメモリブロックが同時にリフレッシュでき、サブスタンダ−ドメモリセルを含まないメモリブロックが同時にリフレッシュできるように設計される。

(もっと読む)

半導体装置及びデータ処理システム

【課題】内部動作電圧VPERIが外部電圧VDDに比べて十分に低い場合であっても、ビット線対とローカルIO線対との間のデータ転送が高速化された半導体装置を提供する。

【解決手段】半導体装置10は、振幅VDDを有するアドレス信号を受け付ける入力バッファ42と、入力バッファ42から出力されたアドレス信号の振幅をVDDよりも小さい振幅VPERIに変換するレベルシフト回路43と、レベルシフト回路43から出力されたアドレス信号を受け付けるアドレス制御回路50と、アドレス制御回路50から出力されるアドレス信号をデコードすることによりデコード信号を生成するアドレスデコーダ61,65と、少なくともデコード信号の振幅レベルがVDDとなるように、前記アドレス信号又は前記デコード信号の振幅をVPERIからVDDに変換するレベルシフト回路53,54とを備える。

(もっと読む)

ワード線選択回路、ロウデコーダ

【課題】ワード線ごとにレベルシフト回路を必要としないワード線選択回路を提供する。

【解決手段】出力ノードがワード線に接続されており、昇圧された電源電位VPPを電源として駆動するインバータ回路300と、インバータ回路300の入力ノードに出力配線された制御出力ノードを有し、前段のロウデコーダからのアドレス制御信号群をデコードした結果に基づいて制御出力ノードの電位を変化させる最終段ロウデコーダ200と、を備える。最終段ロウデコーダ300は、昇圧された電源電位VPPと制御出力ノードとの間に可変抵抗手段を備える。可変抵抗手段の抵抗値はアドレス制御信号群の少なくとも一つによって制御される。前段のロウデコーダからのアドレス制御信号群は、昇圧されていない電源電位VDD系の信号である。可変抵抗手段はpMOSトランジスタである。

(もっと読む)

半導体記憶装置

【課題】選択信号を印加せずに、メモリセルからデータを読出す。

【解決手段】第1データを保持し第1ワード線により選択される第1素子と、第2データを保持し第1ワード線により選択される第2素子と、第3データを保持し第2ワード線により選択される第3素子と、第4データを保持し第2ワード線により選択される第4素子と、行アドレスを保持する行アドレス保持部を有し、第1行アドレスと行アドレス保持部が出力する第2行アドレスが一致する場合に制御信号を出力する比較部と、行アドレスをデコードして第1又は第2ワード線に選択信号を出力し、制御信号が入力される場合には選択信号の出力を抑止する行アドレスデコーダと、選択信号により第1データ又は第3データを保持する第1の読出保持部と、選択信号により第2データ又は第4データを保持する第2の読出保持部を有する半導体記憶装置が提供される。

(もっと読む)

半導体メモリ装置

【課題】読出しマージンを増加させて読出し動作の正確度を高め、素子動作の信頼性を向上させることが可能な半導体メモリ装置を提供する。

【解決手段】メモリセルが連結された複数のワード線、複数のビット線及び複数の反転ビット線を含むメモリセルアレイと、複数のワード線のいずれか1本を選択するロウデコーダと、アドレス信号に応じてビット線選択信号を生成し、互いに隣接した2本のビット線、または互いに隣接した2本の反転ビット線を同時に選択するカラムデコーダと、ロウデコーダ及びカラムデコーダによって選択された各メモリセルにそれぞれ記憶されたデータを読み取るための複数のセンスアンプとを備えてなり、互いに隣接した2本のビット線または互いに隣接した2本の反転ビット線が同時に選択され、選択された二つのメモリセルがセンスアンプの第1入力端に同時に並列連結され、第2入力端に基準電圧が印加され、データが読み出される。

(もっと読む)

半導体記憶装置

【課題】高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を提供する。

【解決手段】第1方向に沿って配置された複数のメモリアレイ領域と、上記複数のメモリアレイ領域と交互に配置された複数のワード選択領域とを有し、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のワード線と、上記第1方向と直交する第2方向に沿って設けられた複数のビット線と、上記複数のワード線と上記複数のビット線との交差部に対応して設けられた複数のメモリセルとを備え、各ワード線選択領域に隣接する両側のメモリアレイ領域のうちの一方に延びるワード線及び他方に延びるワード線のそれぞれに対応してワード線選択回路が上記各ワード線選択領域内に設けられ、各メモリアレイ領域に対するそれぞれのワード線選択タイミングが独立に制御される。

(もっと読む)

半導体集積回路

【課題】tAA(アドレスアクセスタイム)が改善された半導体集積回路を提供する。

【解決手段】外部からライトモード及びリードモードを定義する命令語を提供することで、立ち上りクロック又は立ち下りクロックを用いて、ライト命令又はリード命令を提供する命令語デコーダ110、前記ライト命令に応じて、ライトレイテンシだけ外部アドレス及び前記ライト命令をシフトさせるシフトレジスタ部130、及び、前記リードモード時には前記外部アドレスをコラムアドレスとしてラッチし、前記ライトモード時には前記シフトレジスタから提供されたライト用アドレスをラッチして、前記コラムアドレスとして提供するコラムアドレスラッチ部160を含む。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】アクセス速度の低下を最小限に抑制しつつ、プリデコード信号のリセットによる消費電力の増大を防止する。

【解決手段】ロウアドレスRADTをプリデコードすることによりプリデコード信号RFを生成するプリデコーダ100と、ロウアドレスRADTが不良アドレスであるか否かを判定する救済判定回路300と、救済判定回路300によりロウアドレスRADTが不良アドレスであると判定された場合に、救済アドレスRREDを生成する救済アドレスデコーダ400と、プリチャージコマンドの発行に応答して、プリデコード信号RFをリセットすることなく救済アドレスRREDをリセットする信号制御回路200とを備える。これにより、プリデコード信号RFのリセットによる消費電力の増大が防止される一方、ロウ系アクセスを律速する冗長パスについては高速なアクセスが担保される。

(もっと読む)

1 - 20 / 78

[ Back to top ]