Fターム[5M024BB08]の内容

DRAM (26,723) | 改良の場所/タイミング (5,148) | 場所 (3,103) | ワード線駆動回路 (111)

Fターム[5M024BB08]に分類される特許

1 - 20 / 111

半導体装置

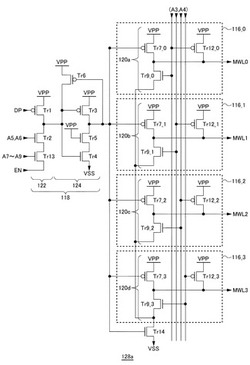

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

メモリにおけるピーク電力管理のためのメカニズム

【課題】メモリにおけるピーク消費電力管理のためのメカニズムを提供する。

【解決手段】サブ・アレイ・ブロックを含むメモリ・ストレージ・アレイにおけるピーク電力を管理するためのメカニズムが、サブ・アレイ・ブロックの各々に対するワードライン信号の起動を互い違いにすることにより、読み出し動作及び書き込み動作と関連したピーク電流を削減することができる。具体的には、1つのサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの書き込みワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、各々のサブ・アレイ・ブロックに対してワードライン信号を生成することができる。さらに、ワードライン・ユニットは、所与のサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの読み出しワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、ワードライン信号を生成することができる。

(もっと読む)

半導体装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線にビット線制御トランジスタを直列に挿入し、そのゲートの最低電位は十分な負の値となるようにする。ビット線制御トランジスタのゲートは電池等に接続するビット線制御回路に接続される。ビット線の最低電位はワード線の最低電位よりも高くなるようにする。外部からの電源が切れた際には、ビット線はビット線制御トランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。あるいは外部電源遮断時にワード線の電位を十分な負の電位とできるような回路を設けてもよい。

(もっと読む)

ワード線分割回路、及び記憶装置

【課題】回路構成が簡略化され、安定して動作可能なワード線分割回路を提供する。また、回路構成が簡略化され、安定して動作可能な記憶装置を提供する。

【解決手段】ワード線と、サブワード線との間に、リーク電流が極めて低減されたトランジスタを直列に接続し、ワード線分割回路を構成すればよい。当該トランジスタには、チャネルが形成される半導体層に酸化物半導体を含むトランジスタを適用できる。また、このような回路構成が簡略化されたワード線分割回路を、記憶装置に適用すればよい。

(もっと読む)

半導体装置

【課題】ワード線の活性化電位への立ち上がりの遅れを回避しチップサイズの縮小化、動作速度の高速化に対応可能とする。

【解決手段】メモリセル容量(C)と、前記メモリセル容量及びビット線(BLT)との間に設けられたメモリセルトランジスタ(NM)と、前記メモリセルトランジスタの制御電極に接続されるワード線(SWL)と、前記ワード線を駆動するワードドライバ(SWD)と、を備えた半導体装置であって、前記ワードドライバは、前記ワード線を活性化させる第1の期間、及びそれに続く第2の期間において、それぞれ第1の電源電圧、及び、第2の電源電圧により前記ワード線を駆動し、前記第1の電源電圧は前記第2の電源電圧よりも高い電位である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミスを防ぐことが可能である。

(もっと読む)

半導体記憶装置

【課題】ワード選択スピードを向上することができ、また動作電流の低減を図ることが可能な半導体記憶装置を提供することである。

【解決手段】本発明かかる半導体記憶装置は、メインワードデコーダ1と、サブワードドライバ2_1〜2_4と、両端にサブワードドライバ2_1、2_2がそれぞれ設けられると共に、複数のサブワード線を含む第1のメモリセルアレイ3_1と、メインワードデコーダ1から最も離れた位置に配置され、サブワードドライバ2_3、2_4がメインワードデコーダ1に近い側のみに配置された第2のメモリセルアレイ3_2と、を備える。メインワード線4およびプリデコード線5は、メインワードデコーダ1から第2のメモリセルアレイ3_2のサブワードドライバ2_4まで延びるように配置されている。

(もっと読む)

半導体装置

【課題】ワード線非活性化における情報破壊を防止する半導体装置を提供すること。

【解決手段】半導体装置は、ワード線及びビット線を含むメモリセルマットと、サブワードドライバ回路と、サブワードドライバ回路を制御する第1制御部と、を有するメモリセルアレイを備える。第2制御部は、第1電源電位を低電位側とする第1電源電圧で動作する第3回路部と、第1電源電位よりも低い第2電源電位を低電位側とする第2電源電圧で動作する第4回路部と、を含む。第2制御部は、サブワードドライバ回路に第1制御信号を供給し、第1制御部に第2制御信号を供給する。第1制御部は、第1電源電位を受け取らずに第2電源電位を低電位側とする第3電源電圧で動作し、第2制御信号を受け取り第3制御信号をサブワードドライバ回路に供給する。サブワードドライバ回路は、第1制御信号と第3制御信号とを受け取り、活性状態のワード線を非線形に非活性状態とする。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

ロジックプロセスで埋め込まれたDRAMのためのワード線ドライバ

【課題】慣用のロジックプロセスによる埋込みDRAMセルのデータ保持性能を改善できるワード線ドライバを提供する。

【解決手段】慣用のロジックプロセスによるpチャネルトランジスタ101を含むDRAMセルにアクセスするためのワード線ドライバを提供する。このワード線ドライバは、p型基板の中の深いn型ウェル領域の中に配置したp型ウェル領域に設けたnチャネルトランジスタ313を含む。負極性のブースト電圧供給源から前記p型ウェルおよび前記nチャネルトランジスタのソースに負極性ブースト電圧を供給する。この負極性ブースト電圧は、pチャネルアクセストランジスタのスレッショルド電圧以上の電圧値だけ接地電位よりも低い。深いn型ウェルおよびp型基板は接地電位点に接続する。

(もっと読む)

半導体記憶装置

【課題】メモリセルの非アクティブ(非選択)時に定常的なリーク電流が発生するのを防止する半導体記憶装置を提供する。

【解決手段】ビット線(BIT/BITB)と、前記ビット線に接続されるメモリ要素(メモリセルまたはローカルセンスアンプ)と、ワード線が活性化(WL=H)されることにより前記メモリ要素がアクティブ状態とされる直前の所定期間(PRE=L)だけ前記ビット線に所定電圧(VDD)を印加するプリチャージ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】複数のメインワード線を備える半導体記憶装置において、複数のメインワード線を同時に活性化したいという要望が存在する。しかし、1本のメインワード線を駆動可能な能力を持つドライバでは、複数のメインワード線を同時に活性化することができない。そのため、複数のメインワード線を同時に活性化する半導体記憶装置が望まれる。

【解決手段】図1に示す半導体記憶装置は、第1及び第2のメインワード線と、外部から入力されるテストコマンドに応じて、第1のメインワード線を第1のタイミングで活性化させ、かつ、第1のメインワード線の活性状態を維持させたまま第1のタイミングとは異なる第2のタイミングで第2のメインワード線を活性化させる制御回路と、を備える。

(もっと読む)

半導体装置

【課題】センスアンプのイコライズ速度を高めつつ、イコライズ動作とワード線のリセット動作との同期を取る。

【解決手段】ビット線対BLT,BLBをイコライズするイコライズ回路を含むセンスアンプSAと、イコライズ信号EQBの振幅をVDDレベルに変換するイコライズ制御回路64と、タイミング信号に基づいてサブワード線SWLを制御するワードドライバWDとを備える。ワードドライバWDは、VDDレベルに応じてサブワード線SWLの動作タイミングを変化させるためのレベルシフト回路LV1を含んでおり、これによりVDDレベルが変化した場合であっても、イコライズ動作の完了タイミングとサブワード線のリセットタイミングが連動する。

(もっと読む)

半導体メモリ装置及び半導体メモリ・システム

【課題】ビットライン間のカップリング、またはワードライン間のカップリングを低減させることができる半導体メモリ装置を提供する。

【解決手段】第1ビットラインBL12に連結される第1メモリセルを含む第1領域SMCB1、及び第2ビットラインBL22に連結される第2メモリセルを含む第2領域SMCB2を具備する複数のメモリセル・ブロック110_1〜110_8と、対応するメモリセル・ブロックの前記第1メモリセル、または前記第2メモリセルと連結される複数のビットライン・センスアンプ120_1〜120_6と、第1ビットラインを、対応するビットライン・センスアンプに連結したり、グローバル・ビットラインGBL1〜GBL8を介して、前記第2ビットラインを、前記対応するビットライン・センスアンプに連結する複数の連結部130_1〜130_8と、を具備する。

(もっと読む)

半導体記憶装置

【課題】ネガティブワード線方式の半導体記憶装置において非選択ワード線の電位を安定させる。

【解決手段】少なくとも1つのメモリブロック(60)を備えた半導体記憶装置(50)において、第1の負電位を出力する第1の負電位発生回路(64)と、第2の負電位を出力する第2の負電位発生回路(65)と、メモリブロックにおけるワード線(13)と第1の負電位との間の第1の放電経路(25)と、ワード線(13)と第2の負電位との間の第2の放電経路(21)とを備えている。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

半導体記憶装置

【課題】ワード線間の寄生容量が相対的に大きくなっても性能が低下しない半導体記憶装置を提供する。

【解決手段】第1の方向に配線された複数のワード線と、第1の方向と交差する方向に配線された複数のビット線と、複数のワード線とビット線との交点に対応して設けられた複数のDRAMセルを備えるメモリセルアレイと、複数のワード線を駆動するワード線ドライバと、複数のワード線それぞれに接続されメモリセルアレイを間に挟んで、ワード線ドライバに対して反対側に配置され、当該ワード線に隣接するワード線が選択されたときに導通して当該ワード線を非選択電位に接続し、当該ワード線が選択されたときに非導通となる複数のワード線電位安定化トランジスタと、を備える。

(もっと読む)

レベル変換器を備える行デコーダ

【課題】CMOSのDRAMの記憶コンデンサの初期電圧を大きくし、また時間が経つにつれて電荷が漏れ出す速度を小さくする方法を提供する。

【解決手段】第1電圧範囲を持つ第1入力信号81に応答して第1出力信号を出すデコーダ回路10を備える。出力回路11は前記第1出力信号に応答して、第2電圧範囲を持つ第2出力信号26を出す。第2電圧範囲は、前記第1電圧範囲の最小電圧より小さい電圧と、前記第1電圧範囲の最大電圧より大きい電圧を含む。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1の信号線と、第2の信号線と、メモリセルと、電位変換回路と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、第1のドレイン電極、及び第1のチャネル形成領域を含む第1のトランジスタと、第2のゲート電極、第2のソース電極、第2のドレイン電極、及び第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、第1のチャネル形成領域は、第2のチャネル形成領域とは、異なる半導体材料を含んで構成され、第2のドレイン電極と、容量素子の電極の一方と、第1のゲート電極と、は電気的に接続され、第2のゲート電極は、第2の信号線を介して電位変換回路と電気的に接続される。

(もっと読む)

1 - 20 / 111

[ Back to top ]