Fターム[5M024CC20]の内容

Fターム[5M024CC20]に分類される特許

1 - 20 / 92

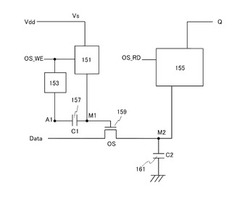

記憶装置、記憶装置の駆動方法

【課題】書き込み速度を損なうことなく、消費電力の低減された記憶装置を提供する。

【解決手段】書き込み信号に応じて、第1のノードに電源電位を入力するか、電位を保持させるか、接地させるかを選択するコントローラと、一方の電極が前記第1のノードに接続する第1の容量素子と、第1の容量素子の他方の電極に、書き込み信号を遅延して出力する遅延回路と、第1のノードと接続されるゲート電極と、入力データ信号が入力される第1の電極と、入力データ信号を記憶する第2のノードと接続される第2の電極とを備える第1のトランジスタと、第2のノードと接続され、読み出し信号に応じて第2のノードの電位に応じた信号を出力する読み出し回路と、を有し、第2のノードは、一方の電極が接地された第2の容量素子の他方の電極と、読み出し回路が備える第2のトランジスタのゲート電極と、が接続される記憶装置を提供すること。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置

【課題】フローティングボディにデータを記憶するメモリセルを備えた半導体装置において、トリガ素子となる能動素子を設けなくともメモリセルの導通、非導通状態を確実に制御する。

【解決手段】ビット線BLと、ワード線WLと、第1の端子がビット線に接続され、第2の端子がワード線に接続されたメモリセル66と、メモリセルに対するデータの書込み時に、書込みデータの如何に係わらず、ビット線とワード線を選択し、メモリセルを導通させた後、ビット線の電圧レベルを書込みデータに応じた電圧レベルに設定し、メモリセルにデータを書込む制御回路を備える。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなる。

【解決手段】1つのビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと4乃至64個のメモリセル(CL_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr1_n_mとSTr2_n_mを有し、また、選択トランジスタSTr2_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線に出力できる。

(もっと読む)

半導体装置

【課題】電流値変化型メモリセルの読み出し動作時に、ビット線電位を低電圧化しても十分な動作マージンを確保可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、電流値変化型メモリセルMCと、ビット線BLと、トランジスタQ1〜Q4からなるセンスアンプSAを備えている。電荷転送ゲートであるトランジスタQ1は転送制御電圧である電位V1に応じてビット線BLとセンスノードNSとの間の接続を制御し、トランジスタQ2はセンスノードNSの信号を増幅する。トランジスタQ3は電位V2をセンスノードに供給し、トランジスタQ4は電位V3をビット線に供給し、ともにプリチャージ制御信号PCに応じて制御される。電位V2を電位V3より高く設定し、電位V1からトランジスタQ1の閾値電圧Vt1を引いた所定電位が電位V3より低く、かつ低電位より高くなるように設定することで、読み出し動作の動作マージンが向上する。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ抵抗が極めて高いトランジスタをスイッチング素子として有するメモリセルを構成するに際し、信頼性を高める検査方法および構成を提供する。

【解決手段】メモリセルのトランジスタのしきい値Vthが許容される範囲内にあるか否かを判定することにより、データ保持特性が十分でないメモリセルを排除する。そのためにトランジスタのゲートの電位を適切な電位VGMに保持し、また、トランジスタのドレインの電位をVGM以上の電位にする。この状態でメモリセルに書き込むことにより、トランジスタのソースの電位はしきい値Vthを含む式、(VGM−Vth)で表現される。この電位と他の参照電位との大小を比較することによりしきい値Vthが許容される範囲内にあるか否かを判定できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

半導体メモリ装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを2つ用いて形成された記憶ユニットのマトリクスにおいて、第1の記憶セルの書き込みトランジスタのゲートを第1のワード線に、キャパシタの他方の電極を第2のワード線に接続する。また、第2の記憶セルの書き込みトランジスタのゲートを第2のワード線に、キャパシタの他方の電極を第1のワード線に接続する。さらに、集積度を高めるために、各記憶セルの読み出しトランジスタのゲートを互い違いに配置する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置及び半導体装置を含む情報処理システム

【課題】フローティングボディ構造の選択トランジスタを用いたメモリセルに対し、ビット線の電位を適切に制御することによりリーク電流を抑制可能な半導体装置を実現する。

【解決手段】本発明の半導体装置において、キャパシタCsと選択トランジスタQ0とを含むメモリセルMCを備え、この選択トランジスタQ0はフローティングボディ24を有している。メモリセルMCに接続されるビット線BLは、第1の電位設定回路Q1により第1の電位VBLPに設定され、さらに読み出し動作に先立って第2の電位設定回路Q3により第1の電位VBLPとは異なる第2の電位VBLRに設定される。センスアンプ30は、この状態のビット線BLを介してメモリセルMCから読み出される信号を増幅する。第1の電位VBLP及び第2の電位VBLRを適切に設定することにより、メモリセルMCのリーク電流を抑え、情報保持時間を長くして消費電流を低減可能となる。

(もっと読む)

縦型バイポーラインジェクタを有するDRAMメモリセル

【課題】フローティングボディDRAMセルにおいて表面積が縮小された改良型メモリセルを提供する。

【解決手段】ソースSと、ドレインDと、ソースSとドレインD間のフローティングボディFBとを有するFETトランジスタと、FETトランジスタのフローティングボディへの電荷の注入を制御可能なインジェクタであって、エミッタ15と、ベースと、FETトランジスタのフローティングボディFBによって形成されたコレクタとを有するバイポーラトランジスタからなるインジェクタとを備え、バイポーラトランジスタのエミッタ15が、FETトランジスタのソース22がバイポーラトランジスタのベースとして働くように配置される。複数のメモリセルを備えるメモリアレイ、及びこのようなメモリセルを制御する方法にも適用される。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

第2のコントロールゲートを絶縁層の下に埋め込んだSeOIDRAMメモリセルをコントロールする方法

【課題】DRAMメモリセルでより小型のトランジスタを使用できる方法を提供する。

【解決手段】ゲート誘電体7によってチャネルから分離されているフロント・コントロール・ゲート8、およびベース基板に配置され、かつ絶縁層(BOX)によってチャネル4から分離されているバック・コントロール・ゲート9と、を有するトランジスタからなるDRAMメモリセルコントロール方法において、セルプログラミング動作において、フロント・コントロール・ゲートおよびバック・コントロール・ゲートが、第1の電圧をフロント・コントロール・ゲートに、第2の電圧をバック・コントロール・ゲートに印加することによって共に使用され、第1の電圧の大きさは、バック・コントロール・ゲートに電圧が印加されない場合にセルをプログラミングするのに必要な電圧の大きさよりも小さい。

(もっと読む)

半導体記憶装置

【課題】リテンション時間を高めて消費電力を削減するとともに、回路面積の増大も抑制する。

【解決手段】ワード線とビット線の交点に配列されたメモリセルから読み出された信号をセンスアンプ回路にて検知増幅する。書き込み回路は、複数のメモリセルのうちの第1のメモリセルに保持された第1データを読み出して第1のメモリセルとは別の第2のメモリセルに第1データに対応する第2データを書き込む。データラッチ回路は、第1のメモリセルから読み出されたデータを保持する。論理演算回路は、第2のメモリセルから読み出されたデータとデータラッチ回路に保持されたデータとを入力値とした論理演算を実行して第3データを演算値として出力する。書き戻し回路は、第3データを第1のメモリセルに対し書き戻す。

(もっと読む)

半導体記憶装置

【課題】不良救済効率を改善する。

【解決手段】サブワード線レベルの不良のときとメインワード線レベルの不良のときとで、スペアワード線の選択態様を変更する。スペア判定結果信号SP2が活性化される時同時にスペア判定結果信号SP1が活性化される時には、3本のノーマルサブワード線間においてショート不良が存在する。この場合には、スペア判定結果信号SP1が活性化されるため、ノーマルロウデコーダ264が非活性状態であり、スペアメインワード線のみが選択されてスペアサブワード線対により不良救済が実行される。この場合においても、ツインセルモードにしたがってサブワード線を選択することができる。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】データ書き込み時のノイズ発生に起因するデータの損失を、少ない消費電力で防止可能な半導体記憶装置及びその制御方法を提供する。

【解決手段】電源供給部2が、メモリセルアレイ1のメモリセルのMOS型キャパシタのゲート電極に接続されるプレート線PLに、プレート電圧Vplを供給し、スイッチ(nMOSQ7)が、メモリセルアレイ1へのアクセス発生時に、プレート線PLを第1電源線に接続することで、データ書き込み時のノイズの影響を除去する。

(もっと読む)

半導体メモリ装置及びそのリフレッシュ制御方法

【課題】本発明は、メモリコア領域のセルトランジスタにFBC技術を実現した半導体メモリ装置及びそのリフレッシュ制御方法を提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、ワードラインと接続するゲート、ビットラインとソースラインに連結するドレイン及びソースをそれぞれ備え、ソースラインを共有してトランジスタ対を形成する複数のFBC(Floating Body Cell)トランジスタからなるメモリセルブロックを含み、リフレッシュ信号がイネーブルされれば、リフレッシュリード信号をイネーブルさせて前記メモリセルブロックに格納されたデータを読み出した後、リフレッシュライト信号をイネーブルさせて前記読み出したデータを前記メモリセルブロックに再記入するように構成されることを特徴とする。

(もっと読む)

1 - 20 / 92

[ Back to top ]