国際特許分類[B41J2/455]の内容

処理操作;運輸 (1,245,546) | 印刷;線画機;タイプライター;スタンプ (167,967) | タイプライタ;選択的プリンティング機構,すなわち版以外の手段でプリンティングする機構;誤植の修正 (126,579) | 設計されるプリンティングまたはマーキング方法に特徴があるタイプライタまたは選択的プリンティング機構 (70,284) | プリンティング材料または印刷転写材料への放射線の選択的適用に特徴があるもの (10,339) | アレイ放射源を使用するもの (3,758) | レーザーアレイを用いるもの (1,860)

国際特許分類[B41J2/455]に分類される特許

31 - 40 / 1,860

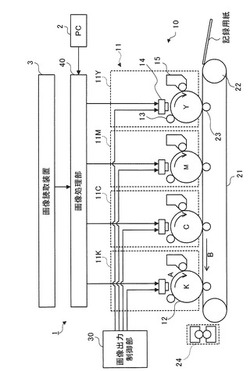

画像形成装置および発光素子ヘッド

【課題】形成される画像の乱れを抑制しつつ、主走査方向の倍率の補正を行なうことができる画像形成装置等を提供する。

【解決手段】スクリーン処理手段と、感光体ドラム12と、感光体ドラム12を帯電させる帯電器13と、発光素子からなる第1の発光素子列と、発光素子からなり第1の発光素子列と少なくとも一部が副走査方向に重複して配される第2の発光素子列と、光を結像させて感光体ドラム12を露光して静電潜像を形成させる光学素子と、を備える発光素子ヘッド14と、静電潜像を現像してトナー像を形成する現像器15と、発光素子からの光の光量を設定する光量設定部と、を備え、発光素子ヘッド14の第1の発光素子列の発光素子と第2の発光素子列の発光素子の間隔とは、重複する箇所において異なり、光量設定部は、重複する箇所の発光素子の光量をスクリーンに応じて設定することを特徴とする画像形成装置1。

(もっと読む)

光プリントヘッド、プロセスカートリッジ及び画像形成装置

【課題】幅狭の光プリントヘッドであっても、十分な剛性が確保でき、組み立ての容易な構造の光プリントヘッドを提供する。

【解決手段】少なくとも感光体及び現像装置を二方向から挟んで位置決めする画像形成装置の面板に、長手方向の両端部側が担持されるプリントヘッドであって、長手方向の両端部側が前記面板に担持される角管形状の本体フレーム20と、本体フレーム20内部に固定され、複数のLED素子からなるLEDアレイチップ12を有する基板11と、本体フレーム20のLEDアレイチップ12に対向するフレーム面にLEDアレイチップ12に対応して固定されるロッドレンズアレイ14と、を備える。

(もっと読む)

光源制御装置及び画像形成装置

【課題】処理規模及び回路規模の増大によるコストアップを招くことなく、簡易な構成で画像データ及び内部パターンのミラーリング処理を行うこと。

【解決手段】電子写真方式の画像形成装置において像担持体上に静電潜像を形成する光源の発光を入力された画像データに基づいて制御する光源制御装置であって、前記画像データに応じて位置合わせや濃度補正等のための内部パターンを生成するパターン生成部と、前記パターン生成部の後段で前記内部パターン及び前記画像データのミラーリング処理を行うミラーリング処理手段と、を有する光源制御装置により、処理規模及び回路規模を増大させることなく、簡易な構成でミラーリング処理が可能な光源制御装置を提供することができる。

(もっと読む)

自己走査型発光素子アレイ、光書込みヘッドおよび画像形成装置

【課題】高出力化を図る自己走査型発光素子アレイを提供する。

【解決手段】自己走査型発光素子アレイ10は、半導体基板と、半導体基板上に形成された島Sn-1、Sn、Sn+1、Sn+2と、当該島内に積層されたpnpn構造の半導体層を含む発光部サイリスタLn−1、Ln、Ln+1、Ln+2と、当該島内に積層されたpnpn構造の半導体層を含むシフト部サイリスタTnー1、Tn、Tn+1、Tn+2と、当該島内に積層されたpn接合の結合ダイオードの直下に形成された寄生サイリスタPTn、PTn+1、PTn+2、PTn+3と、当該島内に形成された電流狭窄層とを有する。電流狭窄層は、酸化領域と非酸化領域とを含み、寄生サイリスタのカソード層28PTの直下には酸化領域が形成される。

(もっと読む)

自己走査型発光素子アレイ、光書込みヘッドおよび画像形成装置

【課題】高出力化を図る自己走査型発光素子アレイを提供する。

【解決手段】自己走査型発光素子アレイは、半導体基板と、半導体基板上に形成された島Sn-1、Sn、Sn+1、Sn+2と、当該島内に積層されたpnpn構造の半導体層を含む発光部サイリスタLn-1、Ln、Ln+1、Ln+2と、当該島内に積層されたpnpn構造の半導体層を含むシフト部サイリスタTn-1、Tn、Tn+1、Tn+2と、当該島内に積層されたpn接合の結合ダイオードの直下に形成された寄生サイリスタPTn、PTn+1、PTn+2、PTn+3と、当該島内に形成された電流狭窄層とを有する。電流狭窄層は、酸化領域と非酸化領域とを含み、寄生サイリスタのカソード層の直下には酸化領域が形成される。

(もっと読む)

露光装置、画像形成装置、及びプログラム

【課題】発光素子間の光量のばらつきを抑制する露光装置、画像形成装置、及びプログラムを提供する。

【解決手段】特定の使用条件下で発光させた場合の相互間の光量のばらつきが補正された複数のLEDを異なる使用条件下で発光させた際のLED間の光量のばらつきが所定範囲内に収まるようにLEDの各々の光量を補正するための出荷後光量むら補正値を記憶したEEPROM112と、特定の使用条件とは異なる使用条件に相当する使用条件を満足した場合に、EEPROMに記憶されている出荷後光量むら補正値に従って発光対象とされたLEDの光量を補正する補正値演算部112と、を備える。

(もっと読む)

ホログラム記録媒体、ホログラム記録装置、プログラム、露光装置及び画像形成装置

【課題】複数の半導体発光素子を有する基板上に配置されたホログラム記録層にホログラムを記録する際に、半導体発光素子の光起電力を利用して、半導体発光素子毎にホログラムの記録条件を設定することができるホログラム記録媒体、ホログラム記録装置等を提供する。

【解決手段】複数の半導体発光素子を有する基板、基板上に配置されたホログラム記録層、及び半導体発光素子の一対の電極の各々から引き出された複数の端子を有するホログラム記録媒体を用いる。ホログラム記録装置は、ホログラム記録媒体を保持する保持手段と、複数の端子と電気的に接続されて半導体発光素子に発生した光起電力を測定する測定手段と、ホログラム記録層にホログラムを記録する記録手段と、測定された光起電力の値に基づいてホログラムを記録する記録条件を取得すると共に、取得された記録条件に基づいてホログラムが記録されるように各手段を駆動制御する制御手段と、を有する。

(もっと読む)

光量補正方法、及び画像形成装置

【課題】発光素子の光量の補正量の飛びを小さくことで、きめの細かな光量補正を可能とする。

【解決手段】補正範囲Es内にて光量を補正する光量補正部100を用いて、LEDアレイ41の各発光素子間の光量差を小さくする光量補正方法であって、前記発光アレイ1本当たりの発光素子の輝度分布Bsの幅に対応して、前記補正範囲Esのレンジを個別設定する。このようにすれば、生産で生じる全輝度ばらつきをカバーできるようにレンジを設定する場合に比べて、補正範囲のレンジが狭くなるので、補正量の飛びが小さくなり、きめの細かな光量補正が可能となる。しかも、補正範囲Esのレンジを輝度分布Bsの幅に対応して個別設定しているので、補正しきれない発光素子の発生がない。

(もっと読む)

画像形成装置

【課題】ディザパターンにできる筋を目立たなくする。

【解決手段】複数の発光チップCHからなる発光アレイ41と、前記発光アレイ41により露光される感光体53に形成される静電潜像を用いて被記録媒体に画像を形成する画像形成部30と、前記発光アレイ41の前記発光素子Pに前記画像の階調を示し一方向に傾斜する規則性をもったドットの集合であるディザパターンを形成させる発光制御装置100、110とを備え、前記発光制御装置100、110は、前記各発光チップ41の発光素子Pが作るドットの集合体が一直線に近づくように前記発光チップ41を構成する発光素子Pの点灯タイミングを発光チップ単位又は発光チップ単位より小さい制御単位で制御する。

(もっと読む)

画像形成装置

【課題】ディザパターンにできる筋を目立たなくする。

【解決手段】主走査方向に並べて配置された複数の発光チップ からなる発光アレイ41と、前記発光アレイ41により露光される感光体53に形成される静電潜像を用いて被記録媒体に画像を形成する画像形成部30と、前記発光チップ同士の継目に位置する2つの発光素子間の距離に応じて前記発光チップの継目における前記発光素子の光量を補正する発光制御装置100、110とを備え、前記発光制御装置100、110は、前記距離と基準値との差が所定値より大きい場合に、前記画像の階調を表すディザパターンの主走査方向に対する角度が所定角度以上となる場合と所定角度未満となる場合で、前記継目における前記発光素子の光量の補正パターンを変更する。

(もっと読む)

31 - 40 / 1,860

[ Back to top ]