国際特許分類[G06F1/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875) | クロック信号の分配 (273)

国際特許分類[G06F1/10]に分類される特許

101 - 110 / 273

クロック分配回路およびそれを用いたインターフェース装置

【課題】データの伝送速度および信頼性の低下を防止できるようにしたクロック分配回路およびそれを用いたインターフェース装置を提供する。

【解決手段】入力されたクロックを制御電圧によって可変とされた遅延を有するようにして分配クロックとして出力する電圧制御分配手段、及び前記データと前記分配クロックの位相差を用いて前記制御電圧を生成する制御電圧生成手段を備える。

(もっと読む)

プロセッサ・コアにおけるアナログ周波数クロッキングのための方法およびシステム

【課題】 プロセッサ・コアにおける周波数クロッキングのための方法およびシステムを提供することにある。

【解決手段】 このシステムでは、少なくとも1つのプロセッサ・コアが提供され、その少なくとも1つのプロセッサ・コアは、可変周波数でアナログ出力クロック信号を生成するためのクロッキング・サブシステムを有する。デジタル周波数制御データおよびアナログ信号はどちらもその少なくとも1つのプロセッサ・コアに伝送され、そのプロセッサ・コアは受信したアナログ信号およびデジタル周波数制御データを使用して、クロッキング・サブシステムの出力クロック信号の周波数を設定する。好ましい一実現例では、複数コアが非同期的にクロックされ、コア周波数が独立して設定される。

(もっと読む)

半導体装置

【課題】半導体制御装置において、供給先別にクロックの位相を制御し、且つクロック供給の供給先別優先順位を制御することによって、動作時の電源電圧変動を抑えこれにより動作時の消費電力を抑える。

【解決手段】機能により複数に分割された機能モジュールと、上記機能モジュールの夫々に供給されるクロック信号を生成するクロック発振回路と、外部から入力される上記機能モジュールの夫々に対するクロック供給イネーブル信号に従って、上記クロック発振回路の生成するクロック信号を上記機能モジュールの夫々に供給するクロック制御回路を含む半導体装置を提供する。

(もっと読む)

同期回路

【課題】広い範囲で遅延調整を可能にしてACタイミングを確保し易くする。

【解決手段】フリップフロップ回路FF1と組合せ論理回路LOGIC1との間にフリップフロップ回路FF1aを挿入し、セレクタMUX1によりいずれか一方のフリップフロップ回路の出力データ信号を選択可能にする。フリップフロップ回路FF1に入力するクロック信号をフリップフロップ回路FF1aに入力するクロック信号よりも遅らせる。

(もっと読む)

タイミング調整回路及びそれを備えた半導体装置

【課題】テスト装置のピン間スキューによる制限を受けること無く、高い精度でタイミングずれを除去することができるタイミング調整回路を提供する。

【解決手段】タイミング調整回路30に、データ入力回路66のレプリカ回路31を設ける。レプリカ回路は、初段回路32とラッチ回路33とを含む。初段回路は、外部クロック信号を受け参照クロック信号を出力する。クロックドライバ64からの内部クロック信号に同期して、参照クロック信号をラッチし、外部出力端子34へ位相進み遅れ信号として出力する。

(もっと読む)

シフタ及び加算器を利用して遅延時間を調節する遅延固定ループ及びクロック遅延方法

【課題】シフタ及び加算器を利用して遅延時間を調節する遅延固定ループを提供する。

【解決手段】第1入力クロックの1クロック周期に対応する第1デジタル値を出力するマスタ遅延固定ループと、第1デジタル値を受信し、第1入力クロックの1クロック周期より短い時間ほど第2入力クロックを遅延させて出力するスレーブ遅延固定ループとがある。該スレーブ遅延固定ループは、シフタ136、演算器138及び可変遅延回路132を備え、該シフタ136は、第1デジタル値をシフトして第2デジタル値として出力し、該演算器138は、第2デジタル値に、工程、電圧及び温度(PVT)によって変化するオフセット値を加算または減算して第3デジタル値として出力し、該可変遅延回路132は、第3デジタル値に対応する時間ほど第2入力クロックを遅延させて出力する。

(もっと読む)

遅延調整回路を有するアレイ型プロセッサ

【課題】各構成のサイクル時間を調整可能とするアレイ型プロセッサの提供。

【解決手段】複数のプロセッサエレメント11がアレイ状に配置されたデータパス部10と、データパスの切り替え制御を行う情報を格納しておく状態遷移管理部12と、前記状態遷移管理部からの情報に基づき、入力されたクロック信号の遅延を調整し、前記データパス部に出力する遅延調整回路13と、を備え、前記遅延調整回路13は、遅延制御情報メモリ14とプログラマブルディレイ15を備え、遅延制御情報メモリは、複数の遅延制御情報を記憶しており、状態遷移管理部からの構成番号をアドレスとして遅延制御情報を読み出し前記遅延制御情報を前記プログラマブルディレイに与え、前記プログラマブルディレイは、入力されたクロック信号を前記遅延制御情報により指定された遅延だけ遅らせてデータパス部に出力する。

(もっと読む)

クロック信号分配回路、情報処理装置及びクロック信号分配方法

【課題】集積回路に供給するクロック信号を分配するためのクロックツリーの構成に関し、最適なクロックツリーを容易に構成し得るクロック分配方法を提供することを目的とする。また、BIST回路を内蔵した評価用のLSIのテストを、短時間で実行できるようにしたクロックツリーのクロック分配方法を提供することを目的とする。

【解決手段】複数のセルに試験パターンを入力するステップと、第1のセルから第2のセルへデータ信号を転送させるステップと、第1のセル及び第2のセルへクロック信号を分配させ、データ信号の転送方向と同方向にクロック信号を転送させるステップと、転送されたクロック信号に基づき、試験パターンを複数のセルに入力し、複数のセルから出力される試験パターンの結果から、複数のセルの故障を検出させるステップとを有する情報処理装置のテスト方法。

(もっと読む)

位相調整機能の評価方法、情報処理装置、プログラム及びコンピュータ読取可能な情報記録媒体

【課題】データ受信回路における位相調整回路の動作検証を効果的に実施し得る構成を提供することを目的とする。:

【解決手段】受信された複数のデータ信号及びクロック信号との間の位相を自動的に調整する位相調整機能を有する位相調整手段と、各位相調整手段に入力される前記クロック信号へ所定の位相量を与える位相量付与手段と、位相量付与手段によって各位相調整手段に与えられる所定の位相量を所定の態様で変化させる付与位相量変化手段と、これに応じて前記各位相調整手段が実施する前記位相調整機能の動作結果を格納手段が記憶手段に格納する格納手段とを設けた。

(もっと読む)

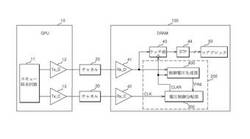

モジュラー・メモリー制御装置のクロック供給アーキテクチャ

【課題】 従来のクロック供給アーキテクチャは、単一のメモリー制御装置チャンネルの全てのデスキューを制御するために、比較的多数のロジック構成要素を実装する。

【解決手段】 ある実施例によると、メモリー制御装置が開示される。メモリー制御装置は、示差基準クロックを生成する位相ロック・ループ(PLL)、及び前記PLLと結合された第1のクロック供給構成要素を有する。第1のクロック供給構成要素は、前記基準クロックを受信し送信及び受信遅延デスキュー・クロック信号を生成する第1の遅延ロック・ループ(DLL)、データ送信デスキューを提供する第1の位相補間器セット、及びデータ受信デスキューを提供する第1のスレーブ遅延線セット、を有する。

(もっと読む)

101 - 110 / 273

[ Back to top ]