国際特許分類[G06F1/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875) | クロック信号の分配 (273)

国際特許分類[G06F1/10]に分類される特許

71 - 80 / 273

信号処理装置および信号処理方法

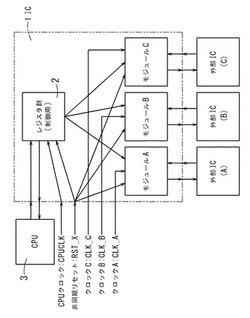

【課題】 相互に異なる周期のクロック信号が与えられ、かつ相互に非同期で所定の処理を行う複数の処理部のリセットを、簡単な構成で、確実に行うことができる信号処理装置および信号処理方法を提供する。

【解決手段】 モジュール回路部14は、モジュールA,B,Cのうちのいずれかに対するリセット指令が与えられると、指令されたモジュールを指定する信号を含み、かつCPUCLKの1周期分の長さを有する1shotリセット信号を生成する。同期リセット生成回路部15は、1shotリセット信号が与えられ、この1shotリセット信号の長さを指令されたモジュールに対応する長さに引き延ばした伸長リセット信号を生成し、生成した伸長リセット信号を指令されたモジュールのクロックに同期させて同期リセット信号を生成し、指定されたモジュールでは、同期リセット信号が与えられた状態で、クロック信号が立上がりまたは立下ると、リセットされる。

(もっと読む)

半導体集積回路

【課題】LSI チップ内に互いに独立した電源を使用する複数の領域が混在する場合、両領域で発生する信号の相対的な遅延差を補償し、信号のタイミングマージンを余計に確保する必要をなくし、チップの面積や消費電力の増大を抑制する。

【解決手段】同一チップ内に互いに独立した電源を使用する複数の領域11,12 が混在するLSI において、複数の領域で発生する信号の相対的な遅延差をチップ内に保持されている設定情報に応じて補償し、複数の領域相互で信号のタイミングを調整する手段13,14 を具備する。

(もっと読む)

半導体集積回路、および半導体集積回路のレイアウト方法

【課題】消費電力及びクロックスキューが小さく、かつ、大規模な半導体集積回路においても、クロック信号を供給するクロック駆動セルの負荷容量が小さいクロック分配回路を提供する。

【解決手段】機能ブロック100の領域10,20にそれぞれ、第1の方向に延びるクロック基幹配線11,21、第2の方向に延びるクロック支線配線群12,22、およびクロック駆動セル13,23が、それぞれ配置されている。領域10のクロック同期セル群14は、クロック基幹配線11またはクロック支線配線群12と接続されている一方、領域20のクロック同期セル群24は、クロック基幹配線21またはクロック支線配線群22と接続されている。クロック基幹配線11,21は、第1の方向においてクロック支線配線群12,22が存在する範囲に限って延びている。

(もっと読む)

半導体集積回路並びにその設計方法及び設計プログラム

【課題】IRDropやEMIの低減等が可能な半導体集積回路の設計方法等を提供する。

【解決手段】この半導体集積回路の設計方法は、複数のリーフセルを複数のグループにグループ分けするステップと、複数のグループの各々に対して、クロック信号の入り口としての代表セルを設けるステップと、複数のグループの各々に対して、代表セルとリーフセルの各々との間のクロック信号の遅延が略同等になるように、代表セル及びリーフセルをグループ配置領域内に配置するステップと、複数のグループをレイアウト領域内に配置するステップと、複数のグループにクロック信号を供給するためのクロックルートセルと複数のグループ内の代表セルとの間にクロックツリーシンセシスを行うステップと、を含む。

(もっと読む)

クロック分配回路、半導体集積回路、およびクロック分配方法

【課題】 関連技術のバス型クロック分配回路は、各分岐配線による反射波形が駆動波形に重なり合い、スイッチング誤りやジッタの要因を内在しており高周波回路に適用するにあたり分配可能な距離やファンアウト数が厳しく制約される。

【解決手段】 入力した、或いは発生したクロック信号を複数段のバッファを通じ順序回路に供給するクロック分配回路であって、複数段の一つ以上について、バッファの出力、或いは発生回路の出力を次段の複数のバッファの入力に一筆書き形状で接続する第1の伝送路(伝送路4)を備え、第1の伝送路が、配線路と、上層メタル配線と下層メタル配線間の接続を鈍角で行うビア群とを有する。

(もっと読む)

クロック分配回路のレイアウト生成方法、および半導体集積回路装置

【課題】再収斂分岐構造を含むクロック分配回路のレイアウト生成において、冗長な迂回配線を生じさせることなく、クロックスキューを低減可能にする。

【解決手段】クロック分配回路の基本セル構成を解析し(S201)、解析された基本セル構成を基にして、クロック経路にクロックバッファを挿入する(S202)。その後、基本セルとクロックバッファとを配置し(S203)、配線を配置する(S105)。解析ステップ(S201)において、クロックの各経路における基本セルの段数の最大値を求め、挿入ステップ(S202)において、クロックの各経路におけるセル段数が、この最大値以上でかつ同じ値になるように、クロックバッファを挿入する。

(もっと読む)

信号処理装置

【課題】0と1の出現確率が異なるデータ信号のデューティサイクルの歪みを補正する。

【解決手段】位相検出回路21は、0と1の出現確率が異なるデータ信号の位相の進みおよび遅れを検出する。AND回路43はデータ信号の立ち上がりを検出し、AND回路44は立ち下がりを検出する。+DCD検出回路45は、位相検出回路21とAND回路43および44の検出結果に基づいて、デューティサイクルのプラス側の歪みを検出し、−DCD検出回路46は、デューティサイクルのマイナス側の歪みを検出する。デューティ調整回路12は、+DCD検出回路45と−DCD検出回路46の検出結果に基づいて、デューティサイクルを調整することにより、デューティサイクルの歪みを補正する。本発明は、例えば、データ信号を受信する受信装置に適用することができる。

(もっと読む)

半導体装置及びデータプロセッサ

【課題】並列動作される複数のメモリデバイスに共通接続するコマンド及びアドレス信号とメモリデバイスに接続するクロック信号との同期化をクロック配線長の増大を極力抑えて実現する。

【解決手段】配線基板に搭載されたデータ処理デバイスとこれによって並列アクセスされる複数個のメモリデバイスとを有する。データ処理デバイスはコマンド及びアドレス端子から第1の周波数でコマンド及びアドレス信号を出力し、前記クロック端子から第2の周波数でクロック信号を出力する。前記第2の周波数は第1の周波数の複数倍とされ、前記コマンド及びアドレス端子から出力されるコマンド及びアドレス信号には前記クロック端子から出力されるクロック信号のサイクル開始位相と同等又はそれよりも早い出力タイミングが選択可能にされる。

(もっと読む)

クロック供給回路

【課題】動作条件が厳しい場合でも、クロックゲーティング信号を含む経路のタイミング違反の発生を防ぐことができるクロック供給回路を提供する。

【解決手段】クロック供給回路1は、クロックツリー13からのクロック信号に基づく信号を複数のインバータ回路32a及び32bによって遅延させ、複数のインバータ回路32a及び32bによる遅延量に基づいてタイミング違反を推定するモニタ回路17を有する。さらに、クロック供給回路1は、モニタ回路17の推定結果に基づいて、組合せ回路16により生成されたクロックゲーティング信号を制御するOR回路18と、OR回路18の出力信号に基づいて、クロック信号を供給又はクロック信号の供給を停止するクロックゲーティング回路12とを有する。

(もっと読む)

半導体集積回路

【課題】雑なクロック選択回路に対応できる半導体集積回路を、簡単な配置クラスタリング工程で作製できるようにする。

【解決手段】クロック信号を種々の遅延量で遅延調整するクロックツリー回路と、遅延調整されたクロック信号が供給されるクロック同期回路とを備える。クロックツリー回路は、クロック信号導入端の後段に設けられた第一のクロックツリーセルと、クロック同期回路の前段でかつ第1のクロックツリーセルより後段に設けられた第二のクロックツリーセルと、第二のクロックツリーセルの前段に設けられたクロック分岐点とを備える。クロック同期回路は第二のクロックツリーセルで遅延調整されたクロック信号が供給される第一のクロック同期回路とクロック分岐点でクロックツリー回路から出力されるクロック信号が供給される第二のクロック同期回路とを備える。

(もっと読む)

71 - 80 / 273

[ Back to top ]