国際特許分類[G06F1/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875) | クロック信号の分配 (273)

国際特許分類[G06F1/10]に分類される特許

81 - 90 / 273

クロック分配回路の設計方法

【課題】消費電力を抑制しつつ、スキューの抑制およびスラックの増大を可能にするクロック分配回路の設計方法を提供する。

【解決手段】クロック分配回路の設計方法は、バッファの位置および配線の位置を設定し、クロック分配回路の共通ノードから第1の回路素子までのクロック伝達時間およびクロック分配回路の共通ノードから第2の回路素子までのクロック伝達時間を計算し、共通ノードから第1の回路素子までの第1の経路と共通ノードから第2の回路素子までの第2の経路との間のいずれかの箇所を短絡する短絡配線を設定することによって、共通ノードから第1の回路素子までのクロック伝達時間のばらつきおよび共通ノードから第2の回路素子までのクロック伝達時間のばらつきだけ、第2の回路素子が受け取るデータと第2の回路素子が受け取るクロックとの間のスラックを改善することを具備する。

(もっと読む)

DLL回路及びこれを用いた半導体装置、並びに、DLL回路の制御方法

【課題】チップ上における占有面積が小さく、広範囲なクロック周波数に対応可能なDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させるディレイライン210と、ディレイライン210による遅延量を制御する制御回路とを備える。ディレイライン210は、従属接続された複数の可変遅延素子500を有し、可変遅延素子500は、バイアス電流量によって遅延量が変化する差動回路構成であり、制御回路は、バイアス電流量を設定する第1の制御部300と、複数の可変遅延素子500のうち出力を取り出す可変遅延素子を選択する第2の制御部400とを有している。本発明によれば、可変遅延素子によってディレイラインが構成されていることから、少ない段数にて広範囲なクロック周波数に対応することが可能となる。

(もっと読む)

半導体集積回路装置及びクロックスキュー計測方法

【課題】クロックスキューをより正確に計測できる半導体集積回路装置及びクロックスキュー計測方法を提供する。

【解決手段】LSI100内部のクロック信号を入力するクロック入力端子1と、クロックスキューを計測するためのクロックスキュー計測信号を入力する計測信号入力端子2と、クロック信号とクロックスキュー計測信号とが入力される複数のF/F3と、計測信号入力端子2から複数のF/F3にクロックスキュー計測信号を分配する複数の計測信号分配ドライバ7と、を備え、複数のF/F3は、複数のF/F群5に分けられ、F/F群5内の全てのF/F3は、同一の計測信号分配ドライバ7と直接に信号線のみを介して接続され、複数のF/F3の出力信号に基づいて、複数のF/F3間におけるクロックスキューを計測するように構成した。

(もっと読む)

分周回路及び分周方法

【課題】複数段の1/2分周器により分周された各信号において、全ての分周信号同士が同期し、かつクロック信号の同一のエッジに同期した分周信号を出力することが可能な分周回路及び分周方法を提供する。

【解決手段】第1の同期回路群は、分周器群と第1の同期回路群との間に設けられ、分周器群からの各分周信号を入力とし、その出力が第1の同期回路群のラッチ回路の各入力端子に接続されたN段のラッチ回路からなり、第1段目から第M段目のラッチ回路のクロック入力端子にはクロック信号が入力され、クロック信号に同期した信号を出力し、第(M+1)段目から第N段目までのラッチ回路のクロック入力端子には第M段目のラッチ回路の出力信号が入力され、M段目のラッチ回路の出力に同期した信号を出力する第2の同期回路群を有する。

(もっと読む)

クロック配線処理装置、クロック配線処理方法、及びプログラム

【課題】 パス始点F/F終点F/F間の遅延を最小化する、最終段クロックドライバから始終点F/Fへクロック信号クロックを配線する。

【解決手段】 始終点F/Fリストを記憶部に抽出し、始終点F/Fへ接続する最終段クロックドライバ候補を選択して記憶部に格納する始終点F/F処理部と、始点F/F終点F/Fへ接続する最終段クロックドライバ候補の組み合わせから、最終段クロックドライバ間クロックスキューが最小になる始終点F/Fに接続する最終段クロックドライバを選択して記憶部に格納するクロックスキュー処理部と、を備えることを特徴とする。

(もっと読む)

メソシンクロナス・データ・バス装置及びデータ伝送方法

メモリ・システムにおける指定されたポイント間の全体の時間遅延が一定に維持されるように、メモリ・モジュール間のデータの伝送時間が管理される、メモリ・システムについて説明される。多数のレーンのバスの各レーンを別個に管理することができ、中間モジュールにおいてスキュー除去する必要なしに、宛先モジュールにおいてデータフレームを評価することができる。バス・シリアル・データ速度の1つ又それ以上の約数でモジュールを通してデータ経路を作動させ、受信されたデータのサンプリング・ポイントを選択し、温度変化又は時間経過に起因する時間遅延の変動を調整することによって、データを経路指定するためのスイッチを有するモジュールを通したデータの伝播における時間遅延が低減される。 (もっと読む)

半導体装置

【課題】 半導体装置におけるクロックスキューを低減する。

【解決手段】 第1のサブクロックツリー802と、第2のサブクロックツリー803とを有し、それぞれのサブクロックツリーにおける相対位置の等しい末端クロックドライバの出力クロックの位相が一致するように、可変遅延素子805で遅延させたクロックを第2のサブクロックツリー803に入力する。

(もっと読む)

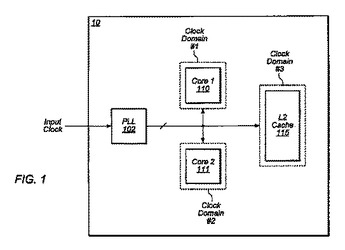

クロックサイクルスチールのための方法および装置

複数のクロック信号を生成するための方法。前記方法は、位相ロックループ(PLL)を使用して基準クロック信号を生成するステップを有する。前記基準クロックが、複数のクロック分周器ユニットのそれぞれに供給され、前記複数のクロック分周器ユニットのそれぞれが、前記受信基準クロック信号を分周して、対応する分周クロック信号を生成する。前記方法は、前記対応する受信分周クロック信号の周波数と、除去するサイクル数とに基づいて、それぞれが有効周波数を有する複数のドメインクロック信号を生成するために、(所定の数のサイクルにつき)1以上のクロックサイクルを除去する。  (もっと読む)

(もっと読む)

遅延パルス発生回路

【課題】クロックパルスを用いずに入力パルスを遅延させた出力パルスを生成する。

【解決手段】外部からの入力パルス信号に応じて動作を開始し、その動作の開始から第1の遅延時間T1後に出力信号を変化させる第1の遅延回路102と、その出力信号に応じて、動作の開始から第1の遅延時間T1後に動作を開始し、その動作の開始から第2の遅延時間T2後に出力信号を変化させる第2の遅延回路104と、を備え、その出力信号の変化に応じて入力パルス信号を遅延させた出力パルス信号を生成する。

(もっと読む)

通信システム

【課題】マスタの第1のデバイスからスレーブの第2のデバイスに確実且つ容易にアクセスすることである。

【解決手段】バスコントローラFPGA1と、バスコントローラFPGA1と通信接続され、ライトクロック信号WCLKが一線路で順に伝送される複数のローカルFPGA21〜24と、を備え、バスコントローラFPGA1からのライトクロック信号WCLKの線路が最も長いローカルFPGA24は、リードクロック信号RCLKを出力して他のローカルFPGA23〜21を一線路で順に介してバスコントローラFPGA1に伝送し、各ローカルFPGA21〜24は、リードクロック信号RCLKに同期して入力信号を出力してバスコントローラFPGA1へ伝送し、各ローカルFPGA21〜24及びバスコントローラFPGA1の間のリードクロック信号RCLKの線路長と、前記入力信号の線路長とが等しい。

(もっと読む)

81 - 90 / 273

[ Back to top ]