国際特許分類[G06F1/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875) | クロック信号の分配 (273)

国際特許分類[G06F1/10]に分類される特許

41 - 50 / 273

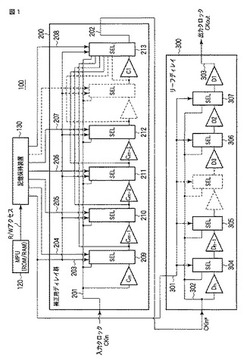

クロック生成装置、クロック生成方法およびデジタル放送受信装置

【課題】延回路を用いて低ジッタの周波数可変クロック生成システムを実現する。

【解決手段】クロック生成装置100は、CKinを遅延してCKoutを提供する遅延回路200,300と、稼動主遅延段選択部と、稼動補正遅延段選択部と、遅延制御部を具備する。遅延回路は、選択的に動作する複数の主遅延段D1〜Dnが縦続接続された主遅延部300および、この主遅延部に接続され選択的に動作する複数の補正遅延段C1〜Cmが縦続接続された補正遅延部(補正用ディレイ200)を含む。稼動主遅延段選択部は、主遅延段のうち遅延動作に用いられる稼動主遅延段を選択する。稼動補正遅延段選択部は、補正遅延段のうち遅延動作に用いられる稼動補正遅延段を選択する。遅延制御部(MPU120)は、稼動主遅延段を選択することでCKinに対するCKoutの遅延量を定め、稼動主遅延段の遅延値が均一化するように稼動補正遅延段を決定する。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

クロック分配素子及びそれを用いたレイアウト設計方法

【課題】簡易かつ精度良くデューティ比を調整することができるクロック分配素子及びレイアウト設計方法を提供すること。

【解決手段】本発明に係るレイアウト設計方法は、クロックツリー回路のレイアウト設計方法であって、クロックツリー回路上に第1のクロック分配素子を配置し、前記第1のクロック分配素子が配置された前記クロックツリー回路に配線し、配線された前記クロックツリー回路についてタイミング検証し、前記タイミング検証の結果に基づいて、前記第1のクロック分配素子を、当該第1のクロック分配素子と入力負荷容量が略等しく遅延値が異なる前記第2のクロック分配素子へ置換するものである。

(もっと読む)

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

デスキュー回路およびデスキュー方法

【課題】デスキュー後のデータの遅延時間を一定範囲に保ち、また、消費電力を低減することができるデスキュー回路を得ること。

【解決手段】データ信号にチェックコードを付加してパラレル信号に変換する伝送データ送信処理回路1と、パラレル信号に対してそれぞれ遅延時間を付加する遅延回路2−1〜2−nと、遅延付加信号のチェックコードに基づいて受信品質を求める伝送データ受信処理回路3と、受信品質に基づいて、パラレル信号ごとの付加すべき遅延時間の最適値を求め、また、付加できる遅延時間の最大値または最小値が、設定遅延時間の最大値または最小値となるよう各最適値に一定の値を一括して加算または減算を行って設定遅延時間を求め、パラレル信号ごとの設定遅延時間を遅延回路2−1〜2−nへ指示する遅延時間最適化制御回路4と、を備える。

(もっと読む)

チャネルに対するクロック分配技法

回路は、第一の領域、第二の領域、および第三の領域を含む。第二の領域は、クロック信号を生成する同期ループ回路を含む。同期ループ回路は、第一の領域において生成されたノイズから隔離された供給電圧を受け取る。第三の領域は、複数のチャネルのカッドと、第二の領域において生成された少なくとも1つのクロック信号をカッドのそれぞれのチャネルにルーティングするために結合されたクロックラインとを含む。第三の領域は、回路において第二の領域から分離している。  (もっと読む)

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の階層レイアウト設計において、タイミング収束を容易化すること。

【解決手段】第1ブロックは、第1クロック端子と第1フリップフロップを有し、第2ブロックは、第2クロック端子と第2フリップフロップを有する。クロック分配経路は、クロック分岐点から、第1クロック端子を通して第1フリップフロップへつながり、且つ、第2クロック端子を通して第2フリップフロップへつながる。データ経路は、第1フリップフロップのデータ出力端子から第2フリップフロップのデータ入力端子へつながる。本発明に係る設計方法は、(A)製造ばらつきに起因するクロック分配経路におけるクロック信号の遅延変動を反映させながら、データ経路のスラックを算出するステップと、(B)算出されるスラックが増加するように、クロック分岐点、第1クロック端子及び第2クロック端子の位置を変更するステップ、とを含む。

(もっと読む)

LSIの電力低減のための適応的クロック位相制御方法および装置

【課題】消費電力を低減する。

【解決手段】クロック信号をデジタル回路に分配する方法、装置は、クロック信号を生成するステップと、制御信号に応じて、クロック信号の位相を遅延され、進められ、あるいはそのままとして、出力クロック信号を生成するステップと、を備える。クロック信号と出力クロック信号の間の遅延量あるいは進み量である位相差を、デジタル回路の電源電圧の大きさの時間的変動に応じて変化させる。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】インピーダンス整合のためのコストを増大させずに高周波クロック信号の伝送効率を高める。

【解決手段】一実施形態に係るクロック供給装置は、クロック信号を生成するクロックジェネレータ21に接続される第1伝送線路T1と、このクロックジェネレータ21の出力インピーダンスとは異なる入力インピーダンスを持つクロック供給先12Aに接続される第2伝送線路T2と、第1および第2伝送線路T1,T2を容量結合するキャパシタCP1と、第1伝送線路T1上でクロック信号の反射を抑制するプルアップ抵抗RP1と、分圧で得られる電位をクロック信号の基準電位として第2伝送線路T2に印加する一対の分圧抵抗RP3,RP2とを備える。一対の分圧抵抗RP3,RP2は第2伝送線路T2上のインピーダンスをクロック供給先12Aの入力インピーダンスに整合させる抵抗比に設定される。

(もっと読む)

41 - 50 / 273

[ Back to top ]