国際特許分類[G06F1/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875) | クロック信号の分配 (273)

国際特許分類[G06F1/10]に分類される特許

21 - 30 / 273

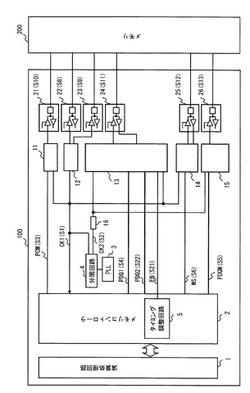

半導体集積回路及びそのタイミング調整方法

【課題】従来技術の半導体集積回路では、タイミング調整に工数がかかるという問題があった。

【解決手段】本発明にかかる半導体集積回路は、外部メモリと接続される複数の信号線に対応して個別に設けられ前記対応する信号線のタイミングを決定する回路ブロックをマクロ化した論理セル群11〜15と、論理セル群11〜15のそれぞれに対応して設けられたIOバッファ21〜26と、を有する。そして、論理セル群11〜15と対応するIOバッファ21〜26とを結合する配線のそれぞれが略同じ長さを有することを特徴とする。

(もっと読む)

クロックツリー形成システム、クロックツリー形成方法及びプログラム

【課題】タイミング収束のイタレーションを削減する。

【解決手段】半導体集積回路600のクロックツリー700Aが、分周器752が追加されたクロックツリー700Bで置換されない場合について、モジュール761及び762に関するホールドエラー値HEV1を算出する(S105)。クロックツリー700Aがクロックツリー700Bで置換された場合について、モジュール761及び762に関するホールドエラー値HEV2を算出する(S107)。ホールドエラー値HEV1及びHEV2に基づいて、クロックツリー700Aをクロックツリー700Bで置換することで半導体集積回路600のホールドエラーが削減されるか判定する(S108)。半導体集積回路600のホールドエラーが削減されると判定された場合、クロックツリー700Aがクロックツリー700Bで置換された半導体集積回路600を記述する回路データを生成する(S109)。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリー設計において、簡潔なスキュー調整をすることができるレイアウト装置及びレイアウト方法を提供すること。

【解決手段】本発明にかかるレイアウト装置1は、想定スキュー値記憶部141、遅延挿入部133、遅延調整部134を備える。想定スキュー値記憶部141は、クロックツリーの段数に応じて予め定められた想定スキュー値を格納する。遅延挿入部133は、想定スキュー値が要求スキュー値以下である場合、当該クロックツリーの最上位側に遅延調整バッファ206を挿入する。遅延調整部134は、クロックツリーのスキュー値が要求スキュー値以下となるように、クロックツリーの配線後に、遅延調整バッファ206の遅延を調整する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

クロックツリー合成装置、クロックツリー合成方法及びプログラム

【課題】半導体集積回路のCTSにおいて、クロック遅延時間を削減すること。

【解決手段】CTS装置は、クロックドメインに接続された複数のフリップフロップの重心座標を求め、求めた重心座標と各フリップフロップとの距離を算出し、重心座標から遠いフリップフロップから順に、重心座標からのクロックラインにおける遅延時間をクロック遅延時間として算出し、前段のフリップフロップとの距離を求め、求めた距離からデータパスにおける遅延時間をデータ遅延時間として算出し、クロック遅延時間とデータ遅延時間との和がクロックドメインのクロックの1周期よりも長いフリップフロップを選択し、選択されたフリップフロップと前段のフリップフロップとのデータパスがフォルスであると判定された場合には、選択されたフリップフロップをスキュー調整の対象外としてクロックツリーを合成する。

(もっと読む)

クロック送受信回路

【課題】

クロック配線からのクロストークを抑制できるクロック送受信回路を提供する。

【解決手段】

クロックを送信し送信した前記クロックを受信するクロック送受信回路において,入力クロックを入力し擬似乱数ビット列に基づく第1のクロックを生成する擬似乱数ビット列生成ユニットと,第1のクロックと入力クロックとを入力し排他的論理演算を行い第2のクロックを生成する送信側排他的論理演算器とを有する送信ユニットと,送信ユニットが生成する前記第1,第2のクロックを伝播する第1,第2のクロック配線と,第1,第2のクロック配線を伝播してきた第1,第2のクロックを入力し排他的論理演算を行い出力クロックを生成する受信側排他的論理演算器を有する受信ユニットとを有する。

(もっと読む)

半導体集積回路の設計方法、設計装置およびプログラム

【課題】製造バラつきの下で、クロックスキューの最小化しつつ、クロック信号部での消費電力を最小化する半導体集積回路の設計方法、設計装置および、コンピュータプログラムを提供する。

【解決手段】メッシュ配線構造を駆動するバッファツリーを生成するグローバルクロック構造生成部104と、クロック素子の配置分布とクロックゲーティング構造を考慮してクラスタを生成するクロック素子クラスタ生成部106と、そのクラスタに含まれるクロック素子が属するゲーティッド回路にクロック信号を分配するゲーティングセルを複製して、クラスタを駆動するゲーティングセルとして挿入するゲーティングセル複製・挿入部107と、ローカルクロック構造生成部109と、タイミング解析結果に基づき、クロック素子クラスタを駆動するゲーティングセルの駆動能力を調整するゲーティングセル駆動能力調整部111と、を備える。

(もっと読む)

半導体集積回路のレイアウト装置及びクロックゲーティング方法

【課題】スイッチング時におけるセルによる消費電力を削減することができる半導体集積回路のレイアウト装置及びクロックゲーティング方法を提供すること。

【解決手段】本発明にかかるレイアウト装置51は、イネーブル信号生成処理部55と、クロックゲーティング回路追加処理部56とを備えている。イネーブル信号生成処理部55は、第1の分岐点よりも後段に位置する第1のクロックゲーティング回路に入力される第1の制御信号と、第1の分岐点よりも後段に位置する同期回路の位置とに基づいて、第2のクロックゲーティング回路に入力する第2の制御信号を生成する。クロックゲーティング回路追加処理部56は、第2の制御信号と、第2のクロックゲーティング回路よりも後段に位置する回路素子数と、に基づいて、第2のクロックゲーティング回路を配置する。

(もっと読む)

動的バスクロックを制御するための装置及び方法

【課題】本発明は動的バスクロックを制御するための装置及び方法に関する。

【解決手段】本発明による動作バスクロックを制御するための装置は、少なくとも一つのマスターモジュールと、少なくとも一つのスレーブモジュールと、前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュールが送受信するデータを媒介するバスと、前記少なくとも一つのマスターモジュールの動作情報(Activity)を考慮してバスクロックの周波数を決定するバス周波数制御機と、前記バス周波数制御機で決定した周波数を発生させて生成したクロックを前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュール及び前記バスに提供するクロック発生器と、を含む。

(もっと読む)

電子機器

【課題】 デジタル回路間におけるクロックスキューを調整することができる電子機器を安価に提供することを目的とする。

【解決手段】 第1クロック信号CK1を遅延させて第2クロック信号を生成する位相調整回路12と、第1クロック信号CK1に同期して動作する制御回路15と、第2クロック信号CK2に同期して動作し、制御回路15との間でデータ入出力を行う制御回路25と、制御回路15,25間の同期を判定する同期判定部153と、この判定結果に基づいて第2クロック信号CK2の遅延量を決定する遅延量制御部141とを備えている。位相調整回路12は、第1クロック信号CK1を遅延させるゲート回路120と、上記遅延量に基づく電源電圧をゲート回路120に供給する電源供給回路121とを備え、ゲート回路120の電源電圧を変化させることにより、制御回路15,25間のクロックスキューを抑制する。

(もっと読む)

21 - 30 / 273

[ Back to top ]