国際特許分類[G06F12/04]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 可変長語,または語の一部,のアドレシング (194)

国際特許分類[G06F12/04]に分類される特許

31 - 40 / 194

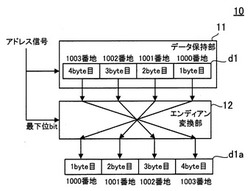

エンディアン変換回路、エンディアン変換方法及びマイクロコントローラ

【課題】効率よくエンディアン変換が可能なエンディアン変換回路を提供する。

【解決手段】アドレス信号の最下位ビットをドントケアビットとして番地指令が行われるデータ保持部11と、エンディアン変換部12を有し、エンディアン変換部12は、データ保持部11へアクセスするアドレス信号の最下位ビットの値に基づいて、データ保持部11への書き込みデータ、またはデータ保持部11からの読み出しデータd1に対してエンディアン変換を行う。

(もっと読む)

メモリコントローラ

【課題】動画像のデコード・エンコード処理または三次元グラフィックス描画処理で使用されるのに適した機能を有するメモリコントローラを提供する。

【解決手段】入力された画像データは、圧縮処理される。圧縮処理の結果、データ量が少なくなった場合には、圧縮データを、少なくならなかった場合には、非圧縮のデータをメモリに格納する。データが圧縮されなかったとした場合にデータを所定サイズで分割して格納する領域ブロックをメモリ内に設け、圧縮された場合、されなかった場合のいずれの場合にも、データを領域ブロックの先頭アドレスから格納する。データの格納先頭アドレスと、データ量および、データが圧縮データか非圧縮データかを示す情報は、マップ情報として、別途格納しておく。

(もっと読む)

データ転送装置およびデータ転送方法

【課題】 入出力データの幅の異なる2つの機能ブロックの通信を可能にする。

【解決手段】 第1周期の第1クロック、第1周期の2倍の第2周期の第2クロックが生成される。第2クロックのハイ、ローの期間の各後半の間のみそれぞれハイを維持する第3、第4クロックが生成される。第1バッファ12は、第1ビット幅でデータを出力する。第1ラッチ71は、第1バッファから第1ビット幅でデータを受け取り、第2周期の第2クロックに合わせて第1ビット幅でデータを出力する。第2ラッチ72は、第1ビット幅で第1ラッチからデータを受け取り、保持している第1データの前半部を第3クロックの立ち上がり時に第1ビット幅の半分の第2ビット幅のデータを出力し、第1データの後半部を第4クロックの立ち上がり時に出力する。第2バッファ21は、第2ビット幅のデータを第2ラッチから受け取る。

(もっと読む)

半導体装置

【課題】ランレングス圧縮変換を適用して、データが劣化することなく、且つ原データよりも圧縮変換後のデータ長が長くなることを抑制する。

【解決手段】メモリアクセスに応答して外部メモリ(3)に対する書き込みおよび読み出しを制御するメモリインタフェースコントローラ(20)を備えた半導体装置(1)であって、外部メモリにデータを書き込むときには、入力された書き込みデータのランレングス圧縮変換を行って、変換後のデータのデータ長と変換前のデータのデータ長を比較し、データ長が短い方のデータを、メモリに出力する書き込みデータとして生成し、外部メモリからデータを読み出したときには、当該データが、ランレングス圧縮変換済みのデータであれば、伸張処理を行う。

(もっと読む)

データ転送回路

【構成】F/F回路22〜36および分配器38〜52は、入力端子20によって取り込まれたデータA〜Pのうち先行する8ワードのデータA〜Hの各々を16ビットの部分データA1〜H2に分割する。一方、SRAM54は、入力端子20によって取り込まれたデータA〜Pのうち後続する8ワードのデータI〜Pを一時的に保持する。分配器58は、SRAM54から読み出された8ワードのデータI〜Pの各々を16ビットの部分データI1〜P2に分割する。セレクタ78は、こうして生成された部分データA1〜P2を時分割態様でSDRAMに向けて出力する。

【効果】回路規模を抑えつつ、入力データのビット幅よりも小さいビット幅を有するSDRAMに対して入力データを転送することができる。

(もっと読む)

データ格納方法及びデータ格納装置

【課題】圧縮データのブロック単位でのランダムアクセスを可能にし、圧縮率を低く抑えながら、エラーを小さくすることができるデータ格納方法を提供する。

【解決手段】データ格納方法は、ブロックデータを圧縮した圧縮ブロックデータを取得し、圧縮ブロックデータの圧縮ブロックサイズが期待圧縮ブロックサイズを超えているか否かを判定する。判定の結果、期待圧縮ブロックサイズを超えていないと判定された場合、期待圧縮ブロックサイズを超えていないことを示すフラグ情報と、圧縮ブロックデータとを圧縮ブロックに格納し、期待圧縮ブロックサイズを超えていると判定された場合、期待圧縮ブロックサイズを超えていることを示すフラグ情報と、期待圧縮ブロックサイズを超えた圧縮ブロックデータを格納するための圧縮ブロックの場所を指定するポインタ情報と、圧縮ブロックデータとを圧縮ブロックに格納する。

(もっと読む)

コンピュータシステム

【課題】圧縮されたプログラムを保存する記憶部に依存しない汎用性のある解凍装置を実現する。

【解決手段】プロセッサ1と、圧縮されたプログラムを保存する記憶部2とを接続するバス12,13中に、解凍装置15が設けられる。記憶部2に、プログラムの圧縮に関する圧縮情報が保存される。解凍装置15は、記憶部2から圧縮情報を収集する。解凍装置15は、圧縮されたプログラムのアドレス情報に基づいて、周辺バス13を流れるアドレス信号を検出し、解凍が必要なプログラムのデータが周辺バス13を流れているかを判断する。解凍装置15は、圧縮されたプログラムであると判断すると、データを解凍して、解凍したデータをプロセッサバス12を通じてプロセッサ1に送る。

(もっと読む)

インターフェース回路、メモリシステム、およびアクセス制御方法

【課題】リフレッシュが必要な記憶装置の同一ブロックに対して連続アクセスを行う際、リフレッシュ動作の実行タイミングを考慮する必要のない、インターフェース回路、メモリシステム、およびアクセス制御方法を提供すること。

【解決手段】アクセスの制御単位であるブロックを複数備える記憶装置に対してアクセスする際、外部からのバーストアクセスの指令を複数のコマンドサイクルに分割して記憶装置に対してコマンドが発行される。この場合、外部ブロックアドレスを、少なくとも1つのコマンドサイクルを除く第1のコマンドサイクルで論理シフトして記憶装置に供給する。第1のコマンドサイクルでは、バーストアクセスの指令により指定されたブロックとは異なるブロックが選択される。第1のコマンドサイクル以外のコマンドサイクルでは、ブロックを指定するアドレスとしてバーストアクセスの指令により指定されたブロックが選択される。

(もっと読む)

マイクロプロセッサ

【課題】面積オーバヘッドや消費電力を低く抑えたマイクロプロセッサを提供する。

【解決手段】本発明は、データ配列単位での順次処理が可能なマイクロプロセッサであって、フェッチされた命令がデータのロード命令である場合に、指定されたデータを含んだデータ列をメモリ幅単位でデータメモリ16からロードし、また、命令の解析結果に基づいて、ロードしたデータ列のうち、次回のロード命令で指定される予定のデータを特定するロードストアユニット14と、ロードストアユニット14により特定されたデータを記憶するデータ一時記憶部17と、を備える。

(もっと読む)

半導体集積回路、データ処理方法、画像形成装置

【課題】シングルポートの記憶装置を用いて非同期の連続書き込み及び連続読み出しを行うことが可能な半導体集積回路、データ処理方法、画像形成装置を提供する。

【解決手段】シングルポート記憶装置を用いてFIFO動作を行う半導体集積回路120であって、書き込み用クロック信号と同期して書き込まれたデータを保持するバッファ回路121と、前記書き込み用クロック信号と、前記書き込み用クロック信号と独立して予め設定された読み出し用クロック信号との非同期を吸収する非同期吸収回路122と、前記データを前記読み出し用クロックと同期して前記シングルポート記憶装置へ出力する制御回路と、を有し、前記読み出し用クロック信号に基づき、前記シングルポート記憶装置のワードサイズと、前記書き込み用クロック信号の周波数の範囲とが設定される。

(もっと読む)

31 - 40 / 194

[ Back to top ]