国際特許分類[G06F7/58]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915) | 乱数または擬似乱数発生器 (209)

国際特許分類[G06F7/58]に分類される特許

11 - 20 / 209

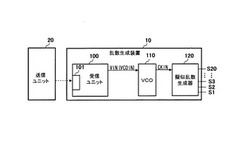

乱数生成装置および乱数生成方法

【課題】 簡単な構成で不規則性の高い乱数を生成することができる乱数生成装置および乱数生成方法を提供する。

【解決手段】 送信ユニット20から送られるエネルギーを非接触で受信する受信機構101を有し、当該受信機構101で受信したエネルギーを受信電圧VINに変換する受信ユニット100と、受信電圧VINに基づいて、発振する出力信号CKINを出力する電圧制御発振器110と、電圧制御発振器110の出力信号CKINの発振周波数に応じて変動する擬似乱数を生成する擬似乱数生成器120とを備えている。

(もっと読む)

乱数発生回路及び半導体記憶装置

【課題】回路規模を縮小しながら、十分に高いランダマイズ性能を確保すると共に、ランダマイズ解除処理に要する時間を短縮する。

【解決手段】実施形態の半数発生回路は、ソフトウェア処理によってシード値を発生するシード値発生処理部と、前記シード値が与えられてハードウェア処理によって乱数を発生する乱数発生部とを具備する。

(もっと読む)

乱数シード選別装置、乱数シードの選別方法、及び乱数シードの選別プログラム

【課題】モンテカルロ計算の収束性が良い擬似乱数列を、多くの乱数列の中から選別するシード選別装置、シード選別方法、シード選別プログラムを提供する。

【解決手段】コンピュータにより、擬似乱数を生成する際のシード(種)を選別する乱数シード選別装置、乱数シード選別方法、乱数シード選別プログラムにおいて、モンテカルロ計算の収束性が良い擬似乱数列を、多くの乱数列の中から選別する選別部を有し、当該収束性の良い擬似乱数列をシード(種)により識別する。

(もっと読む)

一様独立乱数生成方法II

【課題】十分な長周期と高精度を持ち、生成巡回列が−1に合同なすうを含まず全周期使用可能であり、かつ検定による性能保障を伴う一様独立乱数列のより広く新しい生成方法。

【解決手段】

奇素数p1とp2をq1=(p1−1)/2およびq2=(p2−1)/2が互いに素で異なる偶奇性を持つように取り、法p1でのすべての原始根を掃過する6次スペクトル検定での最良の原始根z1、および法p2での同様のスペクトル検定での最良の原始根z2を選ぶ。連立合同式として番号第4669979号特許とは異なりz≡−z1 mod(p1)、Z≡z2 mod(p2)に相当するものを採用し、中国剰余定理が定めるzを乗数として、合成数の法d=p1×p2の単独スペクトル検定を望む次数L(3≦L≦6)まで行い、合格ならば法d、乗数z、周期T=2q1q2の乗算合同法を、L次スペクトル検定の性能保証と共に得る。

(もっと読む)

データランダム選択装置

【課題】軽便性と携帯性を有し、且つ単一装置で複数種類の選択モードを実施できるデータランダム選択装置を提供する。

【解決手段】データ生成モジュール及びデータ読込モジュールを含むデータランダム選択装置である。データ生成モジュールは、無線周波数識別タグ及び複数の指示ユニットを含む。無線周波数識別タグは、識別コードを記憶・送信し、前記複数の指示ユニットの1つは、上記無線周波数識別タグが上記識別コードを送信する場合に、ランダムで駆動されて指示信号を生成する。データ読込モジュールは、無線周波数読込器及び出力ユニットを含み、その内、無線周波数読込器は識別コードを受信し、ランダムで駆動された上記指示ユニットに対応する指示データを読み込み、出力ユニットは識別コード及び指示データを出力する。

(もっと読む)

ゆらぎ増幅装置及び真性乱数生成器

【課題】真性乱数生成器の実装面積あたりのスループットを悪化させずに、生成される乱数品質を向上させることが可能な、オシレータのゆらぎ増幅装置を提供する。

【解決手段】本発明に係る、2つの入力信号間の時間の変動であるゆらぎを増幅するゆらぎ増幅装置100は、2つの入力信号が入力され、2つの入力信号とは異なる外部信号である制御信号によって定まる第1の遅延時間だけ2つの入力信号の各々を遅延させて出力する可変バッファ101と、可変バッファ101へ制御信号を出力することで、第1の遅延時間を制御する遅延制御部102とを備える。

(もっと読む)

かんたん脳トレ

【課題】現在さまざまな能力開発方法があるが、単純な計算の繰り返しによるものも効果的であることが知られている。ところが単調な繰り返しのため、さらに効果を高めることが困難であり、よりシンプルで円滑に計算し易いことが能力開発の効果に影響を与える課題となっている。

【解決手段】エクセルマクロで2桁の乱数表を更新し、足し算、掛け算、割り算をインターバルに配分することで、よりシンプルにバランスよくメンタル能力開発の効果を向上させることができる。

(もっと読む)

擬似乱数生成装置、擬似乱数生成方法及びそのプログラム

【課題】離散的配列データから強度設定可能な擬似乱数を生成する擬似乱数生成装置、擬似乱数生成方法及びそのプログラムを提供する。

【解決手段】離散的配列データのうちの一部をライブラリ用配列データとし、他の部分を乱数判定用データとして、それぞれの要素に対して、所定ビットの数列を割り当てることにより数値列に変換し、ライブラリ用配列データ数列及び乱数判定用データ数列を生成する塩基配列データ数列変換部102と、前記ライブラリ用配列データ数列を用いて、決定論的非線形予測に基づいて予測データを生成する非線形時系列解析部103と、前記予測データと前記乱数判定用データ数列の比較を行い、非ランダムな状態が所定回数連続したとき、前記離散的配列データ全体に対してランダム性が失われたとして評価し、それ以外は、当該乱数判定用データ数列を擬似乱数列の候補として順次外部に送出する乱数生成部105とを備える。

(もっと読む)

乱数生成回路

【課題】回路動作開始直後の初回サンプリングにおいてもランダム性の高い真性乱数を生成することのできる乱数生成回路を提供する。

【解決手段】奇数段の論理ゲートで構成されたM1個の第1のリングオシレータ10−1と、偶数段のインバータと1段の論理ゲートで構成されたM2個の第2のリングオシレータ10−2と、第1のリングオシレータ10−1の中間ノード出力と第2のリングオシレータ10−2の中間ノード出力の排他的論理和をとる(M1+M2)入力XOR21と、出力をサンプリングクロックでラッチし、乱数値として出力するD−FF22と、サンプリングクロックを生成する制御部100とを備え、第1のリングオシレータ10−1を構成する各論理ゲートの出力にそれぞれインバータが接続され、インバータのいずれか1つの出力をリングオシレータの中間ノード出力とする。

(もっと読む)

乱数発生器及び、乱数発生方法

【課題】入力にノイズ源を必要とせず乱数を生成可能な乱数発生器及び、乱数発生方法を提供することにある。

【解決手段】デジタル値を変換して第1の電圧を出力するデジタルアナログ変換回路と、第1の電圧と、定電圧である第2の電圧とを比較し、第1の電圧が第2の電圧より小さい場合に第1の値を、第1の電圧が第2の電圧より大きい場合に第2の値を乱数値として出力する比較回路と、通常動作時に、比較回路が乱数値を複数回出力する度に、当該複数回分の乱数値の多数決が第1の値の場合は第1の電圧が大きくなるように、第2の値の場合は第1の電圧が小さくなるようにデジタル値を制御して、デジタルアナログ変換回路に出力する制御回路とを有する。

(もっと読む)

11 - 20 / 209

[ Back to top ]