国際特許分類[G11C13/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 11/00,23/00,または25/00に包含されない記憶素子の使用によって特徴づけられたデジタル記憶装置 (1,014)

国際特許分類[G11C13/00]の下位に属する分類

化学変化に基づく素子を用いるもの (16)

光学的素子を用いるもの (45)

国際特許分類[G11C13/00]に分類される特許

101 - 110 / 953

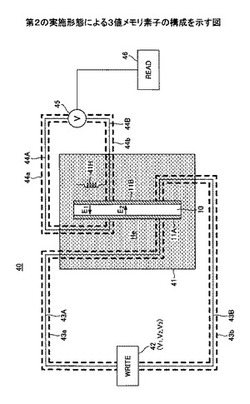

メモリ素子および温度センサ

【課題】カリウムあるいはナトリウムを陽イオンとして含み、OH基を陰イオンとして含むイオン結晶を使った多値メモリ素子を提供する。

【解決手段】メモリ素子40は、カリウムあるいはナトリウムを陽イオンとして含み、OH基を陰イオンとして含むイオン結晶10と、第1および第2の電極11A,11Bと、秩序配列が誘起される転移温度以下の温度に保持するクライオスタット41と、電極の間に直流電圧を印加し、OH基の分極方向が第1の電極11Aから第2の電極11Bに向かう第1の状態と、OH基の分極方向が第2の電極11Bから第1の電極11Aに向かう第2の状態と、最近接OH基の分極が反平行となる第3の状態のいずれかに設定し、第1〜第3の状態に対応して第1〜第3の情報をイオン結晶に書き込む書込回路42と、イオン結晶の分極を測定することにより、書き込まれた第1〜第3の情報のいずれかを読み出す読み出し回路46と、を含む。

(もっと読む)

不揮発性抵抗変化素子

【課題】不揮発性抵抗変化素子の多値化を実現する。

【解決手段】金属元素を有する第1電極11と、半導体元素を有する第2電極13と、金属元素を有する第3電極15と、第1電極11と第2電極13との間に配置され、第1電極11の金属元素が出入りすることで可逆的に抵抗変化が可能な第1抵抗変化層12と、第2電極13と第3電極15との間に配置され、第3電極15の金属元素が出入りすることで可逆的に抵抗変化が可能な第2抵抗変化層14とを設ける。

(もっと読む)

記憶装置およびその動作方法

【課題】ベリファイ動作の高速化を図りつつベリファイ精度を向上させることが可能な記憶装置およびその動作方法を提供する。

【解決手段】記憶装置1は、複数の記憶素子21と、抵抗変化動作(セット動作またはリセット動作)と読み出し動作とを行う駆動部とを備えている。駆動部は、読み出し信号SOを出力する差動アンプAmpと、定電流負荷と、記憶素子21に対して抵抗変化動作とダイレクトベリファイ動作とを実行する制御部30とを有している。制御部30は、ダイレクトベリファイ動作を行う期間では、定電流負荷が差動アンプAmpの負荷として機能すると共に、記憶素子21に流れる電流と定電流負荷の電流とに基づいて読み出し信号SOが出力されるように制御する。

(もっと読む)

半導体装置

【課題】不揮発型抵抗変化素子の低抵抗時の信頼性を向上させる。

【解決手段】少なくとも2つの論理回路15、16と、前段の論理回路15と後段の論理回路16との間を電気的に接続可能とする抵抗変化型不揮発素子14とを備え、抵抗変化型不揮発素子は、抵抗値が電気的に書き換え可能であり、抵抗値が高抵抗状態から低抵抗状態へ遷移するために必要な印加電圧もしくは電流の方向と、低抵抗状態から高抵抗状態へ遷移するために必要な印加電圧もしくは電流の方向とが逆の関係にあるような両極型の遷移特性を有し、前段の論理回路は、前段の論理回路から出力され抵抗変化型不揮発素子を介して流れる信号電流のピーク値が、抵抗変化型不揮発素子が低抵抗状態に遷移する方向に大きく逆方向に小さくなるような駆動能力を有するように構成される。

(もっと読む)

抵抗変化素子の駆動方法、不揮発性記憶装置、抵抗変化素子および多値記憶方法

【課題】多値の記憶状態を安定して読み書きできる抵抗変化素子の駆動法を提供する。

【解決手段】第1電極2を基準とする第2電極4の電位である電極間電圧を抵抗変化素子10に印加することによって第1電極2と第2電極4との間の抵抗値である電極間抵抗値を可逆的に変化させる抵抗変化素子10の駆動方法であって、Vα<Vβ<0およびVγ>0およびRL<RM<RHを満たすVα、Vβ、Vγ、RL、RM、RHについて、電極間電圧Vαの印加によって電極間抵抗値をRLにする書き込み過程と、書き込み過程の後、電極間電圧Vγの印加によって電極間抵抗値をRMにする第1の消去過程と、第1の消去過程の後、電極間電圧Vβの印加によって電極間抵抗値をRHにする第2の消去過程とを有する。

(もっと読む)

記憶装置およびその動作方法

【課題】長期的な信頼性を向上させることが可能な記憶装置およびその動作方法を提供する。

【解決手段】記憶装置1は、印加される電圧の極性に応じて可逆的に抵抗状態が変化する複数の記憶素子21と、駆動対象の記憶素子21の抵抗状態を、低抵抗状態と高抵抗状態との間で選択的に変化させる駆動部とを備えている。この駆動部は、低抵抗状態および高抵抗状態のうちの一方の抵抗状態から他方の抵抗状態へと変化させる第1の動作(セット動作またはリセット動作)を実行する際に、以下の段階的動作を行う。すなわち、第1の動作に関する強ストレス印加工程を実施した後に第2の動作に関する弱ストレス印加工程を実施するというステップを少なくとも1回以上繰り返して行った後、第1の動作に関する強ストレス印加工程を実施する。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ消去/書き込み時の電圧降下及びリーク電流を低減させた不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、列方向に延びる複数の列線、列方向に交差する行方向に延びる複数の行線、並びに、複数の列線及び行線の各交差部に配置された可変抵抗素子を含む複数のメモリセルを有するメモリセルアレイと、列線を介してメモリセルに対して可変抵抗素子の状態遷移に必要な電圧を供給する列線の第1端部及び第2端部の少なくとも一方に配置された列デコーダとを備え、列線は、第1部分、第1部分よりも列デコーダから遠い第2部分及び第2部分よりも列デコーダから遠い第3部分を有し、第2部分の行方向の線幅は、第1部分の行方向の線幅と同等又はより広く、且つ、第3部分の行方向の線幅よりも狭いことを特徴とする。

(もっと読む)

抵抗変化メモリのテスト装置、方法および抵抗変化メモリ装置

【課題】任意のテストサイクルにおけるサイクル時間を局所的に自由に調整するとともにチップサイズ、テストコストを削減する。

【解決手段】シフトレジスタ回路の出力と第1のライトイネーブル信号とに基づき、複数のシーケンスのうちの限界時間の確認を行うシーケンスに対応して信号変化する第2のライトイネーブル信号を発生し、第1および第2のライトイネーブル信号を用いて信号変化する時間間隔が局所的に前記第1のライトイネーブル信号の周期よりも短い複数のコア制御信号を発生し、発生した複数のコア制御信号を用いて抵抗変化メモリの動作確認を行う。

(もっと読む)

記憶装置

【課題】ライトディスターブの問題を解決し信頼性が高められた記憶装置を提供する。

【解決手段】相変化メモリセルに熱を印加してデータを書込むための電流を出力する電流印加回路と、メモリセルへのデータ書込時にメモリセルへの印加電圧を監視するモニタ回路と、第2の論理値を前記メモリセルに書込むサイクルにおいて印加電圧が所定範囲を超えたときに、モニタ回路の出力に応じて電流印加回路に電流の印加を停止させる制御回路とを備える。

(もっと読む)

記憶装置およびその動作方法

【課題】動作速度を向上させることが可能な記憶装置およびその動作方法を提供する。

【解決手段】一のワード線WLn上に位置するメモリセル20nn内の記憶素子21に対してセット動作を行うと共に、このワード線WLn上に位置するメモリセル20n(n+1)内の記憶素子21に対してリセット動作を行う際に、以下のように電圧の印加を行う。まず、ワード線WLnに対して所定のワード線電位Vwl_resetが印加されると共に、メモリセル20nn内の記憶素子21に対応する低電位側のビット線BL1nの電位が、メモリセル20n(n+1)内の記憶素子21に対応する低電位側のビット線BL2(n+1)の電位と比べて所定の電位差ΔVの分だけ高くなるように設定される。同一のワード線WLn上に位置する任意の(複数の)メモリセル20nn,20n(n+1)に対して、同時に(並行して)セット動作とリセット動作とを実行することができるようになる。

(もっと読む)

101 - 110 / 953

[ Back to top ]