国際特許分類[G11C13/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 11/00,23/00,または25/00に包含されない記憶素子の使用によって特徴づけられたデジタル記憶装置 (1,014)

国際特許分類[G11C13/00]の下位に属する分類

化学変化に基づく素子を用いるもの (16)

光学的素子を用いるもの (45)

国際特許分類[G11C13/00]に分類される特許

71 - 80 / 953

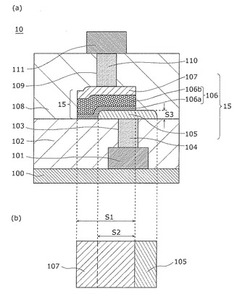

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

抵抗変化型メモリデバイスおよびその動作方法

【課題】低抵抗化動作の終了時に、逆向きの素子電流が流れディスターブが発生することを防止した抵抗変化型メモリデバイスを提供する。

【解決手段】印加電圧に応じて抵抗値が変化する可変抵抗素子Reの低抵抗化動作を、電圧ドライバ51が第2共通線(BLとSLの一方)の電位を変化させて開始し、低抵抗化動作中は可変抵抗素子Reに流れる素子電流を電流制御部52が第1共通線(BLとSLの他方)の側で制御する。低抵抗状態に遷移可能な期間の経過後に第1,第2共通線を、例えば短絡スイッチ54によって電位的にイコライズさせる。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

半導体記憶装置

【課題】ジュール熱を利用して情報を記憶する相変化メモリを採用した半導体記憶装置において、誤ライト動作を起こす可能性を抑制する。

【解決手段】本発明に係る半導体記憶装置は、積層体内のいずれかの半導体層に第1の電流を印加して積層体内の複数の半導体層の側面に配置されている抵抗変化材料層を一括して結晶化した後、第1の電流を印加した半導体層以外の半導体層に第2の電流を印加する。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

半導体装置

【課題】センス動作を高速化でき、誤リセットを防止できる半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、整流素子Diと可変抵抗素子VRとを有するメモリセルMCが配置されるメモリセルアレイMAと、前記メモリセルに電気的に接続される第1側の第1偶数,第1奇数ビット線(BLre,BLro)と第2側の第2偶数,第2奇数ビット線(BLle,BLlo)とを備える周辺回路と、前記周辺回路を介して前記メモリセルのセンスを行うセンスアンプ13と、前記メモリセルアレイと前記センスアンプの動作の制御を行う制御回路27とを具備する。前記制御回路17は、選択メモリセルに接続される前記第1側の第1偶数または第1奇数ビット線に、物理的に隣接する非選択の第2側の第2偶数および第2奇数ビット線のチャージシェアリングにより、選択ビット線である前記第1側の第1偶数または第1奇数ビット線電位を上昇させる。

(もっと読む)

半導体装置

【課題】可変抵抗素子を記憶素子として使用する半導体記憶装置において抵抗変化素子を高抵抗から低抵抗に遷移させるときに過剰な電流が流れることを防止する。

【解決手段】ビット線とワード線とを選択し対応する抵抗変化素子の抵抗値を高抵抗から

低抵抗に書き込む場合に、選択するワード線を非選択レベルの第1の電圧から第1の電圧と選択レベルの第2の電圧との間の電圧である第3の電圧へ遷移させ、対応する抵抗変化素子の抵抗値を高抵抗と低抵抗の中間段階の抵抗値に変化させる。しかる後に選択するワード線を第3の電圧から第2の電圧へ遷移させ、対応する抵抗変化素子の抵抗値を低抵抗に設定する。

(もっと読む)

半導体記憶装置

【課題】 連続して読み出しを行う際に発生する可能性のあるデータの誤りの検出、及び誤りデータの訂正を効率よく行うことのできる半導体記憶装置を実現する。

【解決手段】

金属酸化物を用いた可変抵抗素子を情報の記憶に用いる半導体記憶装置1における、ECCにより符号化されたデータの読み出しにおいて、ECC回路106によりデータの誤りが検出された場合、印加した読み出し電圧パルスと同一極性の書き換え電圧パルスの印加により生じる誤書き込みが発生したとみなして、誤りが検出された全てのメモリセルに対して、読み出し電圧パルスと逆極性の書き換え電圧パルスを印加し、誤りが検出されたビットを訂正する。

(もっと読む)

抵抗記憶装置およびその書き込み方法

【課題】 イオン伝導領域を備えた抵抗記憶装置において、誤書き込みが発生しやすくなるという課題を解決する抵抗記憶装置およびその書き込み方法を提供する。

【解決手段】 抵抗記憶装置およびその書き込み方法であって、第1の絶縁体と、第1の絶縁体を挟んで対向して形成された第1の端子と第2の端子と、第1の絶縁体内に存在し第1の絶縁体が第1の端子と向かい合う面、もしくは第1の絶縁体が第2の端子と向かい合う面とほぼ平行な方向に延在する線状もしくは面状で第1の絶縁体に比べイオンが移動しやすいイオン伝導容易領域と、第1の端子と第2の端子の対向部を挟んで配置された第3の端子とイオン源とを有することを特徴としている。また、その書き込み方法は、書き込み処理を、読み出し端子をフローティング状態にして行うことを特徴としている。

(もっと読む)

抵抗変化メモリ

【課題】抵抗変化素子の低抵抗状態の抵抗値のばらつきを防止する。

【解決手段】実施形態に係わる抵抗変化メモリのメモリセルは、直列接続される抵抗変化素子RW及び積層構造Cを備える。抵抗変化素子RWを第1の抵抗値からそれよりも低い第2の抵抗値に変化させる第1の動作において、メモリセルMCに第1の電圧パルスを印加する。第1の電圧パルスの振幅は、積層構造Cがキャパシタとして機能する第1の電圧領域内にあり、第1の電圧パルスは、Ron×C < T-lead < Roff×C、 Ron×C < T-trailを満たす。但し、T-leadは、第1の電圧パルスの立ち上がり時間[sec]であり、T-trailは、第1の電圧パルスの立ち下り時間[sec]であり、Roffは、第1の抵抗値[Ω]であり、Ronは、第2の抵抗値[Ω]であり、Cは、キャパシタの容量[F]である。

(もっと読む)

71 - 80 / 953

[ Back to top ]