国際特許分類[G11C13/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 11/00,23/00,または25/00に包含されない記憶素子の使用によって特徴づけられたデジタル記憶装置 (1,014)

国際特許分類[G11C13/00]の下位に属する分類

化学変化に基づく素子を用いるもの (16)

光学的素子を用いるもの (45)

国際特許分類[G11C13/00]に分類される特許

51 - 60 / 953

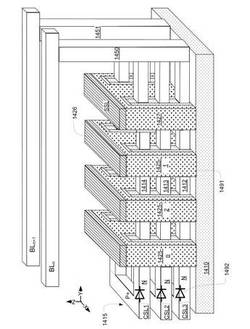

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】信頼性を確保しつつ、高速動作を実現することができる半導体装置を提供する。

【解決手段】抵抗変化素子10を有するメモリセル11と、メモリセル11に印加する電圧を制御する制御部80と、を備え、抵抗変化素子10は、第1の金属材料を含有する下部電極14と、第2の金属材料を含有する上部電極16と、酸素を含有する絶縁膜12と、を有しており、第1の金属材料は、第2の金属材料よりも規格化酸化物生成エネルギーが大きく、制御部80は、絶縁膜12の抵抗値を高抵抗化させる動作時および低抵抗化させる動作時において上部電極16に正電圧を印加し、絶縁膜12の抵抗値を読み出す動作時において下部電極14に正電圧を印加する。

(もっと読む)

再構成可能な論理装置

【課題】動作速度の改善された論理装置を提供する。

【解決手段】所定機能を行うために、入力信号に対する出力信号を生成する論理装置であって、入力信号に対する、可能なあらゆる出力結果を保存する複数の不揮発性メモリセルを備え、前記入力信号に基づいて不揮発性メモリセルのうち一つを選択し、アクセスすることで出力信号を生成することを特徴とする論理装置。

(もっと読む)

抵抗変化型不揮発性メモリ素子

【課題】遷移金属酸化物を用いた不揮発性メモリにおいて、メモリ抵抗の可逆的な変化を化学的変質によらない、メモリ抵抗変化の繰り返しに材料の劣化が起きにくい、メモリ抵抗変化の繰り返し特性に優れ、メモリ抵抗状態の安定した保持特性を有する抵抗変化型不揮発性メモリ素子を提供する。

【解決手段】抵抗変化型不揮発性メモリ素子として、第一電極2の金属Ptに、欠損があり導電性を有する強誘電酸化物Bi1-xFeO33を整流性接合し、さらに第二電極4にオーミック接合して、第一電極と第二電極の間に電圧を印加して、Bi1-xFeO3層に電気分極反転を起こして安定したメモリ抵抗変化を実現した。

(もっと読む)

相変化メモリセル及びそれを利用した相変化メモリデバイス

【課題】本発明は、相変化メモリセル及びそれを利用した相変化メモリデバイスに関するものである。

【解決手段】本発明の相変化メモリセルは、書き込み回路及び読み出し回路を含む。前記書き込み回路は、第一電極と、カーボンナノチューブ構造体と、第二電極と、を含む。前記第一電極、前記カーボンナノチューブ構造体及び前記第二電極は、相互に直列接続される。前記書き込み回路は、相変化メモリセルにデータを書き込む。前記読み出し回路は、第三電極と、相変化層と、第四電極と、を含む。前記第三電極、前記相変化層及び前記第四電極は、相互に直列接続される。少なくとも一部の前記相変化層及び少なくとも一部の前記カーボンナノチューブ構造体は、相互に積層して設置される。前記読み出し回路は、前記相変化メモリセルからデータを読み出す。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

不揮発性半導体記憶装置

【課題】大量データを高速に一括で保存することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】ビット線BL0〜BL3とワード線WL0〜WL3との間に接続され、低抵抗状態から高抵抗状態へ遷移するリセット動作と、リセット動作と異なる極性の電圧を印加することにより高抵抗状態から低抵抗状態へ遷移するセット動作が行われ、リセット動作時に流れるリセット電流がセット動作時に流れるセット電流よりも1桁以上低い可変抵抗素子VRを含むメモリセルMCを複数備えたメモリセルアレイを有する。さらに、メモリセルMCに対してリセット動作及びセット動作を行い、リセット動作を低抵抗状態である第1の複数のメモリセルのうち、選択の第1の配線に接続され、かつ選択の第2の配線に接続される第2の複数のメモリセルに対して一括して行う制御回路を有する。

(もっと読む)

半導体記憶装置

【課題】低電圧化を可能にする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に第1の配線と交差するように形成された第2の配線とを有するセルアレイ層を備え、メモリセルが極性の異なる電気信号が印加されることにより電気的書き換えが可能な可変抵抗素子及び可変抵抗素子に双方向の電流を流す電流制御素子を直列に接続してなる。電流制御素子は、i型半導体とその両側に接する第1及び第2導電型半導体とを有する。第2導電型半導体中の第2の不純物の拡散長は第1導電型半導体中の第1の不純物の拡散長より長く、第1導電型半導体とi型半導体との接合部に、第2導電型半導体とi型半導体との接合部よりも多くのインパクトイオンを発生させるインパクトイオン化促進部が形成される。

(もっと読む)

抵抗変化型メモリデバイスおよびその動作方法

【課題】ビット線側での素子電流による高い制御性を維持しながらも、低抵抗化動作の高速化を実現する抵抗変化型メモリデバイスを提供する。

【解決手段】ビット線BLに接続されて第1電流I1を流す初期電流駆動部55(N4)と、ビット線BLに対し初期電流駆動部55と並列に接続されて、第2電流I2を制御する素子電流制御部52とを有する。そして、初期電流駆動部55と素子電流制御部52の各NMOSトランジスタN4,N3を差動制御して、BL電流の値をI1からI2に切り替える。

(もっと読む)

相変化メモリのプログラミングのためのセットパルス

【課題】相変化メモリをプログラムするための単一パルスアルゴリズムを提供する。

【解決手段】相変化メモリ(PCM)セルを融解させるために第1の特定の信号値レベルで電子信号を印加させることと、前記PCMセルが融解した後、0ではない第2の特定の信号値レベルに到達するまで、印加されている前記電子信号の前記信号値レベルを低下させることと、を含み、前記信号値レベルは、前記第1の特定の信号値レベルと前記第2の特定の信号値レベルとの間で、信号値レベルの実質的に垂直な降下が起きないように低下する。

(もっと読む)

51 - 60 / 953

[ Back to top ]