国際特許分類[G11C13/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 11/00,23/00,または25/00に包含されない記憶素子の使用によって特徴づけられたデジタル記憶装置 (1,014)

国際特許分類[G11C13/00]の下位に属する分類

化学変化に基づく素子を用いるもの (16)

光学的素子を用いるもの (45)

国際特許分類[G11C13/00]に分類される特許

11 - 20 / 953

半導体記憶装置

【課題】半導体記憶装置のスイッチング耐久性の向上を図る。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

(もっと読む)

半導体記憶装置

【課題】データ書き込みエラー発生と消費電力を低減させた半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る半導体記憶装置は、第1極性の電圧パルス印加によってメモリセルに第1動作及び第2動作をさせるユニポーラ方式、並びに、第1極性とは異なる第2極性の電圧パルス印加によってメモリセルに第1動作をさせ且つ第1極性の電圧パルス印加によってメモリセルに第2動作をさせるバイポーラ方式の動作モードを有するデータ書き込み部と、メモリセルの第1動作の回数をカウントする第1動作回数カウント回路と、第1動作回数カウント回路を参照し、ユニポーラ方式による第1動作回数が第1規定回数に達した場合にデータ書き込み部の動作モードをバイポーラ方式に切り替える動作モード切り替え部とを備える。

(もっと読む)

半導体メモリ装置、このための連続プログラム制御回路及びプログラム方法

【課題】プログラム命令とデータを反復的に受信せずにデータを連続的にプログラムできる半導体メモリ装置と、このための連続プログラム制御回路及びプログラム方法を提供する。

【解決手段】本発明による半導体メモリ装置は、プログラミングイネーブル信号に応答して書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部、バッファープログラム命令またはバッファーオーバーライト命令を受信することによって、プログラムアドレス及びデータカウント信号に応答して連続プログラミングイネーブル信号を生成する連続プログラム制御回路及び連続プログラミングイネーブル信号に応答してプログラミングイネーブル信号を生成するコントローラを備える。

(もっと読む)

半導体メモリ装置、半導体メモリ装置のための分割プログラム制御回路及びプログラム方法

【課題】本発明の実施形態はメモリ領域を分割してプログラムできる半導体メモリ装置と、このための分割プログラム制御回路及びプログラム方法を提供することにある。

【解決手段】本発明による半導体メモリ装置はプログラミングイネーブル信号に応答して書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、プログラム完了信号に応答して既設定されたプログラム分割回数によって分割プログラミングイネーブル信号を生成する分割プログラム制御回路及び分割プログラミングイネーブル信号に応答して前記プログラミングイネーブル信号を生成するコントローラを含むことができる。

(もっと読む)

半導体装置

【課題】抵抗変化素子を備える半導体装置(半導体チップ)のチップ面積を削減すること。

【解決手段】半導体装置(1)は、半導体基板(50)上に形成されたトランジスタ(71)を含む下層回路(70)と、半導体基板(50)の上方の配線層(60)に形成されたメモリセルアレイ(20)と、を備える。メモリセルアレイ(20)の各メモリセル(MC)は、配線層(60)に形成された抵抗変化素子(40)を記憶素子として備る。メモリセルアレイ(20)は、メモリセル(MC)の直下に当該メモリセル(MC)との電気的接続用のビアが形成されていない第1領域(RF)を有している。下層回路(70)は、第1領域(RF)の少なくとも一部とオーバーラップするように配置されている。

(もっと読む)

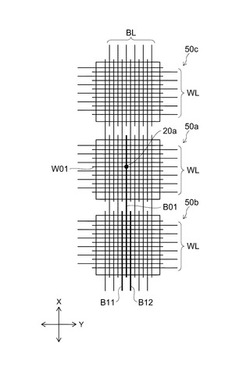

抵抗性メモリ装置、そのレイアウト構造及びセンシング回路

【課題】本発明は、レファレンスセルのライト回路を省略できる抵抗性メモリ装置及びそのレイアウト構造を提供する。また、本発明は、メインメモリセルのライト回路を利用してレファレンスセルを書き込むことができる抵抗性メモリ装置及びそのレイアウト構造を提供する。また、本発明は、レファレンスセルのライト回路を省略した抵抗性メモリ装置のためのセンシング回路を提供する。

【解決手段】複数のワードラインに連結されるメインメモリセルアレイ、及び複数のレファレンスワードラインに接続されるレファレンスセルアレイを有する複数のメモリ領域を具備し、前記複数のメモリ領域が、隣接メモリ領域とビットラインドライバー/シンカーを共有する抵抗性メモリ装置、そのレイアウト構造及びセンシング回路を提供する。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

可変抵抗素子を備える不揮発性メモリセル及び不揮発性半導体記憶装置

【課題】 検知マージンを大きくして可変抵抗素子の抵抗状態をより正しく検知することができ、且つ、面積低減によりコスト抑制を図ることができる不揮発性メモリセル及び不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極と第2電極の間に第1可変抵抗体R1を挟持してなる第1可変抵抗素子RD1と、第3電極と第4電極の間に第2可変抵抗体R2を挟持してなる第2可変抵抗素子RD2と、ドレイン端子が、第2電極と第4電極に、ゲート端子がワードラインに、ソース端子がコモンラインCLに夫々接続されたトランジスタTと、を備え、第1電極材料の仕事関数が第2電極材料の仕事関数より大きい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より小さい値に設定されるか、または、第1電極材料の仕事関数が第2電極材料の仕事関数より小さい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より大きい値に設定される。

(もっと読む)

不揮発性半導体記憶装置

【課題】セット動作・リセット動作時の可変抵抗素子の抵抗値のばらつきを抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1配線WL0〜WL2と、第2配線BL0〜BL2と、第1配線と第2配線との間に接続され可変抵抗素子を備えたメモリセルMC00〜MC22を配列してなるメモリセルアレイと、選択メモリセルに接続された選択第1配線WL1に第1電圧を印加するとともに、選択メモリセルに接続された選択第2配線BL1,BL2に第1電圧より電圧値の低い第2電圧を印加する電圧印加動作を行うように構成された制御回路とを備える。制御回路は、第2電圧の電圧値を複数の異なる電圧値から選択して、第2電圧を出力可能に構成されている。

(もっと読む)

半導体装置及びその制御方法

【課題】可変抵抗型メモリ素子を有する半導体装置におけるデータの読み出し動作の安定化

【解決手段】メモリセルに含まれる可変抵抗の状態が第1の高抵抗状態及び第1の低抵抗状態のいずれかになることによりデータを記憶するメモリセルMCを含み、メモリセルの抵抗値の大きさにより第1モードと第2モードとの2つの記憶モードをもつ半導体装置。データ読み出しの際は、第1モードの場合はビットラインの電位を基準電位より高い第1電位に昇圧し、第2モードの場合はビットラインの電位を第1電位より高い第2電位に昇圧し、ビットラインの電位を基準電位と比較することによりデータの読み出しを行う。

(もっと読む)

11 - 20 / 953

[ Back to top ]