国際特許分類[G11C17/14]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 一度だけプログラム可能なリードオンリメモリ;半永久的記憶装置,例.手でリプレースできる情報カード (379) | その記憶内容が,結合素子の状態を永久に変えることによって連結リンクを選択的に設定,切断または変更することにより決められるもの,例.PROM (188)

国際特許分類[G11C17/14]の下位に属する分類

電気的に溶断可能なリンクを用いるもの

周辺回路,例.メモリへの書込み用 (55)

国際特許分類[G11C17/14]に分類される特許

1 - 10 / 133

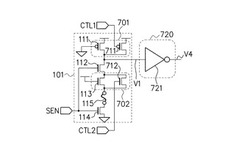

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

不揮発性メモリ及び不揮発性メモリからのデータ読み出し方法

【課題】2つのアンチヒューズ素子を備えるメモリセルから、電流検出によるデータの出力を可能にするセンスアンプを備えた不揮発性メモリが、望まれる。

【解決手段】不揮発性メモリは、一端が、第1の方向に配線された第1の制御線に接続された第1のアンチヒューズ素子と、一端が、第1の方向に配線された第2の制御線に接続され、他の一端が、第1のアンチヒューズ素子と共通接続された第2のアンチヒューズ素子と、第1及び第2のアンチヒューズ素子が共通接続された共通端子と、第1の方向に配線されたビット線との間に接続され、第1の方向と交差する第2の方向に配線されたワード線に印加される電圧により導通非導通が定まるスイッチトランジスタと、からなるメモリセルを複数含むメモリセルアレイと、第1及び第2のアンチヒューズ素子に流れる電流に基づいて、メモリセルに記憶されたデータを出力するセンスアンプと、を備えている。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の動作方法

【課題】光学的に書き込み状態が解析されることがなく、安価に実現することのできる、半導体記憶装置及びその動作方法を提供すること。

【解決手段】半導体記憶装置は、書込み処理が行われていない第1半導体記憶素子と、書込み処理が行われた第2半導体記憶素子とを具備する。前記第1半導体記憶素子及び前記第2半導体記憶素子は、それぞれ、不純物が注入された半導体層を備える抵抗部と、前記抵抗部に接続される、第1コンタクトと、前記抵抗部に接続される、第2コンタクトとを具備する。前記第1半導体記憶素子における前記半導体層の不純物の活性化率は、前記第2半導体記憶素子のそれとは異なっている。

(もっと読む)

書込回路、半導体集積回路、及び書込方法

【課題】アンチヒューズ型のOTPメモリへの書き込み時間を短縮化すること。

【解決手段】書込回路は、OTPマクロに対して書き込むデータを記憶する記憶部と、前記書き込むデータの書き込みを前記OTPマクロに実行させる第一の信号を印加し、前記OTPマクロが記憶しているデータの読み出しを前記OTPマクロに実行させる第二の信号を印加する制御部と、前記第二の信号に応じて前記OTPマクロから読み出されたデータと、前記記憶部が記憶するデータとを比較し、比較結果を出力する比較部とを有し、前記制御部は、前記比較結果が一致を示す場合、前記書き込むデータに関する処理を終了し、前記比較結果が不一致を示す場合、前記第一の信号及び前記第二の信号の印加を再度行う。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

1 - 10 / 133

[ Back to top ]