国際特許分類[G11C19/00]の内容

国際特許分類[G11C19/00]の下位に属する分類

磁気素子を用いるもの (1)

共振回路中の非線型誘導素子を用いるもの

能動素子,例.放電管,半導体素子,と結合した磁気素子を用いるもの (1)

ステージの主素子としてキャパシタを用いるもの

放電管を用いるもの

半導体素子を用いるもの (202)

オプト―エレクトロニクス装置,すなわち電気的または光学的に結合された光放射および光―電気装置を用いるもの

超電導素子を用いるもの

3以上の異なる安定状態を有する記憶素子を用いるもの,例.電圧によるもの,電流によるもの,位相によるもの,周波数によるもの

二次元の,例.水平方向と垂直方向に情報が移動するシフト・レジスター

国際特許分類[G11C19/00]に分類される特許

181 - 190 / 283

シフトレジスタ回路およびそれを備える画像表示装置

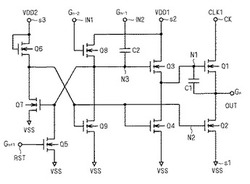

【課題】シフトレジスタ回路において、動作の高速化に伴う駆動能力の低下を抑制する。

【解決手段】シフトレジスタ回路は、出力端子OUTとクロック端子CKとの間のトランジスタQ1、出力端子OUTと第1電源端子s1との間のトランジスタQ2、トランジスタQ1のゲートと第2電源端子s2との間のトランジスタQ3を備える。そして、第1入力端子IN1に入力される信号に基づいて、トランジスタQ3のゲートノードを充電するトランジスタQ8と、第2入力端子IN2に入力される信号に基づいて、充電されたトランジスタQ3のゲートノードを昇圧する容量素子C2とを備える。

(もっと読む)

シフトレジスタ回路およびそれを備える画像表示装置

【課題】消費電力の上昇を抑制しつつ、シフトレジスタ回路の誤動作を防止して動作信頼性を向上させる。

【解決手段】単位シフトレジスタ回路SRは、出力端子OUTに低電位側電源電位VSSを供給する2つのトランジスタQ2A,Q2Bを有している。第1制御端子CTAおよび第2制御端子CTBにはそれぞれ、互いに相補な第1制御信号VFRおよび第2制御信号/VFRが入力される。トランジスタQ2Aと第1制御端子CTAとの間にはトランジスタQ8Aが接続し、トランジスタQ2Bと第2制御端子CTBとの間にはトランジスタQ8Bが接続し、当該トランジスタQ8A,Q8Bは、そのドレインがたすき掛けに互いのゲートに接続されている。

(もっと読む)

シフトレジスタ回路およびそれを備える画像表示装置

【課題】特殊な駆動制御装置を用いることなく、シフトレジスタ回路の誤動作を防止し動作信頼性を向上させる。

【解決手段】単位シフトレジスタ回路SRは、出力端子OUTとクロック端子CKとの間に接続するトランジスタQ1と、出力端子OUTと第1電源端子s1と間に接続するトランジスタQ2を備える。クロック端子CKとトランジスタQ2のゲートとの間には、MOS容量素子として機能するトランジスタQ8が設けられる。即ち、トランジスタQ2のゲートにはトランジスタQ8のゲートが接続し、クロック端子CKにはトランジスタQ8のソース・ドレインが接続する。

(もっと読む)

デュアルパスマルチモード順次記憶素子

本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。  (もっと読む)

(もっと読む)

二つのクロック信号を用いたイメージ表示システム

【課題】イメージ表示システムを提供する。

【解決手段】本システムは、コントローラー210と信号駆動回路200とで構成される。コントローラー210はクロック信号CLK1とCLK2、及び、スタートパルスSTPを信号駆動回路200に提供する。信号駆動回路200は直列され、第一クロック信号CLK1と第二クロック信号CLK2だけにより制御される複数のシフトレジスタ20−1、20−2、20−3、20−4からなり、スタートパルスSTPを受信後、対応する駆動パルスout1、out2、out3、out4を順に出力する。

(もっと読む)

シフトレジスタ回路及びこれを用いた固体撮像装置

【課題】通常読み出し用のクロックと高速読み飛ばし用の高周波数のクロックを別個に用意する必要をなくし、クロックに関する構成を簡単にする。

【解決手段】垂直シフトレジスタ回路14は、縦続接続された9段の単位回路70を備える。各段の単位回路70は、クロック信号に従うシフト動作によって信号伝達を行う第1の動作モードと、前記クロック信号とは無関係に直ちに信号伝達を行う第2の動作モードとを、選択的に行い得るように構成される。9段の単位回路70は、3つのブロックBV1〜BV3に分けられる。ブロックBV1〜BV3に対して1対1に設けられた個別切替設定部S1〜S3は、対応するブロックの各段の単位回路70が行う動作モードを、他のブロックから独立して、制御信号CONV1〜3にそれぞれ応じて前記第1及び第2の動作モードのいずれかに切り替えて設定する。

(もっと読む)

シフトレジスタ回路およびそれを備える画像表示装置

【課題】シフトレジスタ回路の誤動作を防止し、動作信頼性を向上させる。

【解決手段】シフトレジスタ回路は、出力端子OUTと第1クロック端子Aとの間のトランジスタQ1と、出力端子OUTと第1電源端子s1との間のトランジスタQ2と、トランジスタQ1のゲートが接続するノードN1を入力端としトランジスタQ2のゲートが接続するノードN2を出力端とするインバータとを備える。当該インバータは、ノードN2と第1電源端子s1との間に直列に接続し、ノードN1に接続したゲートをそれぞれ有するトランジスタQ7A,Q7Bと、ノードN2と第3電源端子s3との間に接続し、当第3電源端子s3に接続したゲートを有するトランジスタQ6と、トランジスタQ7AとトランジスタQ7Bとの接続ノードである第3ノードと第4電源端子s4との間に接続し、ノードN2に接続したゲートを有するトランジスタQ8とを備える。

(もっと読む)

半導体装置、並びに当該半導体装置を具備する表示装置及び電子機器

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフトレジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制できる。

(もっと読む)

シフトレジスタ回路、及び表示駆動装置

【課題】信号の出力と次段への転送を司るトランジスタの特性の変動を抑制して、より長寿命なシフトレジスタ回路及びこれを備える表示駆動装置を提供すること。

【解決手段】縦続接続された複数の信号保持部を備えたシフトレジスタ回路の各信号保持部FFPnは、ドレイン電極が出力用クロック信号CKが供給される第1のクロック入力端子に接続され、ソース電極が出力信号を取り出す出力端子OUTに接続された第1のMOSトランジスタT1を備え、第1の入力端子に印加される前段の信号保持部の出力信号がハイレベルとなった後に、第2のクロック入力端子に供給される、上記出力用クロック信号CKとは位相が異なるT1駆動用クロック信号CK’の立ち上がり時点から、第2の入力端子に印加される後段の信号保持部の出力信号が立ち上がるまでの間、第1のMOSトランジスタT1がオン状態とされる。

(もっと読む)

シフトレジスタ

【課題】ステージ間の配線を複雑にすることなく各ステージをオフできるシフトレジスタを提供する。

【解決手段】シフトレジスタの各ステージSAは、イネーブル回路1と、ディスエーブル回路2とを備えている。このディスエーブル回路2は、イネーブル回路1に制御信号が入力されてイネーブル回路1から次の制御信号が出力されるまでの間以外は、シフトレジスタの外部からディスエーブル回路2に高電圧が供給されることにより、イネーブル回路1をオフにするように構成されている。

(もっと読む)

181 - 190 / 283

[ Back to top ]