国際特許分類[G11C27/02]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 電気的アナログ記憶装置,例.瞬時値を記憶するためのもの (56) | 抽出・保持装置 (39)

国際特許分類[G11C27/02]に分類される特許

1 - 10 / 39

サンプルアンドホールド回路

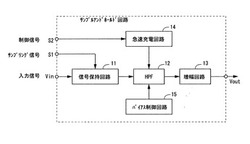

【課題】ハイパスフィルタ回路を急速充電できるようにして、その起動時間を短くする。

【解決手段】所定のタイミング毎に入力信号を保持する信号保持回路11と、信号保持回路11の出力側に接続された第1のトランジスタQ1の出力側の第1のノードN1に現れる信号から低域成分を除去するハイパスフィルタ回路12と、起動時にのみ動作してハイパスフィルタ回路12のコンデンサC2に対して急速充電を行う急速充電回路14と、ハイパスフィルタ回路12の出力側に接続された増幅回路13と、急速充電回路14による急速充電動作の終了から通常動作に移行する前後で前記第1のノードN1のバイアス電位をほぼ一定に保持するバイアス制御回路15とを備える。

(もっと読む)

サンプルホールド回路

【課題】サンプルホールド機能とマルチプレクサ機能とを具備したサンプルホールド回路を互いに位相が反転した2相信号のみでサンプルホールド機能とマルチプレクサ機能とを提供する。

【解決手段】2つのサンプルホールド回路10,11は、非反転入力端が基準電位に接続された差動増幅器A1,A2と、制御信号φ1に従ってオンオフするスイッチ及びサンプリング容量C1,C3と、制御信号φ1に従ってオンオフするスイッチ及びホールド容量C2,C4と、制御信号φ2に従ってオンオフするスイッチと、を備える。マルチプレクサ回路12は、非反転入力端が基準電位に接続された差動増幅器A3と、制御信号φ1,φ2に従ってオンオフするスイッチと、差動増幅器A3の出力端と反転入力端との間に接続されたホールド容量C5と、を備える。

(もっと読む)

サンプルホールド回路及びAD変換器

【課題】アナログ信号に含まれているサンプルホールド動作周期と同じ周期の周期性ノイズや、サンプルホールド動作周期の逓倍の周期の周期性ノイズ等に起因する影響を抑えて信号処理することのできるサンプルホールド回路及びAD変換器を提供する。

【解決手段】入力されたアナログ信号をサンプルホールドするための第1のサンプルホールド回路部23と、第2のサンプルホールド回路部24との2つのサンプルホールド回路部を備えている。第1のパルス信号生成回路部21は、各サンプルホールド動作周期TSHにおいて、任意のタイミングで第1のサンプルホールド回路部23によりアナログ信号AINがサンプルホールドされると共に、その任意のタイミングを変化させて、第1のパルス信号S1を生成する。これにより、サンプルホールド回路20から出力されたアナログ信号ASHに、なるべく周期性ノイズの同じオフセット成分を付加されないようにする。

(もっと読む)

サンプル・ホールド回路、回路装置、A/D変換回路及び電子機器

【課題】チャージインジェクションによる信号誤差を抑制できるサンプル・ホールド回路、回路装置、A/D変換回路及び電子機器を提供すること。

【解決手段】サンプル・ホールド回路は、一端が第1のノードN1に接続されるサンプリング用キャパシターCsと、第1のノードN1と第2のノードN2の間に設けられるメイントランジスターTMと、メイントランジスターTMと並列に設けられるサブトランジスターTSと、を含む。サブトランジスターTSのゲート面積は、メイントランジスターTMのゲート面積よりも小さい。サンプリング期間からホールド期間への切り替わりにおいて、メイントランジスターTMがオフになった後にサブトランジスターTSがオフになる。

(もっと読む)

サンプルホールド回路

【課題】S/N比を向上させたサンプルホールド回路を提供すること。

【解決手段】入力電圧を入力する入力端子と、入力電圧に基づいたサンプリング電圧をホールドする複数の容量と、入力端子と記複数の容量との間に夫々接続された複数の入力スイッチと、複数の容量のホールド電圧を出力する出力端子と、を備え、複数の容量は、複数の入力スイッチによって異なるタイミングで入力電圧をサンプリングし、複数の容量のホールド電圧の平均化処理を行って出力端子に出力する、構成とした。

(もっと読む)

サンプルアンドホールド回路

【課題】製造ばらつきや、温度変化により、ローパスフィルタの特性ばらつきや特性変動が発生するという課題があった。また、低い周波数ノイズ除去で回路チップが大きくなるという課題があった。これら課題を解決するサンプルアンドホールド回路を提供する。

【解決手段】本発明のサンプルアンドホールド回路は、外部電気信号が入力されるための信号入力端子と、内部電気信号を出力するための信号出力端子と、外部電気信号に起因する電荷を蓄積するよう信号入力端子に接続された第1の電荷蓄積手段と、第1の電荷蓄積手段に接続され、電荷を第1の電荷蓄積手段との容量の比に応じて分配蓄積可能とする第2の電荷蓄積手段と、第1の電荷蓄積手段に電荷を蓄積することと、電荷の分配蓄積ならびにこれに起因する内部電気信号を信号出力端子に出力することとを切り替え制御する制御手段とを有する。

(もっと読む)

サンプルホールド回路

【課題】CMOSインバータにより反転増幅回路を構成したサンプルホールド回路では、出力信号のオフセット電位が変動しやすい。

【解決手段】サンプルホールド回路2の出力段に設けられるCMOSインバータ回路14は、それぞれのゲートに共通の信号を入力されるPMOSトランジスタMP1及びNMOSトランジスタMN1と、MP1と正電圧源VCCとの間にダイオード接続されたNMOSトランジスタMN2と、MN1と接地電位GNDとの間にダイオード接続されたPMOSトランジスタMP2とを備える。

(もっと読む)

ホールド回路

【課題】ホールド動作時の出力電圧の変動を抑制することができるホールド回路を提供する。

【解決方法】ホールド回路100は、ホールドコンデンサ140、オペアンプ110、第1pMOS130、バッファアンプ150、電圧調整回路120を備える。オペアンプ110の非反転入力端には入力信号の電圧が印加され、反転入力端にはホールドコンデンサ140の電圧が印加される。ゲートGとドレインDが接続している第1pMOS130は、ソースSからドレインDへ電流を通す整流素子として機能する。整流素子の入力端はオペアンプ出力端に接続しており、出力端はホールドコンデンサ他端に接続している。電圧調整回路120は、オペアンプ出力端と整流素子入力端の間に接続されており、オペアンプ出力端の電圧がバッファアンプ出力端の電圧よりも低い場合に、整流素子入力端の電圧をオペアンプ出力端の電圧よりも高くする。

(もっと読む)

ホールド回路

【課題】ホールド動作時に出力電圧の経時的ドリフトを抑制することができるホールド回路を提供する。

【解決方法】ホールド回路100は、入力端子106と、出力端子114と、スイッチング用MOSトランジスタ108と、ホールドコンデンサ112とバッファアンプ109を備えている。ホールドコンデンサ112は、入力端子から流れ込む電荷を蓄える。スイッチング用MOSトランジスタ108は、入力端子とホールドコンデンサ112の間の導通と遮断を切り替える。バッファアンプ109は、ホールドコンデンサと出力端子の間に介在している。バッファアンプ109は、非反転入力端がホールドコンデンサ112に接続されているとともに反転入力端が出力端に接続されているチョッパアンプ110で構成されている。チョッパアンプ110の出力端がスイッチング用MOSトランジスタ108のバックゲートに接続されている。

(もっと読む)

トラック・ホールド回路

【課題】トラックモードからホールドモードへの遷移時に生じる電圧誤差を低減可能なトラック・ホールド回路を提供する。

【解決手段】入力された差動入力信号を負荷抵抗RL1、RL2、トランジスタ対Q1,Q2からなる第1の差動増幅回路にて増幅して出力する入力バッファ1を、トラックモード時はホールドコンデンサCH1,CH2と接続し、ホールドモード時は切り離すスイッチ回路3を備え、かつ、フィードスルー減衰回路2として、ホールドモード時に負荷抵抗RL1、RL2それぞれに電流を供給するトランジスタ対Q13,Q14、トランジスタ対Q15,Q16それぞれからなる第2、第3の差動増幅回路、前記差動入力信号により該第2、第3の差動増幅回路に流れる電流を制御するトランジスタ対Q17,Q18からなる第4の差動増幅回路を備え、かつ、該第2、第3の差動増幅回路を構成する各トランジスタ対のエミッタにエミッタ接続抵抗を接続する。

(もっと読む)

1 - 10 / 39

[ Back to top ]