国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

1,101 - 1,110 / 6,637

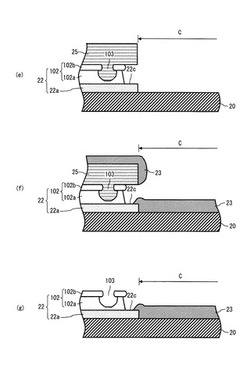

パターン形成方法、及び半導体装置の製造方法

【課題】下地の性能を犠牲にすることなく、リフトオフ層が下地から剥離することを防止できるパターン形成方法、及び半導体装置の製造方法を提供すること。

【解決手段】本発明にかかるパターン形成方法は、基板上にカバー絶縁膜22を形成し、第1のレジストパターン104をマスクとして、金属膜パターン形成領域を取り囲むようカバー絶縁膜22に凹部103を形成する工程と、凹部103内に入り込むよう、カバー絶縁膜22上にリフトオフ層となる第2のレジストパターン25を形成する工程と、第2のレジストパターン25をマスクとして、金属膜パターン形成領域のカバー絶縁膜22に開口部を形成する工程と、第2のレジストパターン25の上から基板表面に金属膜を成膜し、第2のレジストパターン25とともに第2のレジストパターン25上の金属膜を除去して金属膜パターンを形成する工程とを備えるものである。

(もっと読む)

ウエハレベルCSPの製造方法

【課題】 ウエハレベルで組立て可能な薄型CSPを提供する。

【解決手段】 ウエハ裏面側に、スクライブライン上の特定箇所に形成したスルーホールの側面を利用して,ウエハ表裏間の電気接合を取り、基板実装用の電極を配置する。そしてスルーホールは半導体基板のスクライブライン上をハーフエッチングした凹部を、バックグラインドを用いて裏面研磨することで形成する。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】研磨時にバリア膜が溶解することを抑制することができるような半導体装置及びその製造装置を提供する。

【解決手段】半導体基板上に形成された、溝109を有する絶縁膜107と、溝109に形成された第1のバリア膜111と第2のバリア膜112とを有する配線115とを備えている。第1のバリア膜111は、溝109の側壁及び底面上に形成され、第2のバリア膜112は、第1のバリア膜111を覆うように溝109に形成されている。さらに、第2のバリア膜112は、配線115の上面よりも下側に形成されている。

(もっと読む)

半導体ウエハ、半導体ウエハの製造方法、および半導体装置

【課題】ヒューズ素子形成領域の配線を露出させることなく、クラックストップトレンチとボンディングパッド開口部を同時に形成する半導体ウエハ及びその製造方法を提供する。

【解決手段】半導体基板と多層配線構造とを少なくとも具備してなり、前記多層配線構造がチップ領域Aとヒューズ素子形成領域Bおよびダイシング領域Cとに渡って形成されてなる半導体ウエハにおいて、前記チップ領域に位置する前記多層配線構造上には、前記配線で構成されたボンディングパッド170が形成される一方、前記ダイシング領域には、前記多層配線構造が一部除去されることによって形成された二本以上が並行して並ぶダミーリングおよび、前記ダミーリング間に形成された、クラックストップトレンチ152となる溝部が設けられていることを特徴とする半導体ウエハを採用する。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体装置

【課題】ダイシングブレードでダイシングする際の層間絶縁膜間の密着性を良好にしつつ、層間絶縁膜の層間クラックを防ぐ。

【解決手段】スクライブライン領域202において、ダイシング工程においてダイシングブレードが通るブレード領域204およびブレード領域204の両側に形成され、ダイシングブレードが通らない非ブレード領域206にそれぞれダミー配線が形成され、非ブレード領域206においては上下に隣接するダミー配線106bとダミー配線110bとがダミービア108bで接続され、ブレード領域204においては、上下に隣接するダミー配線106aとダミー配線110aとがダミービアで接続されていない。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合に、更に低コンタクト抵抗を確保することができる表示装置用Al合金膜を提供する。

【解決手段】本発明のAl合金膜は、表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Ni:0.2〜1.0原子%、Cu:0.2〜0.8原子%およびTiを0.05〜0.5原子%含有するものであるところに特徴を有する。

(もっと読む)

転写体および電極形成方法

【課題】簡便な製造プロセスにより、被転写体である水晶基板の特性に影響を与えることなく、電極となる導電性膜を水晶基板へ形成することが可能な転写体を提供する。

【解決手段】転写体10は、基材11と、基材11の表面に形成され所定の形状にパターニング加工されて電極4となるべき導電性膜である金属膜14と、少なくとも金属膜14となる導電性膜の部分を覆うように形成されエネルギーを付与されると接着性を発現することが可能な接合膜3と、を備えている。このような構成の転写体10は、導電性膜14および接合膜3の形成された側が被転写体へ押し付けられると、接合膜3の膜面が被転写体へ接合する。そして、基材11を被転写体から離反する方向へ引き離すと、接合膜3が被転写体と強固に接合しているため、導電性膜14は、基材11から剥離し、接合膜3を介して被転写体へ転写される。

(もっと読む)

絶縁性外郭部と、該外郭部内に位置しかつ該外郭部から分離された導電性領域と、で構成されたTSV相互接続構造体の製造

【課題】本発明は、相互接続構造体の製造方法に関する。

【解決手段】本発明の相互接続構造体の製造方法は、基板(100)内における、閉じた外郭部を形成する少なくとも一つのトレンチ(103,105)及び前記閉じた外郭部の内側に位置する少なくとも一つのホール(102,104)の形成を含み、トレンチ及びホールが、基板の領域によって分離され、また、本方法は、トレンチを誘電性材料(111)で充填するステップと、ホールを導電性材料(117,122)で充填するステップと、を含む。

(もっと読む)

1,101 - 1,110 / 6,637

[ Back to top ]