国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

1,071 - 1,080 / 6,637

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

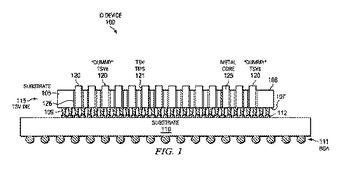

ICデバイスのエンハンストされた熱放散のための突出するTSV

集積回路デバイス(100)が、基板パッド(102)を含む上面を有する基板(110)、及び能動回路を含む上部半導体表面(107)と(底面)106とを含む半導体基板(105)を含む複数の基板貫通ビア(115)ダイを含む。上部半導体表面(107)は、基板の上面上の基板パッドに結合されるボンドコネクタ109を含む。複数の基板貫通ビア(TSV)が、底面から外に延びる突出するTSVティップ(121)に上側半導体表面から延びる内部金属コア(125)を含む。複数のTSVの少なくとも1つが、そこへの如何なる電気的接続もない、突出するTSVティップを有し、TSVダイの底面からの熱消散を可能にするための付加的な表面領域を提供するダミーTSV(120)である。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置を3次元実装するため、狭ピッチ、微小径、高アスペクト比の開孔に空隙を形成することなく導電性材料を埋め込み、低コストで貫通電極を形成する。

【解決手段】 半導体基板10上の絶縁膜層11、パッド電極12が形成された面に導電性の接着剤層13を用いて導電性のサポート基板14を貼り合わせする。この状態で半導体基板10の裏面を研磨して薄化した後、開孔15を形成する。さらにサポート基板14、接着剤層13を通じて複数のパッド電極12に同時に同電位を与え、ボトムアップ成長のメッキ法で開孔15に銅を埋め込み、Cuプラグ16、Cuポスト17からなる貫通電極を形成する。このようにすると開孔15のアスペクト比が極端に高くならないので銅が良好に埋め込まれ、また半導体基板10の表裏反転を伴う工程処理回数が低減できる。

(もっと読む)

半導体装置製造方法及び積層半導体装置

【課題】複数の基板を貼り合わせる積層半導体装置を効率よく製造できる方法を提供する。

【解決手段】複数の基板を貼り合わせて積層半導体装置を製造する半導体装置製造方法であって、回路が形成された複数の基板のうちの一の基板に凹部を形成する凹部形成ステップと、一の基板を複数の基板のうちの他の基板に重ね合わせる重ね合わせステップと、重ね合わせステップの後に、一の基板の凹部に導電性材料を導入することにより、一の基板の回路と他の基板の回路との間の電気的な導通路を形成する導通形成ステップとを備える半導体装置製造方法が提供される。

(もっと読む)

パターン形成方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等のパターンを作製する方法、さらには、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜、良好なマスクパターン、及びコンタクトホールを形成する方法を提案し、更には低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】本発明の一は、膜上にぬれ性の低い1のマスクパターンを形成した後、第1のマスクパターンを介して、膜上にぬれ性の高い材料を塗布又は吐出して第2のマスクパターンを形成し、第1のマスクパターンを除去して、第2のマスクパターンをマスクとして第1の膜の一部を除去する。

(もっと読む)

半導体装置

【課題】多層配線構造において、測定パッドとバンプ等形成用の外部接続パッドの構造をそれぞれの用途に合わせて最適化する。

【解決手段】半導体装置100は、測定パッド2と外部接続パッド3を有している。測定パッド2は、その周端部に沿って20個のビアコンタクトが配置され、当該ビアコンタクトが形成されていない平坦な中央部を有し、当該中央部は、測定用のプローブ針が接触されるプローブ針接触領域2Aになっている。外部接続パッド3は、9個のビアコンタクトが配置され、当該ビアコンタクトが配置されることにより凹凸のある領域を有し、当該領域は、外部接続媒体が形成される外部接続媒体形成領域3Aになっている。

(もっと読む)

半導体集積回路及びそのレイアウト方法

【課題】製造工程で生じるCMP後の膜厚ばらつき等の歩留まり低下要因を設計段階で取り除くことができる半導体集積回路及びそのレイアウト方法を提供する。

【解決手段】複数の機能回路毎にパターン面積率及びパターン周囲長率を抽出した後、当該抽出結果により規定される基準を用いて、複数の機能回路のそれぞれを第一の回路領域と第二の回路領域とに分別し、少なくとも一つ以上の第一の回路領域の周囲に第二の回路領域を配置する。第二の回路領域内に位置する任意の一点から所定の距離の範囲内には、少なくとも第一の回路領域の一部が含まれている。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備した半導体装置において、低コストで、半導体ウエハからEM保護の施されたダイを形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように形成される。この傾斜サイドウォール上、および、半導体ダイの底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIから保護する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

1,071 - 1,080 / 6,637

[ Back to top ]