国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

1,041 - 1,050 / 6,637

導体層の形成方法及び半導体装置の製造方法

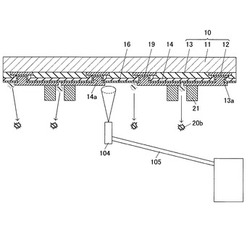

【課題】レジスト残滓を確実に除去する。

【解決手段】基板10上の一部にレジスト20を用いて導体層19をパターニングした後、レジスト20を剥離するレジスト剥離工程と、基板10の導体層19が形成された面に対して、第一ノズル103から第一噴射圧で溶剤を噴射することによりレジスト20の残滓20bをふやかし、第二ノズル104から第一噴射圧よりも高圧の第二噴射圧で溶剤を噴射することによりレジスト20の残滓20bを物理力で除去するレジスト残滓除去工程と、を備える導体層の形成方法である。

(もっと読む)

電子デバイスの製造方法

【課題】接合熱処理温度が低くて済み、凝固後は高い融点を確保し得る高耐熱性の電子デバイス及びその製造方法の提供。

【解決手段】複数枚の基板WF1〜WFrのそれぞれは、縦導体31と、接続導体4とを有している。複数枚の基板WF1〜WFrのうち、隣接する基板WF1、WF2は、一方の基板WF2の接続導体(縦導体)31が、他方の基板WF1の接続導体4と、接合膜5によって接合されている。接合膜5は、第1金属または合金成分と、それよりも融点の高い第2金属または合金成分とを含み、凝固後の溶融温度が第1金属または合金成分の融点よりも高くなっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】OBIRCH法を行う際に、特性チェック素子の特性を容易に測定することができる、半導体装置、及び半導体装置の製造方法を提供する。

【解決手段】レーザ光が照射されることにより特性が検査される、特性チェック素子と、前記特性チェック素子よりも上層に位置し、ダミーメタルが配置された、上部配線層とを具備する。前記上部配線層は、前記特性チェック素子に重なる第1領域と、前記特性チェック素子に重ならない第2領域とを備える。前記第1領域における前記ダミーメタルの密度は、前記第2領域における前記ダミーメタルの密度よりも、小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体基板、積層チップパッケージおよび半導体プレート並びにこれらの製造方法

【課題】積層チップパッケージの電気的な接続に関する信頼性を高める。

【解決手段】半導体基板はスクライブラインに沿って複数の溝部が形成されている。半導体基板は、複数の溝部のいずれか少なくとも一つに接する単位領域と、その単位領域内に一部が配置されている配線電極とを有している。そして、複数の溝部は、底部を含む溝下部よりも幅の広い幅広部が入り口に形成されている口広構造を有している。半導体基板は、幅広部が入り口の長さ方向全体に形成されていてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

半導体装置の積層構造体とその製造方法

【課題】継ぎ目無し貫通配線を有する三次元集積回路装置構造となる半導体装置の積層構造と、その製造方法を提供する。

【解決手段】半導体素子とこれに接続する配線群とを有してなる半導体基板11と、半導体基板11の厚さ方向に貫いて設けられた貫通電極6と、半導体基板11の表裏面のうちの一方の側に設けられた凹部と、凹部内に設けられて貫通電極6に電気的に接続する再配置配線7とを備え、貫通電極6と再配置配線7とのうちの一方を配線群のうちの少なくとも一部の配線に接続してなる半導体装置が、上下に複数積層されてなる半導体装置の積層構造体20である。第2半導体装置1Bの貫通電極6と、第1半導体装置1Aの再配置配線7とが連続して形成されている。第2半導体装置1Bの貫通電極6と第2半導体装置1Aの貫通電極6とが、平面視した状態で異なる位置に形成されている。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

1,041 - 1,050 / 6,637

[ Back to top ]